Fターム[5F045AF04]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 被成膜面が半導体であるもの (4,466) | III−V族(GaAs、GaP、InP、GaN等)面への成膜 (1,371)

Fターム[5F045AF04]の下位に属するFターム

3元以上の混晶(GaAlAs等)面への成膜 (282)

Fターム[5F045AF04]に分類される特許

1,081 - 1,089 / 1,089

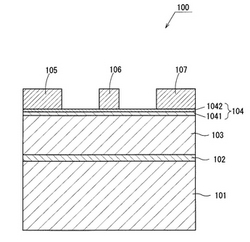

電界効果トランジスタ及びその製造方法

【課題】電極が形成される半導体層の表面平坦性や、シート抵抗などが何れも優れた、高性能化や小型化に好適な電界効果トランジスタを実現すること。

【解決手段】ノンドープのGaN結晶から成る半導体層103(バッファ層)の上には、厚さ約40nmのノンドープのAl0.2 Ga0.8 Nから成る半導体層104が積層されている。この半導体層104は、本発明に基づく厚さ約30nmの急峻界面提供層1041と、本発明に基づく厚さ約10nmの電極接続面提供層1042の計2層の半導体層から構成されている。これらは双方共に上記の通りノンドープのAl0.2 Ga0.8 Nから形成されているが、急峻界面提供層1041を結晶成長させる際には、キャリアガスとしてH2 を使用した。また、電極接続面提供層1042を結晶成長させる際には、キャリアガスとしてN2 を使用した。

(もっと読む)

半絶縁III族窒化物においてフェルミ準位を制御するための同時ドーピング

半絶縁III族窒化物層および半絶縁III族窒化物層の製造方法は、III族窒化物層を浅い準位のp型ドーパントでドーピングすること、およびIII族窒化物層を、例えば深い準位の遷移金属ドーパントなどの深い準位のドーパントでドーピングすることを有する。このような層および/または方法はまた、III族窒化物層をおよそ1×1017cm−3よりも小さい濃度を有する浅い準位のドーパントでドーピングすること、およびIII族窒化物層を深い準位の遷移金属ドーパントでドーピングすることを有する。深い準位のドーパントの濃度は、浅い準位のp型ドーパントの濃度よりも大きい。  (もっと読む)

(もっと読む)

枝を広げたナノウィスカーが形成されたナノ構造とその製造方法

第1ステージと第2ステージとを有する、ツリーの形態を持つナノ構造を形成する方法。第1ステージは、基板表面上に少なくとも1つの触媒粒子を供給し、かつ、各触媒粒子を介して第1ナノウィスカーを成長させる工程を含む。第2ステージは、各第1ナノウィスカーの周囲に、1つ以上の第2触媒粒子を供給し、各第1ナノウィスカーの周囲から横方向に伸びる第2ナノウィスカーを成長させる工程を含む。更なるステージは、以前のステージのナノウィスカーから伸びる1つ以上のさらなるナノウィスカーを成長させる工程を含み得る。ヘテロ構造は、ナノウィスカー中に形成され得る。このようなナノ構造は、太陽電池アレイまたは光放出フラットパネルのコンポーネントを形成し得る。その構造において、ナノウィスカーは光電性材料から形成される。神経ネットワークは、複数の第1ナノウィスカーを近くに一緒に配置し、連続するステージで成長したナノウィスカーを通して隣接するツリーが互いに接触し、ナノウィスカー内のヘテロ結合が電流の流れに対してトンネル障壁を形成するようにすることによって、形成され得る。  (もっと読む)

(もっと読む)

高品質ホモエピタキシ用微傾斜窒化ガリウム基板

【数1】

方向または

【数2】

方向に主に向かう<0001>方向から、約0.2〜約10度の範囲のオフカット角度でオフカットされた(0001)表面を含むIII−V族窒化物、例えばGaN基板。表面が50×50μm2AFM走査により測定された1nm未満のRMS粗さと、3E6cm−2未満の転位密度とを有する。この基板は相当するブールまたはウェハブランクのオフカットスライスにより、オフカットラッピングまたは相当する微傾斜へテロエピタキシャル基板、例えばオフカットサファイア上の基板本体の成長により形成することができる。この基板はIII−V族窒化物系超小型電子および光電子デバイスの作製におけるホモエピタキシャル蒸着に有用に用いられる。  (もっと読む)

(もっと読む)

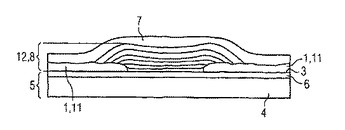

犠牲層上のヘテロエピタキシによるIII族窒化物の自立基板の実現方法

本発明は、III族窒化物の自立基板の作製に関するものである。本発明は、より詳細には、エピタキシによって初期基板からIII族窒化物、とくに窒化ガリウム(GaN)の自立基板を実現する方法であって、III族窒化物のエピタキシ工程の際に自然に蒸発させるための犠牲層として、単結晶珪素ベースの中間層の蒸着を含むことを特徴とする方法を対象とする。この方法はとくに、平坦で直径が2”を超えるIII族窒化物自立基板を得ることを可能にする。 (もっと読む)

複数のオプトエレクトロニクス半導体チップの製造方法およびオプトエレクトロニクス半導体チップ

本発明は複数のオプトエレクトロニクス半導体チップの製造方法に関し、これらの半導体チップはそれぞれ少なくとも1つの半導体層を備えた複数の構造素子をそれぞれ有する。この方法においては基板ならびに成長表面を有するチップ結合体ベースが提供される。成長表面の上には複数の窓を有するマスク材料層が形成され、これらの窓の大部分は1μm以下の平均的な広がりを有する。マスク材料は後続のステップにおいて成長すべき半導体層の半導体材料がこのマスク材料上では実質的に成長しない、または成長表面に比べて実質的に成長しにくいように選択される。続けて、半導体層が実質的に窓の内部に位置する成長表面の領域の上に析出される。さらなるステップではチップ複合体ベースが被着された材料と共に半導体チップに個別化される。さらに本発明は本方法に応じて製造されるオプトエレクトロニクス半導体チップに関する。  (もっと読む)

(もっと読む)

エピタキシャル基板の製造方法

本発明は、エピタキシャル基板、例えば、GaN,SiGe,AlNまたはInNのエピタキシャル基板の製造方法、およびエピタキシャル基板上またはその中に作製された電子デバイスに関する。本発明の目的は、基板の影響を更に軽減することが可能であると同時に経済的に実行可能な、エピタキシャル基板の製造方法を提供することである。この目的は、以下のように達成することが出来る。すなわち、結晶性基板を用意し、原子種を基板に注入して脆性層を作成し、第1の温度で、基板の表面にエピタキシャル補強層を設け、第2の温度範囲で補強層を基板の副層とともに基板の残部から分離させて、これによって、この分離した材料によって、その上にホモエピタキシャル層またはヘテロエピタキシャル層の形成する擬似基板が作成される。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

1,081 - 1,089 / 1,089

[ Back to top ]