Fターム[5F045GH03]の内容

気相成長(金属層を除く) (114,827) | 機械加工プロセスとの組み合わせ (190) | 機械加工による前処理(膜形成が後) (70) | 研磨 (55) | 化学的機械研磨(CMP) (29)

Fターム[5F045GH03]に分類される特許

1 - 20 / 29

SiCエピタキシャルウェハ及びその製造方法

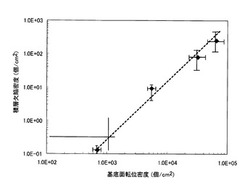

【課題】積層欠陥の面密度が低減されたSiCエピタキシャルウェハ及びその製造方法を提供する。

【解決手段】本発明のSiCエピタキシャルウェハの製造方法は、オフ角を有するSiC単結晶基板の成長面に存在する基底面転位(BPD)のうち、SiC単結晶基板上に形成された、所定膜厚のSiCエピタキシャル膜において積層欠陥になる比率を決定する工程と、比率に基づいて、使用するSiC単結晶基板の成長面におけるBPDの面密度の上限を決定する工程と、上限以下のSiC単結晶基板を用いて、比率を決定する工程において用いたエピタキシャル膜の成長条件と同じ条件で、SiC単結晶基板上にSiCエピタキシャル膜を形成する工程と、を有することを特徴とする。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】(0001)面に対して4°以下のオフ角θ1で傾斜したSi面が主面4とされたSiC基板2と、SiC基板2の主面4に形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、SiC基板2の主面4のオフ方向Dを、[11−20]軸方向および[01−10]軸方向に対して15°+/−10°の角度θ2で傾斜した方向にする。

(もっと読む)

III族金属窒化物の加工された非極性面を有する基板およびその製造方法

【課題】III族金属窒化物の非極性面を有する基板を研磨加工することで極めて平坦な表面を形成しつつ、かつその表面の加工歪みを取り除くことによって、III族金属窒化物の無歪研磨加工面を得ることである。

【解決手段】本方法は、III族金属窒化物の非極性面を有する基板を研磨加工し、前記非極性面の平均表面粗さ(Ra)を1nm以下とする研磨加工工程、次いで基板を不活性雰囲気下で熱処理する熱処理工程、および基板の非極性面を、ハロゲン含有ガスを用いて反応性ドライエッチングするか、または化学機械研磨加工する加工工程を有する。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

シリコンエピタキシャルウエーハの製造方法

【課題】所望の抵抗率のエピタキシャル層と従来より更に低抵抗率なシリコンウエーハからなり、素子の電気的特性の向上を実現できる、エピタキシャル成長中のオートドープを従来に比べて容易に抑制できるシリコンエピタキシャルウエーハの製造方法を提供する。

【解決手段】ボロンが1.0×1019atoms/cm3以上の濃度でドープされたシリコンエッチドウエーハを準備し、準備したシリコンエッチドウエーハの裏面側にCVD酸化膜を形成する工程を行い、その後、シリコンエッチドウエーハの表面に対して鏡面研磨を行って、表面側に回り込んだCVD酸化膜を除去する工程を行い、その後、温度1100℃以下のウェット酸化によって酸化膜を形成する工程を行い、そして、表面側の酸化膜をエッチングで除去する工程を行い、エッチング工程で酸化膜が除去された側の表面にエピタキシャル層を形成する。

(もっと読む)

炭化珪素単結晶基板、炭化珪素エピタキシャルウェハ、及び薄膜エピタキシャルウェハ

【課題】体積抵抗率が低く、しかも、エピタキシャル成長工程等のウエハプロセスにおいて炭化珪素単結晶基板が1000℃以上に晒されても、積層欠陥が殆ど発生することがない炭化珪素単結晶基板、および、この基板を用いて得た炭化珪素エピタキシャルウェハ、及び薄膜エピタキシャルウェハを提供する。

【解決手段】体積抵抗率が0.001Ωcm以上0.012Ωcm以下の炭化珪素単結晶基板であり、表裏面のうち少なくとも片面の表面粗さRaが1.0nm以下であると共に、外周側面の表面粗さRaが1.0nm以下である炭化珪素単結晶基板、および、前記炭化珪素単結晶基板上に炭化珪素薄膜をエピタキシャル成長してなる炭化珪素エピタキシャルウェハ、あるいは、窒化ガリウム、窒化アルミニウム、窒化インジウム又はこれらの混晶をエピタキシャル成長してなる薄膜エピタキシャルウェハ。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.9×10-3以下であり、主表面1sの面方位が、結晶基板の(0001)面または(000−1)面1cから<11−20>方向に10°以上81°以下で傾斜している。

(もっと読む)

窒化物半導体エピタキシャル層の形成方法および窒化物半導体デバイスの製造方法

【課題】窒化物半導体基板から窒化物半導体エピタキシャル層を分離する際に窒化物半導体エピタキシャル層に与えるダメージが低く高品質な窒化物半導体エピタキシャル層の形成方法を提供する。

【解決手段】本窒化物半導体エピタキシャル層の形成方法は、転位密度が1×107cm-2以下の窒化物半導体基板10上に、ガスおよび電解液の少なくともいずれかにより化学的に分解する化学的分解層20を介在させて、少なくとも1層の窒化物半導体エピタキシャル層30を成長させる工程と、窒化物半導体エピタキシャル層30を成長させる工程中およびこの工程後の少なくともいずれかにおいて、ガスおよび電解液の少なくともいずれかを用いて化学的分解層20を分解させることにより、窒化物半導体基板10から窒化物半導体エピタキシャル層30を分離する工程と、を備える。

(もっと読む)

III族窒化物半導体基板、エピタキシャル基板及び半導体デバイス

【課題】半導体デバイスの発光強度を向上させることが可能なIII族窒化物半導体基板、エピタキシャル基板及び半導体デバイスを提供する。

【解決手段】半導体デバイス100では、表面10aが特定の面方位を有した上で、S換算で30×1010個/cm2〜2000×1010個/cm2の硫化物、及び、O換算で2at%〜20at%の酸化物が表面層12に存在することにより、エピタキシャル層22とIII族窒化物半導体基板10との界面においてCがパイルアップすることを抑制できる。これにより、エピタキシャル層22とIII族窒化物半導体基板10との界面における高抵抗層の形成が抑制される。したがって、半導体デバイス100の発光強度を向上させることができる。

(もっと読む)

III族窒化物半導体基板、エピタキシャル基板及び半導体デバイス

【課題】半導体デバイスの発光強度を向上させることが可能なIII族窒化物半導体基板、エピタキシャル基板及び半導体デバイスを提供する。

【解決手段】半導体デバイス100では、表面10aが特定の面方位を有した上で、S換算で30×1010個/cm2〜2000×1010個/cm2の硫化物、及び、O換算で2at%〜20at%の酸化物が表面層12に存在することにより、エピタキシャル層22とIII族窒化物半導体基板10との界面においてCがパイルアップすることを抑制できる。これにより、エピタキシャル層22とIII族窒化物半導体基板10との界面における高抵抗層の形成が抑制される。したがって、半導体デバイス100の発光強度を向上させることができる。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】研磨工程の簡略化で生産性が高まり、コストダウンが可能で、鏡面研磨されたウェーハ表面に生じる加工起因のLPDの密度を低減し、ウェーハ表面の表面粗さを改善可能なエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】1次、2次研磨のみを行い仕上げ研磨を省略するので、シリコンウェーハの研磨が簡略化し、エピタキシャルシリコンウェーハの生産性が高まり、コストダウンが図れる。また、従来の砥粒を含む1次研磨のみを施した場合に比べて、ウェーハ表面に発生する加工起因のLPDの密度が低減し、ウェーハの表面粗さが小さくなる。さらに、砥粒で酸化膜を除去する1次研磨を行うので、砥粒が存在しない2次研磨時、アルカリ性水溶液による研磨レートが高まる。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】ヒ素ドープの低抵抗シリコンウェーハ上にエピタキシャル成長させる際に、簡易な方法で、積層欠陥の発生を防止することができるシリコンエピタキシャルウェーハの製造方法を提供することを目的とする。

【解決手段】シリコン単結晶をスライスして得られるシリコンウェーハ表面にエピタキシャル層を形成してシリコンエピタキシャルウェーハを製造する方法において、少なくとも、ヒ素をドープして抵抗率1.0〜1.7mΩcmにしたシリコン単結晶をスライスしてシリコンウェーハを得て、該シリコンウェーハを850〜1200℃で熱処理することでピットを発生させて、該熱処理したシリコンウェーハを鏡面研磨することで前記発生したピットを除去して、その後該鏡面研磨したシリコンウェーハ表面にエピタキシャル層を形成することを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】シリコンウェーハの鏡面研磨された表面に発生する加工起因のLPDの密度を低減し、かつウェーハ表面の表面粗さを小さくすることで、LPD密度が低く、表面粗さ品質に優れたエピタキシャル膜を有するエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】砥粒を含まず水溶性高分子を含むアルカリ性水溶液の研磨液を用いて、シリコンウェーハの表面を鏡面研磨する。水溶性高分子をアルカリ性水溶液に添加したので、摩擦係数を低下させ、鏡面研磨されたウェーハ表層部に発生する加工起因のLPDの密度を低減でき、LPD密度が低いエピタキシャルシリコンウェーハを製造できる。しかも、鏡面研磨されたウェーハ表面に発生する表面粗さを小さくでき、表面粗さ品質に優れたエピタキシャルシリコンウェーハを提供できる。

(もっと読む)

半導体ウェハの製造方法

【課題】半導体ウェハの裏面の定義されたかつ有利な特性を有する半導体ウェハを提供すること

【解決手段】a) シリコン棒をウェハに切断することにより半導体ウェハを準備する工程、b) 前記半導体ウェハのエッジを丸めることで、前記半導体ウェハは前面及び裏面が平坦な面とエッジ領域で丸められかつ傾斜する面とを有する工程、c) 前記半導体ウェハの前面及び裏面を研磨し、前記前面の研磨は、研磨パッド中に固定された砥粒を有していない研磨パッドを使用する化学機械的研磨を有し、前記半導体ウェハの裏面の研磨は、それぞれ研磨パッド中に結合された研磨材料を有する研磨パッドを使用してかつ前記半導体ウェハの裏面に研磨圧力を加える3つの工程で行い、第1の工程では、固体を有していない研磨剤を前記研磨パッドと前記半導体ウェハの裏面との間に導入し、第2及び第3の工程では研磨材料を有する研磨剤を導入し、第1の及び第2の工程の8〜15psiの研磨圧力を、第3の工程では0.5〜5psiに低下させる工程を有する半導体ウェハの製造方法

(もっと読む)

SiC単結晶基板の製造方法

【課題】SiC単結晶基板の活性層表面の中心線平均粗さが、0.1nm程度と、極めて平坦な表面を持つSiC単結晶基板の製造方法を提供する

【解決手段】活性層を有する複数のSiC単結晶基板を回転するテンプレート上に配置して前記活性層の表面を研磨するSiC単結晶基板の製造方法において、前記SiC単結晶基板が互いに直交する第1と第2のオリフラを持ち、前記第2のオリフラの中点と前記テンプレートの中心とを結ぶ線が前記中心から放射上になるように前記SiC単結晶基板を前記テンプレート上に配置するSiC単結晶基板の製造方法。

(もっと読む)

おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法

【課題】おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法。

【解決手段】本方法は、次の順序で工程:前記シリコン単結晶基板のおもて面及び裏面を同時に研磨する工程;応力補償層を前記シリコン単結晶基板の裏面上に堆積させる工程;前記シリコン単結晶基板のおもて面を研磨する工程;前記裏面上に堆積された応力補償層を有する前記シリコン単結晶基板を洗浄する工程;及びSiGeの完全に又は部分的に緩和された層を前記シリコン単結晶基板の前記おもて面上に堆積させる工程を含んでなる。

(もっと読む)

エピタキシャルウェハの製造方法、欠陥除去方法およびエピタキシャルウェハ

【課題】膜厚分布が均一なエピタキシャル膜を有するとともに、平坦度に優れたエピタキシャルウェハを簡単な工程で製造することのできるエピタキシャルウェハの製造方法およびエピタキシャルウェハを提供すること。

【解決手段】CZ法により得られたシリコン単結晶インゴットを薄円板状に切り出してウェハを得る(ステップS1)。次に、ウェハの表面を研削(ラッピング)して平面化する(ステップS2)。次に、エッチングによる化学研磨を行った(ステップS3)後、ウェハの両面を粗研磨する(ステップS4)。粗研磨終了後、気相エッチングを行い(ステップS5)、その後、エピタキシャル膜を形成する(ステップS6)。そして、エピタキシャル膜が形成されたウェハに対して仕上げ研磨を行い(ステップS7)、最終洗浄を行った(ステップS8)後、終了する。

(もっと読む)

化合物半導体基板及び半導体デバイス

【課題】 エピタキシャル層と基板との界面における電気抵抗の低減が図られた化合物半導体基板及び半導体デバイスを提供する。

【解決手段】 本発明に係る化合物半導体基板10は、III族窒化物で構成され、Cl換算で200×1010個/cm2以上12000×1010個/cm2以下の塩化物及びO換算で3.0at%以上15.0at%以下の酸化物を含む表面層12を表面に有する。発明者らは、鋭意研究の末、化合物半導体基板10の表面の表面層12に、Cl換算で200×1010個/cm2以上12000×1010個/cm2以下の塩化物及びO換算で3.0at%以上15.0at%以下の酸化物が含まれるときに、化合物半導体基板10とその上に形成されるエピタキシャル層14との間の界面のSiが低減され、その結果界面における電気抵抗が低減されることを新たに見出した。

(もっと読む)

半導体集積回路装置の製造方法

【課題】STIにおける酸化シリコン部材によるトレンチ埋め込み工程においては、一般に、HDP−CVDにより、成膜とスパッタ・エッチを同時的に進行させることで、酸化シリコン系の埋め込み絶縁膜の平坦化を計っている。しかしながら、65nmプロセス・ノード等の微細製品では、近接したトレンチを均一の埋め込むことが、ますます困難となっている。従って、近接したトレンチ配列部分をより均一に埋め込むことができる技術が待望されている。

【解決手段】本願発明は、近接したトレンチ配列部分をHDP−CVDによる酸化シリコン系の埋め込み絶縁膜によって埋め込む際に、成膜ステップとエッチング・ガスを含むガス雰囲気中でのエッチングを交互に繰り返すことによって、平坦な埋め込み特性を得ることができる。

(もっと読む)

1 - 20 / 29

[ Back to top ]