Fターム[5F048AB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | メモリ (1,087)

Fターム[5F048AB01]に分類される特許

1,081 - 1,087 / 1,087

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

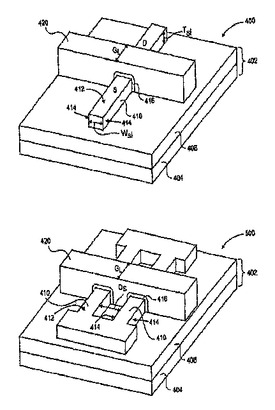

増大されたセル比を有する6トランジスタFINFET型CMOSスタティックRAMセル

本発明に係るCMOSスタティックRAMセルは、2つのアクセスデバイスであり、各々のアクセスデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのアクセスデバイス;2つのプルアップデバイスであり、各々のプルアップデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのプルアップデバイス;及び2つのプルダウンデバイスであり、各々のプルダウンデバイスが複数のフィンを有する3ゲートトランジスタから成るところの2つのプルダウンデバイスを有する。さらに、2つのフィンを有する3ゲートトランジスタを備えたCMOSスタティックRAMセルの製造方法が提供される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

半導体装置

【課題】 消費電力が小さく、かつ動作速度が速い半導体装置を提供する。

【解決手段】 DRAMコアセルのリードゲート1は、各々のゲートがそれぞれノードN1,N2を介してビット線BL,/BLに接続されるNチャネルMOSトランジスタ61,63と、各々のゲートがともに列選択信号CSLRを受けるNチャネルMOSトランジスタ2,3とを含み、MOSトランジスタ2,3のゲート酸化膜はMOSトランジスタ61,63のゲート酸化膜よりも薄い。したがって、列選択信号CSLRの振幅電圧の低電圧化を図ることができる。

(もっと読む)

1,081 - 1,087 / 1,087

[ Back to top ]