Fターム[5F048BB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378) | ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB03]に分類される特許

621 - 639 / 639

自動設計システム、自動設計方法及び半導体装置の製造方法

【課題】 電気的特性が均一なトランジスタを設計可能な自動設計システムを提供する。

【解決手段】 複数のトランジスタのレイアウトデータから複数のトランジスタのそれぞれの拡散領域の面積を計算する面積計算部101と、拡散領域のゲート長方向の寸法が最も小さいレイアウトデータを基準レイアウトデータとして定義する基準データ定義部102と、拡散領域のゲート長方向の寸法、面積、イオン注入条件及び熱処理条件に基づいて、実効チャネル長を予測する構造予測部201と、複数のトランジスタの総ての実効チャネル長と、基準レイアウトデータに基づく実効チャネル長との有意差がなくなるよう、複数のトランジスタのレイアウトデータに含まれる複数のゲート電極のレイアウトパターンのそれぞれのゲート長を補正する補正部400とを備える。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 引っ張り応力がかかった半導体層が設けられた基板上に高電圧駆動デバイスを形成できるようにする。

【解決手段】 酸化防止膜4をマスクとしてエピタキシャル成長を行うことにより、第1単結晶半導体層3上に第2単結晶半導体層5を形成し、酸化防止膜4をマスクとして第2単結晶半導体層5の熱処理を行うことにより、第2単結晶半導体層5を熱酸化させるとともに、第2単結晶半導体層5の構成成分を歪み半導体領域R1の第1単結晶半導体層3内に拡散させ、歪み半導体領域R1の第1単結晶半導体層3を第3単結晶半導体層3´に変換し、エピタキシャル成長を用いることにより、無歪み半導体領域R2の第1単結晶半導体層3上および歪み半導体領域R1の第3単結晶半導体層3´上に第4単結晶半導体層7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗体における抵抗値のばらつきが抑制され、かつ、MISトランジスタのゲート絶縁膜の破壊が防止される半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、抵抗体5eの上がシリコン酸化膜22によって覆われ、非シリサイド領域であるMISトランジスタ33, 34のゲート電極5c, 5dや不純物拡散層19, 21が露出した状態で、不純物活性化のための熱処理やシリサイド化が行われる。これにより、不純物のオートドープが抑制されるため抵抗体の抵抗値のばらつきが抑制されると共に、不純物の活性化のための熱処理の際にMISトランジスタ33, 34のゲート電極5b, 5c等が露出しているためMISトランジスタ33, 34のゲート絶縁膜4c, 4dが破壊されにくくなる。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】面積当たりに占めるゲート数の割合が大きい密パターンの領域と面積当たりに占めるゲート数の割合が小さい疎パターンの領域とが混在する場合において、1つのマスクを用いて低消費電力に優れた半導体集積回路装置と高速動作に優れた半導体集積回路装置とを作り分けること。

【解決手段】図1(イ):写真製版に使用するマスクの作成時に、高速動作や低消費に効く周辺回路部領域(1)を意図的にパターンが疎(2A<B)となるように形成し、パターンを密(2A≧B)にするメモリ部領域(2)と区別する。図1(ロ):絶縁膜5のマスクエッチにおいて、O2(酸素)などのエッチング条件を変更する。これによって、パターンが密(2A≧B)になっているメモリ部領域(2)とパターンが疎(2A<B)になっている周辺回路部領域(1)とでCDシフト量が別々に変更される。

(もっと読む)

半導体装置の製造方法

【課題】耐圧特性の異なる複数のトランジスタをプロセスルールの変更を伴うことなく同一の半導体基板上に好適に形成することのできる半導体装置の製造方法を提供する。

【解決手段】第1のトランジスタとそれよりも耐圧の低い第2のトランジスタとを同一の半導体基板11に有し、第1及び第2のトランジスタがソース領域及びドレイン領域よりも低不純物濃度のLDD領域33,34、23,24を有してなる半導体装置の製造方法において、低耐圧トランジスタのLDD領域23,24を形成する工程では、該低耐圧トランジスタのゲート電極27をマスクとして不純物の注入を行い、高耐圧トランジスタのLDD領域33,34を形成する工程では、該高耐圧トランジスタのゲート電極37上に残るようパターン形成したレジスト41をマスクとして不純物の注入を行うようにした。

(もっと読む)

出力回路

【課題】出力回路のパターン面積を縮小しながら静電破壊強度を十分に確保する。

【解決手段】本発明の出力回路は第1のアンプ1と第2のアンプ2の各出力が1つの出力パッドP2に接続され、内部回路3からの信号φ1,φ2によって駆動されている。第1のアンプ1は第2のアンプ2より大きな駆動能力を有している。

第2のアンプ2の高電圧側電源端子H2には電源パッドP1から第1の保護抵抗素子r1を通して電源電圧VDDが供給され、その低電圧側電源端子L2には接地パッドP3から第2の保護抵抗素子r2を通して接地電圧VSSが供給されている。また、第2のアンプ2の出力と出力端子P2の間には第3の保護抵抗素子r3が接続されている。これらの第1乃至第3の保護抵抗素子r1、r2,r3は金属配線で形成され、それらの抵抗値は10Ω程度であることが好ましい。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】 MONOS型トランジスタを有する不揮発性半導体記憶装置の高性能化を推進する。

【解決手段】 MONOS型不揮発性メモリのメモリセル(MC1)は、コントロールトランジスタ(C1)とメモリトランジスタ(M1)とで構成されている。コントロールトランジスタ(C1)のコントロールゲート8はn型多結晶シリコン膜からなり、酸化シリコン膜からなるゲート絶縁膜6上に形成されている。また、メモリトランジスタ(M1)のメモリゲート9はn型多結晶シリコン膜からなり、コントロールゲート8の一方の側壁に配置されている。メモリゲート9はドープド多結晶シリコン膜からなり、アンドープドシリコン膜に不純物をイオン注入して形成した多結晶シリコン膜からなるコントロールゲート8よりもシート抵抗が低い。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化が進められてもトランジスタのオン電流を十分に確保することができる半導体装置及びその製造方法を提供する。

【解決手段】 全面に高電圧トランジスタ用のゲート絶縁膜4を形成した後、低電圧領域内に存在するゲート絶縁膜4を除去する際に、活性領域3が露出した時点でエッチングを終了するのではなく、低電圧領域内において、活性領域3の表面よりも素子分離絶縁膜2の表面が、例えば15nm程度低くなるまでオーバーエッチングを行う。次に、低電圧領域内の活性領域3に対して高温急速水素加熱処理を行う。この結果、低電圧領域内の活性領域3の表面から自然酸化膜が除去され、平坦度が増すと共に、角部が丸まる。

(もっと読む)

半導体装置

【課題】 低しきい値電圧のMOSFETを含むCMOS回路の電源投入時あるいは電源遮断時におこすラッチアップを阻止し、通常動作中のサブスレッショルド電流を低減する。

【解決手段】 通常動作時には実質的に十分カットオフできないMOSFETを含むCMOS回路の電源と外部電源との間に、電源電圧制御用のMOSFET(Q)を接続し、電源投入時には低しきい値MOSFETを含むCMOS回路にウエル電圧を投入した後に、上記電源電圧制御用のMOSFETを導通させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 簡易な工程で製造でき、かつ微小リーク電流の発生を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板1の表面に高耐圧ウェル3が形成されている。入力保護回路に含まれる高耐圧系トランジスタN1のドレイン領域11aおよびソース領域11bは高耐圧ウェル3に形成されている。高耐圧系トランジスタN1のドレイン領域11aの下部に隣接するようにp型不純物領域4aが形成されている。このp型不純物領域4aは低耐圧系トランジスタLTの形成領域に形成される低耐圧ウェル4と同一の製造工程で形成されたものである。

(もっと読む)

マルチチャンネルFin電界効果トランジスタを備える半導体素子及びその製造方法

【課題】 半導体素子及びその製造方法を提供すること。

【解決手段】 セル領域と周辺回路領域とを備え、セル領域及び周辺回路領域は、素子分離膜により画定された活性領域を備える半導体基板、素子分離膜の表面上に突出され、少なくとも二つの活性チャンネルを画定する活性領域の一部分、少なくとも二つの突出活性チャンネルを有する半導体基板の活性領域上に形成されたゲート酸化膜、ゲート酸化膜及び半導体基板の素子分離膜上に形成されたゲート電極、及び各ゲート電極の両側の半導体基板の活性領域内に形成されたソース及びドレインを備える半導体素子が提供される。

(もっと読む)

パワー半導体デバイス

垂直絶縁ゲート電界効果パワー・トランジスタ(3)は、2つのトランジスタ・セル(TC3)の間毎の境界において周辺ゲート構造(G31,G32)を有する複数の並列のトランジスタ・セル(TC3)を有する。ゲート構造(G31,G32)は、独立して動作可能となるように互いに絶縁された第1(G31)および第2(G32)のゲートを含む。第1のゲート(G31)は、トレンチ・ゲート(21,22)であり、第2のゲート(G32)は、少なくとも絶縁平面状ゲート部分(13,14)を有する。第1(G31)および第2(G32)のゲートが同時に動作することによって、デバイス(3)のソース領域(16)とドレイン領域(12)の間に伝導チャネル(23c,23b)が形成される。デバイス(3)は、トレンチ・ゲート・デバイスのオン状態抵抗値に近づくオン状態抵抗値を有し、スイッチング性能がDMOSデバイスより良好であり、安全動作領域がトレンチ・ゲート・デバイスより良好である。デバイス(3)は、安定化出力電圧を供給するための回路構成(50)(図14)中でロー側パワー・トランジスタ(6)と直列に接続されたハイ側パワー・トランジスタとすることができる。デバイス(3)は、負荷(L)に電流を供給するための回路構成(60)(図15)中でスイッチとすることもできる。これらの回路構成(50,60)は、第1のゲート(G31)用の電極(G311)に、供給される固定電位を加えるための端子(Vcc,VF)と、第2のゲート(G32)用の電極(G321)に変調電位を加えるためのゲート・ドライバ回路(573、673)とを含む。  (もっと読む)

(もっと読む)

トランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子

【課題】 トランジスタの電気的特性に異常がある場合に、その不良解析に要する時間を短縮することができるようにしたトランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子を提供する。

【解決手段】 ウエーハWに形成されたICチップ100に含まれる代表的なMOSトランジスタ1の製造プロセスを評価するための評価素子10であって、MOSトランジスタ1と同一の製造プロセスによってウエーハWに形成された通常のMOSトランジスタ10aと、この製造プロセスからチャネルドープ工程だけを除いた不完全製造プロセスによって当該ウエーハWに形成されたネイティブトランジスタ10bと、を備えたものである。通常のMOSトランジスタ10aの閾値等に異常があった場合に、その値とネイティブトランジスタ10bの閾値等とを比較することで、その原因がチャネルドープ工程に有るか否かを容易に判断することができる。

(もっと読む)

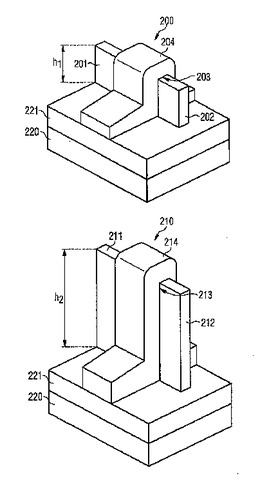

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

並列接続されているトランジスタTr1、Tr2、Tr3のゲート電極1−1、2−1、3−1のゲート幅、及び、隣接し合うゲート電極間の距離が異なり、また、ソース領域やドレイン領域の対応するゲート電極のゲート幅に沿う方向の長さや面積がトランジスタTr1、Tr2、Tr3で種々異なる値を持っている。したがって、同一のトランジスタ群内のトランジスタTr1、Tr2、Tr3間でゲート長などの特性の相関が低下し、それによって、複数のトランジスタ群間における特性のばらつきが小さくなる。  (もっと読む)

(もっと読む)

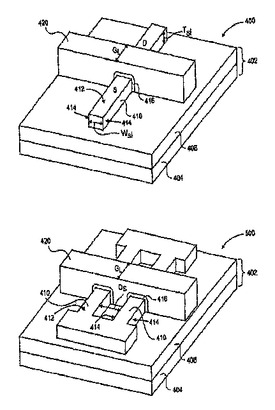

増大されたセル比を有する6トランジスタFINFET型CMOSスタティックRAMセル

本発明に係るCMOSスタティックRAMセルは、2つのアクセスデバイスであり、各々のアクセスデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのアクセスデバイス;2つのプルアップデバイスであり、各々のプルアップデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのプルアップデバイス;及び2つのプルダウンデバイスであり、各々のプルダウンデバイスが複数のフィンを有する3ゲートトランジスタから成るところの2つのプルダウンデバイスを有する。さらに、2つのフィンを有する3ゲートトランジスタを備えたCMOSスタティックRAMセルの製造方法が提供される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

621 - 639 / 639

[ Back to top ]