Fターム[5F048BC02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 形状 (1,394) | 分割ドレイン(ソース) (356)

Fターム[5F048BC02]に分類される特許

341 - 356 / 356

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

高密度二重平面デバイス

基板(10)上に形成された第1及び第2の自立型半導体本体(40N、40P)を有するMOSデバイスである。第1の自立型半導体本体(40N又は40P)の第1の部分は、第2の自立型半導体本体(40P又は40N)の第1の部分に対して非直交かつ非平行な向きに配置される。第1及び第2の自立型半導体本体(40N、40P)のこれらの部分は、それぞれ第1及び第2の結晶配向を有する。第1のゲート電極(60)は、第1の自立型半導体本体(40N又は40P)の第1の部分の少なくとも一部と非直角に交差し、第2のゲート電極(60)は、第2の自立型半導体本体(40P又は40N)の第1の部分の少なくとも一部と非直角に交差する。  (もっと読む)

(もっと読む)

半導体装置及びそれを用いた光半導体リレー装置

【課題】 信号遮断時の出力端子間容量Coffを低減し、且つオン抵抗Ronを低減化

したSOI構造の半導体装置及びそれを用いた光半導体リレー装置を実現する。

【解決手段】 パワーMISFET20は、第1のシリコン基板1の表面上にBOX層(

酸化膜層)2が形成され、このBOX層2の表面上にN+ソース層7、P層6、低不純物

濃度オフセット層5、N+ドレイン層8が設けられている。このP層6上には、ゲート絶

縁膜9を介して第1のゲート電極10が設けられている。そして、第1のシリコン基板1

の裏面には、P層6に対向してBOX層2をゲート絶縁膜とする第2のゲート電極15が

設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】ESD(静電気放電)等のサージに対する耐性をより安定して高く確保することのできる構造を有し、大量生産した場合にもより高い信頼性をもって製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板内の素子領域の内部に配置されるソース層の電流電圧特性の最大電圧値Vmax1と、同素子領域の最も外側に配置されるドレイン層に隣接するソース層の電流電圧特性の最大電圧値Vmax2とが、「Vmax1<Vmax2」なる関係式を満足するような構造とする。さらに、半導体層14の表面の、素子領域の最も外側に配置されるドレイン層N22と素子領域の内部に配置されるドレイン層N12との間に段差をつけて、ドレイン層N22の下方における半導体層14の深さ方向の幅d2を、ドレイン層N12の下方における半導体層14の深さ方向の幅d1よりも大きな幅に設定する。

(もっと読む)

半導体装置及びその製造方法

【課題】電力用トランジスタと制御用半導体素子とを共通の基板上に備え、電力用トランジスタにおける電力損失が従来よりも大幅に低減された半導体装置を提供する。

【解決手段】半導体装置200は、トランジスタ2と、トランジスタ2のゲート電位を制御する半導体素子10、11とを備え、トランジスタ2および半導体素子10、11は共通の炭化珪素基板1の上に形成されており、トランジスタ2と半導体素子10、11とを電気的に分離する素子分離領域12をさらに含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 高耐圧、低耐圧トランジスタを同一基板に備える半導体装置の、高耐圧トランジスタ領域の面積の削減を図る装置及び方法の提供。

【解決手段】 支持基板10a上の絶縁層10b上に形成された第1半導体層10cと、前記第1半導体層10c内に形成された第1高耐圧トランジスタ100Pと、前記絶縁層上に形成された第2半導体層内に形成された第2高耐圧トランジスタ100Nと、第1半導体層と第2半導体層との間に設けられた絶縁層10bに到達する深さを有する第1素子分離領域110aと、前記絶縁層10b上に形成された第3半導体層内の第1低耐圧トランジスタ200Nと、前記第3半導体層内に形成された第2低耐圧トランジスタ200Pと、前記第3半導体層内に形成され、かつ、前記第1低耐圧トランジスタ200Nと前記第2低耐圧トランジスタ200Pとの間に設けられた、前記絶縁層10bに到達しない深さを有する第2素子分離領域とを含む。

(もっと読む)

マルチチャンネルFin電界効果トランジスタを備える半導体素子及びその製造方法

【課題】 半導体素子及びその製造方法を提供すること。

【解決手段】 セル領域と周辺回路領域とを備え、セル領域及び周辺回路領域は、素子分離膜により画定された活性領域を備える半導体基板、素子分離膜の表面上に突出され、少なくとも二つの活性チャンネルを画定する活性領域の一部分、少なくとも二つの突出活性チャンネルを有する半導体基板の活性領域上に形成されたゲート酸化膜、ゲート酸化膜及び半導体基板の素子分離膜上に形成されたゲート電極、及び各ゲート電極の両側の半導体基板の活性領域内に形成されたソース及びドレインを備える半導体素子が提供される。

(もっと読む)

半導体装置

【課題】同一なチップ内でNチャネルおよびPチャネルの両チャネルが高い耐圧特性を有する高耐圧MOSトランジスタを実現でき得るデバイス構造の製造方法を提供する。

【解決手段】本発明は、Nch型L−DMOS101 とPch型L−DMOS102と論理部103 から成る半導体装置であり、Nch型L−DMOS101 は、N型ドリフト領域12、Pウエル19、P型高濃度拡散層20、ソース拡散層21、ドレイン拡散層22、ソースコンタクト14、ドレインコンタクト16、ソース電極配線15、ドレイン電極17、ゲート電極18の各主要素から成り、SOI領域であるN型ドリフト領域12に形成されたこのNch型L−DMOS101のソース電極14と、領域11と、を電気的に導通して同電位になるように構成するデバイス構造である。

(もっと読む)

センス構造体を備える半導体デバイス

パワーセル(14)及びセンスセル(16)に分割される複数のセルを備えるパワー半導体デバイスが記載されている。センスセル(16)の複数のグループ(30、32)がもたらされる。本デバイスは、センスセル(16)のグループの縁においてもたらされる効果の補償を可能にする。  (もっと読む)

(もっと読む)

アバランシェを阻止できる大電流MOSデバイスおよび動作方法。

特に大電流を使用する場合、MOSトランジスタ(51)のドレイン(74)中に、衝撃イオン化によって、電子‐正孔の対が生成されて、それによって寄生バイポーラトランジスタ(38)が破壊的に導電性になる。正孔は、内在の抵抗を有するMOSトランジスタ(51)の本体領域(76)を通過してソース(80)に達し、ソース(80)はグランドのように比較的低電圧で保持される。正孔電流は本体領域(76)中に電圧を発生させてベース(42)として作用する。この増大したベース電圧は寄生バイポーラトランジスタ(38)を導電性にする。この可能性は、エミッタ(44)として作用するソース(80)と本体領域(76)との間のインピーダンスを介してチャネル電流を流すことによって、ソース(80)と本体領域(76)の間に電圧発生させることによって大幅に減少する。これによって、ベース電圧の増大に伴ってエミッタ電圧が増加し、それによって、寄生バイポーラトランジスタ(38)が導電性になるのを防止する。  (もっと読む)

(もっと読む)

高圧接合型電界効果トランジスタ

本発明は、第2の導電型基板(10)内の第1の導電型の第1のウエル(11)と、前記第1のウエル内のそれぞれ第1の導電型からなるソース(14)及びドレイン(15)と、第2の導電型からなる第2のウエル(12)内に配設されている第2の導電型のゲート(16)とを有している高圧接合型電界効果トランジスタに関しており、前記第2のウエルは逆行性のタイプからなり、さらにソース、ゲート、ドレインの素子がフィールド酸化膜領域(13a〜13d)によって相互に離間されていることを特徴としている。またゲート(16)からソース及びドレイン領域の方向にフィールドプレート(17a,17b)がフィールド酸化膜(13a,13b)の上方で延在している。  (もっと読む)

(もっと読む)

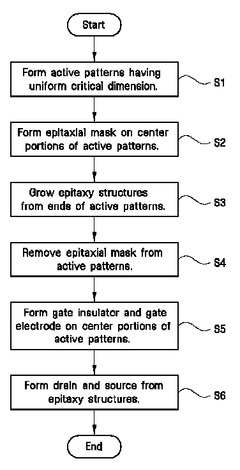

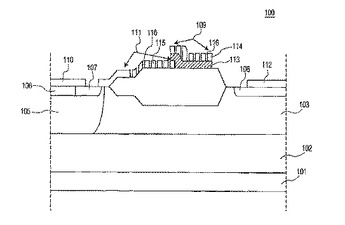

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

直流ノード拡散領域の下に埋め込み酸化物を有さず、酸化物ホールを有する差別化SOI構造

直流ノード拡散領域の下に埋め込み酸化物を設けず、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。印加電圧Vdd、接地GND、基準電圧Vrefおよびその他の類似DCノードなどのDCノード拡散領域の直下に存在する埋め込み酸化物を設けずに、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。本発明の選択的SOI構造をIC中に用いて回路の性能を改善することができる。本発明の選択的SOI構造は、上に配置された複数のSOIデバイスを有する上部Si含有層を備える絶縁体上シリコン(SOI)基板材料を含む。本SOIデバイスは、本体接触部領域を介して下地のSi含有基板と接触する。下地の埋め込み酸化物領域を備えないDCノード拡散領域がSOIデバイスの一つに隣接する。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

並列接続されているトランジスタTr1、Tr2、Tr3のゲート電極1−1、2−1、3−1のゲート幅、及び、隣接し合うゲート電極間の距離が異なり、また、ソース領域やドレイン領域の対応するゲート電極のゲート幅に沿う方向の長さや面積がトランジスタTr1、Tr2、Tr3で種々異なる値を持っている。したがって、同一のトランジスタ群内のトランジスタTr1、Tr2、Tr3間でゲート長などの特性の相関が低下し、それによって、複数のトランジスタ群間における特性のばらつきが小さくなる。  (もっと読む)

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】CMOS回路の集積度を高め、かつMOSトランジスタのゲート幅の変動を抑えることが可能な半導体集積回路を提供する。

【解決手段】PMOS及びNMOSトランジスタ1個から成るインバータを構成するレイアウトとして、素子領域の中央付近にNMOSトランジスタ領域8が配置され、その上下に2分割された状態でPMOSトランジスタ領域1a及び1bが配置され、それぞれのトランジスタ領域1a及び1bと領域8にゲート電極3が延在するように配置されている。NMOSトランジスタ領域8の位置にマスク合わせずれが生じたとしても、各トランジスタのゲート幅に変化がなく、特性を低下させずに集積度を向上させることができる。

(もっと読む)

341 - 356 / 356

[ Back to top ]