Fターム[5F048BD10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 複数MOS間のチャネル長(幅) (608)

Fターム[5F048BD10]に分類される特許

601 - 608 / 608

半導体集積回路

【課題】 保護ダイオードの逆方向耐圧よりも低電圧で動作する保護回路を有する半導体集積回路を実現する。

【解決手段】 静電保護回路には、N+ドレイン層D1とN+多結晶シリコン膜16が接続され、N+多結晶シリコン膜16をゲート、N+ドレイン層D1をドレイン、第1のNウエル層11をソース、第1のPウエル層13をチャネルとする縦型トレンチMOSトランジスタTR1が設けられている。N+多結晶シリコン膜16と第1のPウエル層13、第1のNウエル層11、及びP型シリコン基板10の間に容量C1が設けられている。一方、P型シリコン基板10と第2のNウエル層12の間にダイオードDi1が設けられている。

(もっと読む)

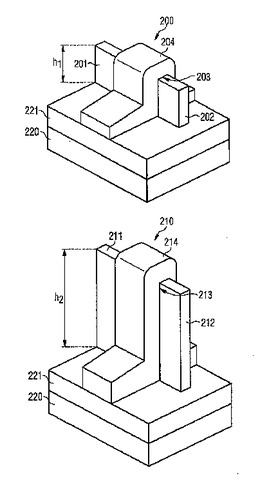

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

複合スペーサ絶縁領域幅を備えた集積回路

異なるスペーサ絶縁領域幅を有するPチャネルトランジスタ(823)とNチャネルトランジスタ(821)とを備えた集積回路が開示されている。一実施形態において、Nチャネルトランジスタのスペーサ絶縁領域幅がPチャネルトランジスタのスペーサ絶縁領域幅よりも小さくなるようにPチャネル領域(115)をマスクしている間に、Nチャネルトランジスタの外側壁スペーサ(321)は除去される。また、Pチャネルソース/ドレインシリサイド領域(809)がPチャネルトランジスタのゲート(119)に対して配置されるよりも、Nチャネルトランジスタのドレイン/ソースシリサイド領域(805)はNチャネルトランジスタのゲート(117)に対してより近い位置に配置される。Pチャネルトランジスタのスペーサ絶縁幅をより大きくし、ソース/ドレインシリサイド領域とゲートとの間の距離をより大きくすることにより、Nチャネルトランジスタのチャネル領域の応力に対しPチャネルトランジスタのチャネル領域の相対圧縮応力を増大させた結果、Pチャネルトランジスタの性能が向上する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

並列接続されているトランジスタTr1、Tr2、Tr3のゲート電極1−1、2−1、3−1のゲート幅、及び、隣接し合うゲート電極間の距離が異なり、また、ソース領域やドレイン領域の対応するゲート電極のゲート幅に沿う方向の長さや面積がトランジスタTr1、Tr2、Tr3で種々異なる値を持っている。したがって、同一のトランジスタ群内のトランジスタTr1、Tr2、Tr3間でゲート長などの特性の相関が低下し、それによって、複数のトランジスタ群間における特性のばらつきが小さくなる。  (もっと読む)

(もっと読む)

非対称の側壁スペーサの形成方法

集積回路半導体デバイスの製造プロセスに統合可能な非対称スペーサの形成方法が提供される。この方法は、基板上にゲート構造(15)を形成するステップと、ゲート構造および基板の上に側壁層(10)を形成するステップとを含み、側壁層は、ゲート構造の第1の側壁の上に第1の部分を含む。第1の部分に隣接して、フォトレジスト構造(11)が形成され、イオンビームにさらされる。フォトレジスト構造は、第1の部分の少なくとも一部をイオンビームから遮蔽するように働く。照射中、ウェハは、イオンビーム(13、17)の経路と、第1の側壁の表面との間に、非直交傾斜角が存在するように配向される。遮蔽されていない側壁部分への放射ダメージにより、その後に続くエッチングがより高速に進むため、非対称スペーサの形成が可能である。  (もっと読む)

(もっと読む)

半導体装置

【課題】低オン抵抗の縦型トランジスタが形成されてなる半導体装置を提供する。また、マルチチャネル化の自由度の高い半導体装置を提供する。

【解決手段】半導体基板30の一方の表面である主面側に形成された第1電極と、もう一方の表面である裏面側に形成された第2電極とを有する縦型トランジスタ101が形成されてなる半導体装置100であって、第1電極が、主面上に形成された層間絶縁膜43を介して、主面側の半導体基板30表層部に形成された拡散領域41,42,48に接続する第1金属層44からなり、裏面側には、半導体基板30の内部に向かってトレンチ35が形成され、第2電極が、トレンチ内に形成され、トレンチ35によって露出された半導体基板30内の半導体層33に接続する第2金属層37からなる半導体装置100とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

半導体装置とその製造方法

【課題】 高耐圧MOSトランジスタの微細化を図る。

【解決手段】 P型ウエル3上にゲート酸化膜9を介して形成されたゲート電極27Fと、前記ゲート電極27Fから離間されて形成される高濃度のN型ソース・ドレイン層15と、前記ソース・ドレイン層15を取り囲むように形成され、前記ゲート電極27F下方に形成されたP型ボディ層18で分断された低濃度のN型のソース・ドレイン層10とを具備したことを特徴とする。

(もっと読む)

601 - 608 / 608

[ Back to top ]