Fターム[5F048BE01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ウェル (5,077) | 濃度分布に特徴のあるウェル (142)

Fターム[5F048BE01]に分類される特許

1 - 20 / 142

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1導電型の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2導電型の不純物層及び第1のエピタキシャル半導体層とは膜厚の異なる第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上に第1のゲート絶縁膜と同じ膜厚の第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置の製造方法

【課題】不純物濃度のピーク位置までの深さが互いに異なる複数の不純物領域を半導体基板内に従来よりも少ない工数で形成するための技術を提供する。

【解決手段】複数の不純物領域を半導体基板内に有し、半導体基板の表面から複数の不純物領域の不純物濃度のピーク位置までの深さが互いに異なる半導体装置の製造方法が提供される。本方法は、光透過率が互いに異なる複数の領域を含むフォトマスクを用いて、半導体基板に塗布されたフォトレジストを露光する露光工程と、フォトレジストを現像して、フォトレジストの露光量に依存した互いに異なる膜厚を有する複数の領域を含むレジストパターンを形成する現像工程と、レジストパターンの膜厚が互いに異なる複数の領域を通して半導体基板に不純物イオンを注入して、半導体基板の表面からピーク位置までの深さが互いに異なる複数の不純物領域を形成する注入工程とを有し、ピーク位置までの深さは、注入される不純物イオンが通るレジストパターンの膜厚に依存することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの更なる高性能化を実現し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜20を形成する工程と、ゲート絶縁膜上にゲート電極22を形成する工程と、ゲート電極の両側における半導体基板内にソース/ドレイン拡散層40,44を形成する工程と、ソース/ドレイン拡散層を形成する工程の後に、複数回のスパイクアニールを行う工程とを有している。

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

【課題】混合信号プロセスにおいてアナログ回路の性能を向上させる方法および装置を提供すること

【解決手段】順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板にアライメントマークとなる溝を形成し、アライメントマークに位置合わせして素子分離領域となる領域を露出し素子領域となる領域を覆うマスク膜を形成し、マスク膜をマスクとして半導体基板を異方性エッチングし、半導体基板の素子分離領域となる領域に素子分離溝を形成し、素子分離溝を絶縁膜で埋め込み素子分離絶縁膜を形成する半導体装置の製造方法において、溝を形成する工程では、マスク膜の厚さに相当する深さよりも浅い溝を形成する。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性の半導体装置を製造するための半導体装置の製造方法を提供する。

【解決手段】半導体基板上に保護膜を形成し、保護膜を介して不純物をイオン注入する。注入した不純物を活性化して不純物層を形成した後、保護膜を除去する。その後、不純物層の表面部の半導体基板を除去し、表面部を除去した半導体基板上に半導体層をエピタキシャル成長する。

(もっと読む)

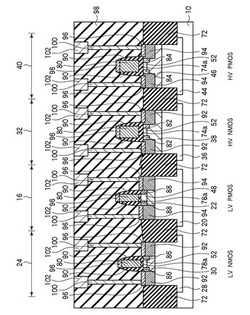

半導体装置及びその製造方法

【課題】低電圧トランジスタ及び高電圧トランジスタの双方の要求を満たし、高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】ボロン又はリンを含む第1の不純物層と、第1の不純物層上に形成された第1のエピタキシャル層と、第1のエピタキシャル層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1のソース/ドレイン領域とを有する第1のトランジスタと、ボロン及び炭素又は砒素を含む第2の不純物層と、第2の不純物層上に形成された第2のエピタキシャル層と、第2のエピタキシャル層上に、第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2の不純物層及び第1のエピタキシャル半導体層よりも薄い第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル不純物の拡散を抑制し、高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板第1及び第2の領域に非晶質化のためのイオン注入を行い、第1の領域及び第2の領域に第1の不純物及び第2の不純物をそれぞれイオン注入し、注入した不純物を活性化して第1の不純物層及び第2の不純物層を形成し、不純物層を形成した半導体基板上に半導体層をエピタキシャル成長し、第1及び第2の領域上にゲート絶縁膜を成長し、第1及び第2のゲート絶縁膜上に第1及び第2のゲート電極をそれぞれ形成する。

(もっと読む)

半導体装置

【課題】IGBT素子領域からダイオード素子領域へのホールの注入を抑制することができ、さらに耐圧を確保できる構造を備えた半導体装置を提供する。

【解決手段】ダイオードセル20において、IGBTセル10のトレンチ38よりも深く、チャネル層37よりも面密度が小さいアノードとしてのP型のリサーフ領域52が形成され、このリサーフ領域52の表層部にP+型の第2コンタクト領域55が形成されている。これにより、チャネル層37によってドリフト層33に形成される空乏層とリサーフ領域52によってドリフト層33に形成される空乏層とがIGBTセル10とダイオードセル20との境界付近で滑らかに接続されるので、当該境界付近における電界集中を緩和することができ、半導体装置の耐圧を確保することができる。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

静電気保護用のMOS型半導体装置

【課題】ESD素子のESD耐量を向上させる。

【解決手段】ESD素子21は半導体基板1表面に形成したP型ウェル領域2上にゲート絶縁膜を介して、一方向に延びた複数本のゲート電極3が相互に平行に設けられており、P型ウェル領域2の表面におけるゲート電極3の直下域がチャネル領域9になっている。そして、チャネル領域9間の領域がN+ソース領域5又はN+ドレイン領域4となっており、N+ソース領域5とN+ドレイン領域4とは交互に配列されている。そして、並列して隣接するゲート電極3間に位置するN+ドレイン領域4を分割し、かつ隣接するゲート電極3を接続するようにゲート電極接合領域10を設ける。なお、ゲート電極接合領域10の直下域にはチャネル領域9と同一の不純物濃度を有する領域11が設けられている。

(もっと読む)

素子分離領域を有する半導体装置とその製造方法

【課題】 素子分離領域の広がりによる素子形成領域間の拡大等の改善を図る。

【解決手段】 半導体基体11には、素子分離領域16が、所定の濃度をもって第1導電型不純物が導入された第1の選択的不純物導入領域17と、第1の選択的不純物導入領域17に比し低い所定の不純物濃度の第2導電型不純物が選択的に導入された第2の選択的不純物導入領域18とによって構成される。第2の選択的不純物導入領域18の不純物濃度の選定によって第1の選択的不純物導入領域17からの不純物の横方向拡散による広がり領域における第1導電型の打消しを行って、素子分離領域16の横方向の実質的広がりを抑制する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】閾値電圧の制御性を向上させて形成された複数種類のトランジスタを備える不揮発性記憶装置、および、それに適した製造方法を提供する。

【解決手段】1つの半導体基板2の表面に形成された複数種類のMOSトランジスタを有する不揮発性記憶装置であって、n形のソース領域14およびドレイン領域15と、その間の半導体基板2の表面上に設けられたゲート絶縁膜17と、ゲート電極18と、ゲート絶縁膜17の直下に位置し、n形不純物とp形不純物との両方を含むチャネル領域42と、を有するMOSトランジスタ10と、n形のソース領域24およびドレイン領域25と、その間の半導体基板2の表面上に設けられたゲート絶縁膜27と、ゲート電極28と、ゲート絶縁膜27の直下に位置し、n形不純物の濃度プロファイルがチャネル領域42と同じであるチャネル領域43と、を有するMOSトランジスタ20と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ボディー抵抗の低減化を図った部分分離ボディー固定SOI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのソース・ドレイン領域形成時において、N+ブロックレジスト51におけるN+ブロック領域41のゲート方向延長領域41aによって、ゲート方向延長領域41a下のウェル領域11には、N型の不純物が注入されることを回避する。ゲート電極9の長手方向延長線上においてN型の不純物が注入される恐れのあるウェル領域11である高抵抗形成領域を、従来の高抵抗形成領域A1より狭い高抵抗形成領域A2とすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストが低減し、電界効果トランジスタの短チャネル効果が抑制された半導体装置を提供する。

【解決手段】第1導電型のソース領域と、第1導電型のドレイン領域と、が表面に選択的に形成された第2導電型のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備え、前記ソース領域の最も曲率が高い部分または前記ドレイン領域の最も曲率が高い部分と同じ深さの前記ウェル領域の位置を基準した場合、前記ウェル領域の深さ方向の前記第2導電型の不純物濃度分布のプロファイルは、前記基準からプラスマイナス0.15ミクロンの範囲に不純物濃度分布のピークを有することを特徴とする半導体装置が提供される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 MOSトランジスタの製造工程を削減し、さらには寄生MOSの敷居値電圧が低下するのを抑制する。

【解決手段】 本発明の半導体装置の製造方法は、ゲート電極形成後にウェル拡散層とは逆導電型のチャネル形成用の不純物をイオン注入する製造方法において、フィールド酸化膜30にチャネル形成用の不純物をイオン注入しない製造方法である。従って、本発明の半導体装置は、フィールド酸化膜30にチャネル形成用の不純物がイオン注入されていない構造となる。

(もっと読む)

1 - 20 / 142

[ Back to top ]