Fターム[5F048BE09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ウェル (5,077) | ウェルに電圧印加 (892)

Fターム[5F048BE09]に分類される特許

881 - 892 / 892

高圧接合型電界効果トランジスタ

本発明は、第2の導電型基板(10)内の第1の導電型の第1のウエル(11)と、前記第1のウエル内のそれぞれ第1の導電型からなるソース(14)及びドレイン(15)と、第2の導電型からなる第2のウエル(12)内に配設されている第2の導電型のゲート(16)とを有している高圧接合型電界効果トランジスタに関しており、前記第2のウエルは逆行性のタイプからなり、さらにソース、ゲート、ドレインの素子がフィールド酸化膜領域(13a〜13d)によって相互に離間されていることを特徴としている。またゲート(16)からソース及びドレイン領域の方向にフィールドプレート(17a,17b)がフィールド酸化膜(13a,13b)の上方で延在している。  (もっと読む)

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

集積半導体回路を保護するための回路装置および方法

サイリスタストラクチャ(SCR)を備えている保護回路を含んでおり並びに保護回路のドライブ制御のための制御回路(TC;C1,R1,I1ないしI3)を含んでおり、これらは両方とも保護すべきエレメント(PV,LV)と基準電位(VB)との間に介挿されており、制御回路(TC;C1,R1,I1ないしI3)は複数の制御信号を生成し、該制御信号がそれぞれサイリスタストラクチャのアクティブエレメント(T1,T2)をドライブ制御するという、集積半導体回路を保護するための回路装置並びに方法が提案される。これにより、保護回路の所期のトリガが規定のスイッチングしきい値および短い導通切り換え時間において実現される。更に制御回路の活性化の持続時間を決定するための形態が提案される。  (もっと読む)

(もっと読む)

ラッチアップに対する脆弱性について集積回路をテストする方法及び装置

集積回路設計のラッチアップに対する脆弱性をテストするためのテストモジュールであって、前記テストモジュールは並列接続された複数のテストブロック(30)を有し、各テストブロック(30)は、それぞれのテストブロック(30)にストレス電流又は電圧を印加するためのインジェクタブロック(12)と、それぞれのインジェクタブロック(12)から異なる距離に連続的に配置された複数のセンサブロック(13)とを有し、各センサブロック(13)はPNPNラッチアップテスト構造を有するテストモジュール。本発明は、従来のICストレス電流テスト、及び標準的なPNPNラッチアップテスト構造を利用するラッチアップ・パラメータ測定の、それぞれの利点を併せ持つ。  (もっと読む)

(もっと読む)

電圧発生回路と半導体集積回路装置

第1電流がエミッタに流れるようにされた第1トランジスタと、上記第1トランジスタよりも大きな電流密度となるような第2電流がエミッタに流れるようにされた第2トランジスタとのベース,エミッタ間の電圧差を第1抵抗に流して定電流を形成し、それと直列にして第2抵抗を回路の接地電位側に設け、上記第1トランジスタと第2トランジスタのコレクタと電源電圧との間に第3抵抗と第4抵抗とを設け、上記第1と第2トランジスタの両コレクタ電圧とCMOS構成の差動増幅回路に供給して、出力出力電圧を形成するとともに、かかる出力電圧を上記第1トランジスタと第2トランジスタのベースに共通に供給する。 (もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

加速粒子および高エネルギ放射線センサ

加速電子検出器はCMOS構造のモノリシックセンサのアレイを備え、各センサは基板(10)と、エピ層(11)と、p+ウェル(12)と、エピ層(11)によってp+ウェル(12)から分離されたn+ウェル(13)とを含む。p+ウェルには複数のNMOSトランジスタが集積される。センサはまた、バイアス電圧の印加によりエピ層内に発生する電荷担体がn+ウェル(13)にドリフトされるように、エピ層内に欠乏層を確立する深いn領域(15)をp+ウェル(12)の下に含む。検出器は改善された放射線耐性を有し、したがってそれは電子顕微鏡のような加速電子の検出および撮像に適する。 (もっと読む)

半導体集積回路装置

【課題】近年、MOSトランジスタのウェル(基板)に順方向バイアス電圧を印加することが注目されているが、温度変化に対して最大限の順方向バイアス電圧を得ることが難しく、そのための回路構成や占有面積も問題になってきている。

【解決手段】第1導電型(p+;n+)のソース電極Sおよびドレイン電極Dとゲート電極Gとを有し、第2導電型(n;p)のウェル10;20に形成されてなるMISFET1;2を備える半導体集積回路装置であって、前記ウェル10;20の電位Vbp;Vbnを、前記MISFET1;2のソース電極Sおよび該ウェル10;20により形成されるダイオード11;21に対して所定電流Ibp;Ibnを順方向に流すことにより生成する基板バイアス回路110;111〜113を備えるように構成する。

(もっと読む)

半導体集積回路

【課題】 本発明の目的は、高速・低消費電力の半導体集積回路を提供することにある。

【解決手段】 動作状態にある回路と待機状態にある回路を混在するようにして、回路毎にバックゲート電圧を設定可能にする。

【効果】 待機時には小電流とし低消費電力性を得て、動作時には大電流として高速性を得ることができる。

(もっと読む)

半導体集積回路装置

【課題】順方向基板バイアスを印加する場合に、動作温度の上昇にともなうリーク電流の増加を防止する。

【解決手段】順バイアス制御回路FBBが出力するバイアス信号は電流クランプ回路CLMPを通してCMOS回路LSIの基板へ供給される。電流クランプ回路CLMPは不純物濃度の低い拡散層を利用して構成され、温度変化に対して不変な定電流を供給する。

【効果】CMOS回路の低電圧駆動時、動作速度を順バイアスにより向上するとともに、温度上昇時、順バイアス印加にともなうリーク電流の増加を抑制し、高速かつ高信頼性を持った半導体集積回路装置を実現する。

(もっと読む)

半導体装置

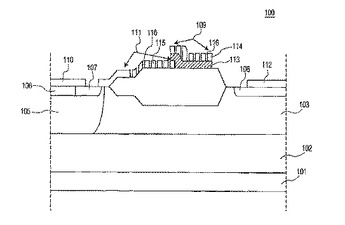

【課題】 BiCMOS集積回路において、工程や回路面積を増加させずに、高耐圧と高ESD耐量を有し、素子のBody電位を半導体基板電位によらず自由に設定できる絶縁ゲートNチャネル電界効果型トランジスタを提供する。

【解決手段】 P型半導体基板1上のN型のエピタキシャル層2上に形成された絶縁ゲート電界効果型トランジスタのドレイン領域を囲む領域にP型ウェル層4を有し、素子の下にN型埋込み層13を有し、平面的にはN型埋込み層の内側で深さ方向ではN型埋込み層の下側及び上側に存在し、上側がP型ウェル層に接するまでの幅をもつP型埋込み層3を有する構造とする。

(もっと読む)

881 - 892 / 892

[ Back to top ]