Fターム[5F048CC05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 容量 (145)

Fターム[5F048CC05]に分類される特許

1 - 20 / 145

ESD保護回路およびこれを備えた半導体装置

半導体集積回路

ESD保護回路

半導体装置

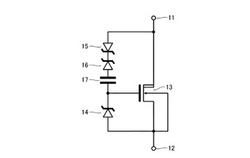

【課題】低消費電力化及び回路面積の削減を図れるようにした半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、電源端子と接地端子の間に接続されたMOSトランジスタと、MOSトランジスタのドレインとゲートの間に接続された第1のダイオードと、MOSトランジスタのドレインとゲートの間に第1のダイオードと互いの順方向が逆向きに直列に接続された第2のダイオードと、MOSトランジスタのドレインとゲートの間に第1及び第2のダイオードと直列に接続されたキャパシタとを備えている。

(もっと読む)

半導体集積回路及び保護回路

【課題】 より効率的にESDサージ電流を流すことができるESD保護回路を備える半導体集積回路を提供する。

【解決手段】 半導体集積回路100は、クランプMOSトランジスタ30と、第1トリガー回路部10と、第2トリガー回路部20と、内部回路2とを備える。第1トリガー回路部10は、出力端がクランプMOS30のゲートに接続され、クランプMOSトランジスタ30内のサージ電流のチャネル経路を開閉制御する。そして、第2トリガー回路部20は、出力端がクランプMOS30のウエルに接続され、クランプMOSトランジスタ30内のサージ電流のバイポーラ経路を開閉制御する。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体集積回路

【課題】実装工程中のESD保護とともに、保護用トランジスタのオフリーク電流を低減する。

【解決手段】RCMOS型のESD保護回路において、RC構成の検出回路の出力を、電源配線2のサージを基準電圧配線3に流す保護用トランジスタ5のゲートに伝達するインバータ回路4内で、出力が上記ゲートに接続されたインバータを、電源配線と第3の電源線7との間に接続している。第3の電源線は実装時には、オープンで実装後には負電圧に接続する。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

信号伝達装置および撮像表示システム

【課題】静電気からの保護をより確実に行うことが可能な信号伝達装置等を提供する。

【解決手段】信号伝達装置は、信号の入力動作および出力動作のうちの少なくとも一方の動作を行う複数の画素と、画素に接続された1または複数の信号線を含む複数の配線と、複数の配線のうちの一の信号線と他の一の配線との間に配設され、第1トランジスタおよび容量素子を有する1または複数の静電気保護回路と、静電気保護回路に接続された第1制御線とを備えている。静電気保護回路では、第1トランジスタのゲートが、第1制御線と直接もしくは間接的に接続され、第1トランジスタにおけるソースおよびドレインのうちの一方が、一の信号線および容量素子の一端に接続されると共に、他方が他の一の配線に接続され、容量素子の他端が、第1トランジスタのゲートに接続されている。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、ノイズの発生が抑制された半導体装置を提供する。

【解決手段】実施形態の半導体装置は、ドレイン層と、ドレイン層の表面から内部にかけてトレンチ状に設けられたドリフト領域と、ドリフト領域の表面から内部にかけてトレンチ状に設けられたベース領域と、ベース領域の表面から内部にかけてトレンチ状に設けられたソース領域と、ドレイン層の裏面に対して略平行な方向に、ソース領域の一部からソース領域の一部に隣接するベース領域を貫通してドリフト領域の一部にまで到達する第1トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、ドレイン層の表面から内部にかけて設けられた少なくとも1つの第2トレンチ内に第1絶縁膜を介して設けられた第1抵抗体層と、ドレイン電極と、ソース電極と、を備える。第1抵抗体層は、ソース電極に電気的に接続されている。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体集積回路

【課題】電源電圧線とグランド線の両方を外部サージから保護することができる半導体集積回路を提供する。

【解決手段】GCNMOS回路70は、電源電圧線63またはグランド線64にサージ電圧が加えられたときに、サージ電圧を放電する。スイッチ72は、内部回路と電源電圧線63およびグランド線64とを接続または分離する。制御回路71は、スイッチ72を制御する。GCNMOS回路70、スイッチ72、および制御回路72のトランジスタは、厚膜トランジスタで構成され、コア領域61の内部回路のトランジスタは、薄膜トランジスタで構成される。制御回路71は、電源電圧線63またはグランド線64にサージ電圧が加えられたときに、スイッチ72をオフにする。

(もっと読む)

ダイオード保護回路、LNB、およびアンテナシステム

【課題】半導体集積回路に設けられた端子に発生するESDへの対策を施すために同半導体集積回路に設けられた、ダイオードが破壊されることを防止する、ダイオード保護回路、LNB、およびアンテナシステムを実現する。

【解決手段】保護抵抗RCNT_INは、ダイオードD3およびD4を流れる電流ΔICNT_INに応じて、保護抵抗RCNT_INに印加された電圧を、ダイオードD3および/またはD4がショートモードで破壊しない電圧にまで降下させる。

(もっと読む)

ESD保護回路

【課題】ESD保護回路の配線部の寄生容量を低減する。

【解決手段】一つの実施形態によれば、ESD保護回路は、複数のダイオードから構成されるESD保護ダイオード、第一の空隙部、及び第二の空隙部が設けられる。ESD保護ダイオードは、信号線と低電位側電源の間に設けられ、信号線に印加される静電気が入力される。第一の空隙部は、信号線と複数のダイオードの少なくともいずれか1つを接続する第一の配線と複数のダイオードが形成される半導体基板の間に設けられる。第二の空隙部は、複数のダイオードの間を接続する第二の配線と半導体基板の間に設けられる。

(もっと読む)

半導体装置

【課題】ESD保護特性のすぐれたESD保護回路を含む半導体装置を構築することが課題となる。

【解決手段】静電気によるサージ電圧が印加されたときだけオン状態になるように、抵抗素子20と容量素子21で形成されるRCタイマーとPLDMOSトランジスタ5とからなるRCタイマー付き放電部1を形成する。また、NMOSオフトランジスタ10、15のそれぞれのソース電極13とドレイン電極16同士を接続したノイズ発生防止部2を形成する。前記RCタイマー付き放電部1のPLDMOSトランジスタ5のソース電極6を電源ライン3に接続する。また、該PLDMOSトランジスタ5のドレイン電極8と前記NMOSオフトランジスタ10のドレイン電極11とを接続する。NMOSオフトランジスタ15のソース電極18を接地ライン4に接続する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

1 - 20 / 145

[ Back to top ]