Fターム[5F048CC16]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 出力側 (294)

Fターム[5F048CC16]に分類される特許

1 - 20 / 294

半導体集積回路

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】IGBT終端部でのリカバリ破壊を防ぎ、ダイオードのスナップバックを抑制することができる半導体装置を提供する。

【解決手段】N−型のドリフト層30の上に形成されたP型のチャネル層31を含む半導体基板32のうちチャネル層31側の一面33とは反対側の他面34側に、P++型のコレクタ層53とN++型のカソード層54とが同じ階層に形成されている。そして、P++型のコレクタ層53がトレンチ35の延設方向における表面IGBT専用領域10および表面ダイオード専用領域20の周辺部25にそれぞれ設けられていることによりN++型のカソード層54は四角形状にレイアウトされている。また、P++型のコレクタ層53がエミッタ領域39の終端部39aから距離aを半径とする円形状に設けられていることにより当該四角形状の角部が窪んだ形状にレイアウトされている。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

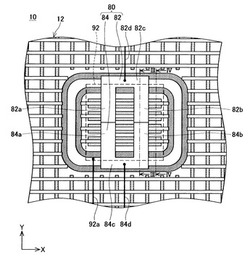

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

集積回路

【課題】ESDに対する安定した保護動作を実現する集積回路を提供する。

【解決手段】実施形態によれば、集積回路は、外部電源と接続される第1の外部端子と、第2の外部端子と、接地された第3の外部端子と、出力トランジスタと、ESD保護回路と、ダイオードと、電源回路と、内部回路と、電流源回路と、駆動回路とを備えている。電流源回路は、電源回路の出力ラインと第3の外部端子との間に直列接続されたコンデンサ及び電流源を含む。駆動回路は、コンデンサと電流源との間に接続された第1の入力端子と、内部回路の出力端子と接続された第2の入力端子と、出力トランジスタの制御電極と接続された出力端子とを有する。第2の外部端子に最大定格電圧より大きい電圧が印加すると、駆動回路は出力トランジスタをオフにし、ESD保護回路が動作する。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

集積回路

【課題】ESDに対する安定した保護動作を実現する集積回路を提供する。

【解決手段】実施形態によれば、集積回路は、電源端子と出力端子との間に接続されたハイサイド出力トランジスタと、ハイサイド出力トランジスタの制御電極と第2の電極との間に接続されたトランジスタと、電源端子とトランジスタの制御電極との間に接続されたトリガー回路と、電源端子と出力端子との間に接続されたESD保護回路とを備えている。電源端子に最大定格電圧より大きい電圧が印加すると、トリガー回路が動作し、トランジスタがオンし、ハイサイド出力トランジスタがオフし、ESD保護回路が動作する。

(もっと読む)

1 - 20 / 294

[ Back to top ]