Fターム[5F064AA13]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | 3次元素子 (13)

Fターム[5F064AA13]に分類される特許

1 - 13 / 13

レイアウトデータ作成装置及び半導体装置

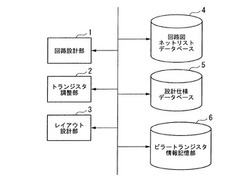

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

三次元集積回路の設計装置、三次元集積回路の設計方法およびプログラム

【課題】論理モジュールチップとメモリアレイチップとから成る三次元集積回路を高性能に実現する設計装置を提供する。

【解決手段】設計装置100は、論理モジュールに関する論理モジュール情報を入力する入力部101と、論理モジュール情報に基づいて、メモリブロックの構成を示すメモリブロック構成情報を生成するメモリブロック構成部103と、論理モジュール情報に基づいて論理モジュールを論理モジュールチップ上に配置する論理モジュール配置部102と、メモリブロック構成部103により生成されたメモリブロック構成情報に基づいて、メモリアレイチップに実装される複数のメモリエレメントにメモリブロックを割り当てるメモリブロック割当部104と、論理モジュールの配置とメモリブロックの割当とを設計結果として出力する出力部105と、を備える。

(もっと読む)

三次元半導体集積回路

【課題】複数チップからの二値データを一箇所に集めずに多値データを生成する。

【解決手段】本発明の例に係る三次元半導体集積回路は、積み重ねられる第一乃至第三チップ11,12,13を有する。第二チップ12内の第二回路15は、二値の第一データAが入力され、第一及び第二電位のうちの一つを出力する第一インバータと、第一インバータの出力端と共通導電体との間に接続される第一キャパシタとを備える。第三チップ13内の第三回路16は、二値の第二データBが入力され、第三及び第四電位のうちの一つを出力する第二インバータと、第二インバータの出力端と共通導電体との間に接続される第二キャパシタとを備える。

(もっと読む)

半導体集積回路装置

【課題】微細ピッチで配列するに好ましい垂直配線構造を持つ半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、回路が形成された半導体基板と、前記半導体基板上に複数層積層された機能素子アレイと、前記機能素子アレイの信号線を前記半導体基板上の回路に接続するための垂直配線とを備え、前記垂直配線は、ストライプ状溝が形成されたあとの絶縁層の前記ストライプ状溝の長手方向に分散的に配置されたメタル層の積み重ね構造として構成されている。

(もっと読む)

三次元集積電気回路の配線構造及びそのレイアウト方法

【課題】複数のモジュール間を3次元的に接続する3次元集積電気回路の配線構造において、ネットワークの高い性能及びハードウェアの量と機能を維持しつつ、配線長を低減し、モジュール間の通信遅延を低減する。

【解決手段】本発明による三次元集積電気回路の配線構造は、複数の電気回路モジュールと、前記電気回路モジュールを相互に交換接続する交換接続手段と、前記電気回路モジュールと前記交換接続手段とを接続する配線及び前記交換接続手段間を接続する配線とで構成される二次元集積電気回路モジュールを三次元的に積層して構成される三次元集積電気回路の配線構造であって、前記二次元集積電気回路モジュール間の配線は前記二次元集積電気回路モジュールのほぼ中央を貫通する貫通ビアを通して構成され、前記電気回路モジュール及び前記交換接続手段とを接続する配線構成をFat Treeトポロジ又はFat H−Treeトポロジを用いて構成される。

(もっと読む)

三次元集積回路設計方法及び三次元集積回路設計装置

【課題】 設計コストと設計時間を節約しつつ、性能的に優れた三次元集積回路を設計する。

【解決手段】 二次元レイアウトデータから三次元レイアウトデータを作成する三次元集積回路設計方法であって、半導体基板上に形成される回路の二次元レイアウトデータを、それぞれ異なる層に配置可能な複数のレイアウトブロックデータに分割し、上下に隣接配置される層のそれぞれに配置されるブロックデータのうち一方を裏表に反転したブロックデータを生成し(4)、上下に重ね合わされる複数の層上に、反転されたブロックデータと反転されていないブロックデータとを交互に配置し、回路内で複数のブロックデータに含まれて複数の層に跨る配線のなかから、遅延又は配線の長さを優先して少なくとも1本選び、選んだ配線を上下の層を接続するビアを通じて再配置する(3a,4a)。

(もっと読む)

集積回路デバイスとその製造方法

【課題】基板と複数のマイクロ電子デバイスを備える集積回路デバイス及びその方法を提供する。

【解決手段】少なくとも一つのマイクロ電子デバイス150に電気的に接触する導電性相互接続部を備える第1の層と、第1の層のラインに対して直角に整列された導電性のラインを備える第2の層であってかつ第2の層のラインが第1の層のラインと電気的に接触している第2の層と、第2の層のラインに対して直角に整列された導電性のラインを備える第3の層であってかつ第3の層のラインが第2の層のラインと電気的に接触している第3の層とを備え、第1の層を第2の層に相互接続し、かつ第3の層を第2の層に相互接続する複数のバイア224等を備える。

(もっと読む)

抵抗率切り換え酸化物または窒化物およびアンチヒューズを含む不揮発性の書き換え可能なメモリセル

メモリセルが記載され、このメモリセルは、電気的に直列に配置された誘電破壊アンチヒューズおよび抵抗率切り換え材料の層を含み、抵抗率切り換え材料は、金属酸化物または窒化物化合物であり、この化合物はただ1種の金属を含む。誘電破壊アンチヒューズは、事前調整ステップにおいて破壊され、アンチヒューズを貫通して破壊領域を形成する。この破壊領域は、狭い導電性パスを提供し、抵抗率切り換え材料への電流を制限するために役立ち、抵抗率切り換え層がより高い抵抗率状態とより低い抵抗率状態との間で切り換えられる場合に制御を改善する。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体集積回路装置の開発期間を短縮すると共に、回路の高性能化かつ低コスト化を図る。

【解決手段】LSIコアとしてのRAM基板11A及びMPU基板11Bとパッケージング後に回路を特定できるFPGA基板12とには、各基板の主面上に、各集積回路に電気的に接続されているパッド51a,51b,52aがそれぞれ形成されている。半導体チップの張り合わせ技術を用いて、RAM基板11Aの主面11a及びMPU基板11Bの主面11bとFPGA基板12の主面12aとが、各パッド51a,51b,52aに、はんだ又は金等よりなるボール14をそれぞれ挟み、対向して接続されることにより、RAM、MPU及びFPGAはそれぞれ電気的に接続されている。

(もっと読む)

ダイ素子が積層された再構成可能なプロセッサモジュール

【課題】 集積回路(IC)ダイ素子が積層されたハイブリッド型の再構成可能なプロセッサモジュールを提供する。

【解決手段】 本明細書に開示する一実施形態に係る再構成可能なプロセッサモジュールは、薄いマイクロプロセッサダイ素子、メモリダイ素子および/またはFPGAダイ素子が積層され、ダイの厚み方向に貫通しているコンタクトによりこれらのダイ素子が相互接続される構造を持つとしてもよい。このようなプロセッサモジュールは、マイクロプロセッサとFPGA間でのデータ共有化速度を大幅に上げることができ、完成アセンブリの歩留まりを改善すると同時に完成アセンブリの製造コストを削減するという効果を奏する。

(もっと読む)

1 - 13 / 13

[ Back to top ]