Fターム[5F064CC30]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | その他 (41)

Fターム[5F064CC30]に分類される特許

1 - 20 / 41

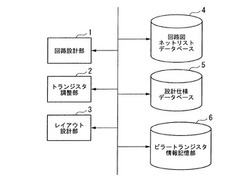

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

半導体集積回路装置の解析方法

【課題】半導体集積回路装置に含まれる回路素子および寄生素子の中から電位変動の発生源から観測点への電位変動の伝播経路の要因となる素子を容易に特定する。

【解決手段】半導体集積回路装置に含まれる回路素子および寄生素子の各々の電位変動量が登録された素子電位変動情報(11)と回路素子および寄生素子の各々の配置位置が登録された素子配置情報(12)とを入力する。素子電位変動情報(11)および素子配置情報(12)を参照して、回路素子および寄生素子の中から予め設定された電位変動閾値よりも大きい電位変動量に対応する素子を選別し、選別された素子の電位変動量および配置位置を示す情報を素子選別情報(10)に登録する。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

半導体装置の設計支援装置、設計支援プログラム及びレイアウト情報生成方法

【課題】従来の設計支援装置により生成したインダクタは、周囲の回路の影響により特性ずれが生じる問題があった。

【解決手段】本発明の設計支援装置は、生成対象のインダクタに接続される接続対象回路領域の第1、第2の接続端子の位置情報を回路設計情報から生成されるフロアプラン結果から得て、インダクタを他の回路と接続する第3、第4の接続端子を、第1の接続端子と第3の接続端子との間及び第2の接続端子と第4の接続端子との間が最短の配線によって接続可能な位置に設定する端子位置設定部10と、第3、第4の接続端子の位置を基準としてインダクタの配線パターンを生成し、当該配線パターンに基づきインダクタのレイアウト情報を生成するパターン生成部13と、を有する。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

ネットリスト作成方法、回路シミュレーション方法、半導体集積回路装置の設計方法及び半導体集積回路装置の製造方法

【課題】パッケージにより生じる回路特性のバラツキを簡便にかつ正確に予測する。

【解決手段】設計されたレイアウトデータと、パッケージに起因してシリコンチップに加わる応力値の分布を示す応力マップデータと、シリコンチップに搭載される各素子について、応力値と素子の特性変動量の関係を示す検量線データとを用いる。レイアウトデータから素子の種類、位置、方向、大きさのうち1つ以上の情報を読み取る。その素子の位置での応力値を応力マップデータから読み取る。その応力値に対するその素子の特性変動量をその素子に対応する検量線データから読み取る。その特性変動量に基づいてその素子の特性を修正してネットリストの作成を行なう。

(もっと読む)

T−コイル回路網設計を生成する方法およびT−コイル回路網

T−コイル回路網を備える回路設計を生成する方法の1つの実施形態は、インダクタのインダクタンスおよびT−コイル回路網の寄生ブリッジ容量を決定するステップ(305−340)を含み得る。寄生ブリッジ容量は、T−コイル回路網の出力に結合された負荷の寄生容量に依存する負荷容量基準と比較され得る(345,355)。T−コイル回路網の出力に結合された回路設計の静電放電(ESD)保護の量、または、T−コイル回路網のインダクタのパラメータが、寄生ブリッジ容量と負荷容量基準との比較に従って、選択的に調整され得る(350,360)。インダクタのインダクタンスと、静電放電保護の量と、インダクタの巻線の幅とを特定可能な回路設計が出力され得る(365)。  (もっと読む)

(もっと読む)

インダクタを備えた半導体集積回路

【課題】半導体集積回路をパッケージに実装した後に、インダクタンスを増加および減少させる調整が可能な半導体集積回路を提供する。

【解決手段】LSIの内部回路106が形成された同一の半導体基板に磁気検出素子100が形成されており、ボンディングパッド114とLSIの内部回路106の間に接続された第1インダクタ101のインダクタンスを磁気検出素子100と磁気検出回路105の出力電圧でモニタし、第1インダクタ101の片方の端子と第2インダクタ102の一端と第3インダクタ103の一端が第1接続部107を介して接続される第1スイッチ108、第2インダクタ102の片方の端子が第2接続部109を介して接続される第2スイッチ110、および、第3インダクタ103の片方の端子が第3接続部111を介して接続される第3スイッチ112を接続または切断状態に切り替えることにより、第一のインダクタ101をトリミングする。

(もっと読む)

CAD装置、インダクタの巻き数求め方法、プログラム及び記憶媒体

【課題】本発明は、高速にインダクタの巻き数を求めることが出来るCAD装置、インダクタの巻き数求め方法、プログラム及び記憶媒体を提供することを課題とする。

【解決手段】CADデータ表示部22が表示したレイアウト表示上で、インダクタ位置指定部23によって、ユーザにインダクタの位置を指定させる。この頂点抽出部24は指定位置の範囲内の頂点の数を求め、巻き数計算部25はこの頂点の数からインダクタの巻き数を算出する。

(もっと読む)

スピントランジスタ、このスピントランジスタを備えたリコンフィギャラブル論理回路および磁気メモリ

【課題】電子と正孔の相互作用による、磁化方向が略平行なときの電流IDPと、磁化方向が略反平行なときの電流IDAPとの差の絶対値の減少を抑制することを可能にする。

【解決手段】表面にn型の半導体領域が設けられた半導体基板10と、半導体領域上に離間して設けられたソース電極30aおよびドレイン電極30bであって、ドレイン電極は半導体領域上に設けられ半導体領域の半導体よりもバンドギャップが大きくかつ価電子帯端が半導体領域の半導体の価電子帯端よりも低いエネルギーを有するn型の第1半導体層31bと、第1半導体層上に設けられた第1強磁性層34bとを有し、ソース電極は半導体領域上に設けられた第2強磁性層34aを有する、ソース電極およびドレイン電極と、ソース電極とドレイン電極との間の半導体領域に設けられたゲート電極24と、を備え、第1および第2強磁性層のうちの一方は磁化方向が不変であり、他方は磁化方向が可変である。

(もっと読む)

半導体装置及びその配置方法

【課題】インダクタの特性劣化を防止できる配置方法の提供。

【解決手段】外部接続端子の配置を決定する第1ステップと、インダクタの空芯部の最大幅を決定する第2ステップと、第1の方向に隣接する前記外部接続端子の略中央を通る第1の仮想線を描く第3ステップと、前記第1の方向と略直交する第2の方向に隣接する前記外部接続端子の略中央を通る第2の仮想線を描く第4ステップと、前記インダクタと最も近接する前記第1の仮想線及び前記第2の仮想線と、前記インダクタの中心との距離の許容範囲を決定する第5ステップと、前記インダクタと最も近接する前記第1の仮想線と前記インダクタの中心との距離、前記インダクタと最も近接する前記第2の仮想線と前記インダクタの中心との距離の少なくとも何れか一方の距離が、前記許容範囲に入るように前記インダクタを配置する第6ステップと、を有することを特徴とする半導体装置の配置方法。

(もっと読む)

磁気素子及び集積回路並びに磁気ランダムアクセスメモリ

【課題】磁気素子本体に電流を流すことなく、磁性体電極の磁化反転が可能な磁気素子及び集積回路並びに磁気ランダムアクセスメモリを提供する。

【解決手段】磁気素子1は、基板6上に第1の強磁性体電極3及び第2の強磁性体電極4を隔置し磁気素子本体2と、第1の強磁性体電極3に接触して高スピンホール効果を有する電極5を配設し、高スピンホール効果を有する電極5に電流を流して第1の強磁性体電極3へスピン注入して磁化反転する。磁気素子本体2へ電流を流すのではなく、高スピンホール効果を有する電極5に電流を流すことでスピンホール効果によるスピン分極を発生させ、第1の強磁性体電極3への移行により磁化反転できる。高インピーダンスの微小磁気メモリ素子及び磁気論理素子やスピン電界効果トランジスタを多段に接続した再構成可能微小磁気論理素子の磁化反転が可能となる。

(もっと読む)

半導体装置

【課題】不揮発的にコンフィギュレーションデータを格納し、かつ高速でコンフィギュレーションを実行することのできるプログラマブル・ロジック装置を実現する。

【解決手段】プログラマブル・ロジック装置の内部状態を設定するプログラム素子(PE)を、可変磁気抵抗素子(TMR0,TMR1)とインバータラッチ(IV0,IV1)とで構成する。可変磁気抵抗素子にコンフィギュレーションデータを格納し、インバータラッチのストレージノード(NM0,NM1)へのデータ転送時にインバータを構成するトランジスタ(PT0,PT1,NT0,NT1)のバックゲートバイアスをフォワードバイアス状態に設定するなどのデータ転送アシストを行う。

(もっと読む)

回路装置および制御方法

【課題】イオン伝導層を用いたイオン伝導素子をより高速に動作させる。

【解決手段】第1電極101と、第2電極102と、第1電極101および第2電極102の間に配置されたイオン伝導層103とを備えるイオン伝導素子と、このイオン伝導素子に、正電圧の印加および負電圧の印加を行うことでイオン伝導素子の動作を制御する両極動作制御部104と、第1電極101に、異なる電圧の負電圧を印加することでイオン伝導素子の動作を制御する単極動作制御部105とを備える。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

半導体装置の製造方法

【課題】歩留りが高く、且つ、配線間容量を十分に低減できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板上に絶縁膜を形成する工程と、絶縁膜の内部に複数の配線溝を形成する工程と、複数の配線溝の内部に複数の配線を形成する工程と、絶縁膜及び複数の配線の上に、複数の配線間の領域のうち選択的に領域を露出する開口部を有するレジストマスクを形成する工程と、レジストマスクを用いたエッチングにより、複数の配線間の領域のうち選択的に露出した領域の絶縁膜を除去してエアギャップ溝を形成する工程と、レジストマスクを除去した後に、複数の配線上を覆うように層間絶縁膜を堆積することによってエアギャップを形成する工程とを含む。

(もっと読む)

半導体装置

【課題】不揮発性メモリに格納された内部回路の動作特性を設定するチューン情報を、メモリセル微細化時においても、電源投入後、正確かつ安定に読出す。

【解決手段】2つのメモリアレイ(1a、1b)各々のメモリセルに互いに相補なデータをチューン情報としてツインセルモードで格納する。ツインセル(TW1、TW2)は、互いに相補なチューンデータを格納するメモリセル(MCA1,MCA2,MCB1,MCB2)で構成され、2つのツインセルが同一チューン情報を格納する。チューン情報読出モード時、ダブルツインセルモードでメモリセルの選択およびデータ読出を行い、2つのツインセルの記憶情報を読出す。読出回路(5)により読出されたデータ(Q)に従って、対象回路の動作特性を設定する。

(もっと読む)

磁気トンネル素子、これを利用した半導体装置およびその製造方法

【課題】スピン平行/反平行状態の2値に加えて、リセット/セット状態の書き込みを可能とするMTJ素子を提供する。

【解決手段】磁気トンネル素子は、一対の強磁性層と、前記強磁性層の間に挟まれるトンネルバリア層とを含み、第1の抵抗状態と、前記第1の抵抗状態よりも高抵抗の第2の抵抗状態の間を遷移する第1機能と、前記第1の抵抗状態より低抵抗の第3の抵抗状態と、前記第2の抵抗状態よりも高抵抗の第4の抵抗状態の間を遷移する第2機能と、を有する。

(もっと読む)

チップレイアウト設計方法および共通ライブラリセル

【課題】POE技術によって作成されたI/Oセルを互い違いに配置する場合、レイアウトツールで自動配置することができず、手動によって配置する必要がある。I/Oセルの配置、種類の変更やチップサイズの変更があるたびに、設計者が配置の変更を手動で行うが、自動配置では生じなかったセル配置ミスや配置に要する工数の増加が生じる。

【解決手段】半導体チップの周辺に、周縁に対する内外方向で複数段にI/Oセルを配置するチップレイアウト設計方法であって、半導体チップに搭載されるべき複数種類のI/Oセルについて、各I/Oセルを、I/Oセルそれぞれの入出力端子位置を非重複の状態で合わせ有するとともに複数種類のI/Oセルの配置領域全体をカバーするセルサイズをもつダミーの共通ライブラリセルに置き換え、自動レイアウトツールを用いて共通ライブラリセルの配置を行う。

(もっと読む)

1 - 20 / 41

[ Back to top ]