Fターム[5F064DD31]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 特定用途素子、セル、ブロックに関する構造 (657)

Fターム[5F064DD31]の下位に属するFターム

Fターム[5F064DD31]に分類される特許

1 - 20 / 71

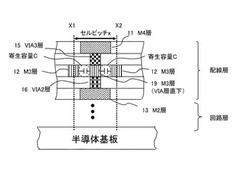

半導体集積回路

半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法

【課題】複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することを可能にする。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

(もっと読む)

回路設計装置、デカップリング容量効果最適化方法、及びプログラム

【課題】 本発明の課題は、デカップリング容量効果を最適化した回路設計を行うことを目的とする。

【解決手段】 上記課題は、回路を構成する複数のセル間のネット毎の高電位電源側及び低電位電源側の配線容量と、各入力ピンの該高電位電源側及び該低電位電源側の容量とを記憶する記憶部と、前記記憶部に記憶された前記各ネットの配線容量と、前記各入力ピンの容量とを参照して、前記構成における非動作パスに対して、セルの置換前の該セルの組み合せと、セルを置換する際の制約に従った置換後のセルの組み合せのうち、該非動作パスの信号値の遷移状態に応じた、各ネット及び各入力ピンの前記高電位電源側又は前記低電位電源側の容量を加算した総容量に基づいて、該総容量が最大となるセルに置換することによって、デカップリング容量効果を最適化する最適化処理部と、を有する回路設計装置により達成される。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置では、コンデンサの容量値が配置場所で変化するため、容量値の見積もりが煩雑になるという問題を解決する。

【解決手段】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置の補償容量部のレイアウト配置の際に、補償容量部を構成する領域に拡散層の矩形領域を配置する。また、該拡散層の矩形領域の各辺に対し、各辺の中心が直行する箇所に矩形開口部を設ける。また、該拡散層の矩形領域の中心線近傍に沿ってゲート電極を直行するように形成する。また、該拡散層の該矩形領域の四隅に上層の金属層と接続するためのコンタクトを形成する。また、該ゲート電極と該拡散層の矩形開口部の重なる箇所にゲート電極と上層の金属層を接続するコンタクトを形成する。また、該ゲート電極が直行する箇所で容量を形成する。また、補償容量の単位セルを構成する。

(もっと読む)

集積回路のレイアウト設計方法、レイアウト設計装置、及び設計プログラム

【課題】高駆動素子が含まれている論理素子経路に遅延素子を挿入してホールドタイム違反を解消する際に、セットアップタイム違反が新たに発生することを防止する。

【解決手段】レイアウト設計方法が、第1フリップフロップ101と、第2フリップフロップ102と、第1フリップフロップ101の出力と第2フリップフロップ102の入力の間の論理回路とを含む集積回路について配置及び配線を行うステップと、ホールドタイム違反を検出するステップと、遅延素子302をホールドタイム違反を解消するように挿入するステップとを備えている。遅延素子302を挿入するステップでは、第1フリップフロップ101と第2フリップフロップ102間の論理素子経路に高駆動素子105が配置されているかが確認され、高駆動素子105が配置されている場合、高駆動素子105の出力に直接に接続されないように遅延素子302が配置される。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置

【課題】占有面積を増やすことなくロジック回路領域におけるトランジスタ特性の変動が抑制される半導体装置を提供する。

【解決手段】NMOS領域の素子形成領域4と、この素子形成領域4に隣り合う他の素子形成領域4との間隔(ゲート幅方向)が一定の間隔(距離2×LA)に設定されている。また、この素子形成領域4と、この素子形成領域4に隣り合う素子形成領域8との間隔(ゲート幅方向)も一定の間隔(距離2×LA)に設定されている。

(もっと読む)

半導体集積回路の設計方法、設計装置およびプログラム

【課題】製造バラつきの下で、クロックスキューの最小化しつつ、クロック信号部での消費電力を最小化する半導体集積回路の設計方法、設計装置および、コンピュータプログラムを提供する。

【解決手段】メッシュ配線構造を駆動するバッファツリーを生成するグローバルクロック構造生成部104と、クロック素子の配置分布とクロックゲーティング構造を考慮してクラスタを生成するクロック素子クラスタ生成部106と、そのクラスタに含まれるクロック素子が属するゲーティッド回路にクロック信号を分配するゲーティングセルを複製して、クラスタを駆動するゲーティングセルとして挿入するゲーティングセル複製・挿入部107と、ローカルクロック構造生成部109と、タイミング解析結果に基づき、クロック素子クラスタを駆動するゲーティングセルの駆動能力を調整するゲーティングセル駆動能力調整部111と、を備える。

(もっと読む)

半導体集積回路

【課題】入力回路または出力回路を介して電源配線にサージ電圧が印加された場合においても、素子面積の増大を抑制しつつ、内部回路を静電破壊から安定的に保護する。

【解決手段】入出力セル3c〜3fの間の隙間に電源保護素子6a〜6dをそれぞれ配置し、電源保護素子6a〜6dとして、電源配線7、8間に接続されたダイオードストリングS2〜S5をそれぞれ用いる。

(もっと読む)

アンチヒューズ構造体および形成方法

【課題】 アンチヒューズ構造体および形成方法を提供する。

【解決手段】 アンチヒューズ構造体は基板上に配置された複数の並行導電フィンを含み、フィンのそれぞれは第1の端部と第2の端部とを有する。第2の電気導体はフィンの第2の端部に電気的に接続される。絶縁体はフィンの第1の端部を覆い、第1の電気導体は絶縁体上に配置される。第1の電気導体は絶縁体によってフィンの第1の端部から電気的に絶縁される。絶縁体は、第2の電気導体と第1の電気導体との間に所定の電圧を印加したときに絶縁破壊し、それによりフィンを介して第2の電気導体と第1の電気導体との間に途切れない電気接続を形成するのに十分な厚さまで形成される。

(もっと読む)

クロック分配素子及びそれを用いたレイアウト設計方法

【課題】簡易かつ精度良くデューティ比を調整することができるクロック分配素子及びレイアウト設計方法を提供すること。

【解決手段】本発明に係るレイアウト設計方法は、クロックツリー回路のレイアウト設計方法であって、クロックツリー回路上に第1のクロック分配素子を配置し、前記第1のクロック分配素子が配置された前記クロックツリー回路に配線し、配線された前記クロックツリー回路についてタイミング検証し、前記タイミング検証の結果に基づいて、前記第1のクロック分配素子を、当該第1のクロック分配素子と入力負荷容量が略等しく遅延値が異なる前記第2のクロック分配素子へ置換するものである。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】レイアウト工程を再度行わずに、タイミング違反が発生した配線の遅延時間を微調整することができ、レイアウトプロセスのTATを短くすることができるレイアウト設計方法及びレイアウト設計装置を提供する。

【解決手段】半導体集積回路のレイアウト設計方法は、レイアウトデータにおける第1の論理セルと第2の論理セルの間の対象配線が配置される領域に、ダミーセル(電源間容量セル、バッファセル)を配置するダミーセル配置ステップ(S2)を含む。また、レイアウト後にタイミング検証を実行し(S4)、タイミング違反が発生した対象配線近傍の電源間容量セルを容量セルへ置換し(S8)、対象配線へ接続する(S9)。又は、タイミング違反配線を第1の配線、第2の配線に切断し、バッファセルの入力端子を第1の配線へ、出力端子を第2の配線へと接続する。

(もっと読む)

集積半導体回路

【課題】ダミーゲートアレイのPN貫通電流による短絡現象により、本来の集積半導体回路構成の不良率に不良率が上乗せされるので、本来の集積半導体回路構成の不良率より高い不良率となっていまい、本来の回路の収率より集積半導体回路全体の収率が下がっていたので、本来の回路が正常であれば、ダミーゲートアレイに不良があってもそのダミーゲートアレイさえ使わなければ正常動作する集積半導体回路を提供する。

【解決手段】メタル層で配線がなされるとともにダミーゲートアレイを有する集積半導体回路において、ダミーゲートアレイの電源回路にスイッチング素子を設けたことを特徴とする集積半導体回路を提供する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】チップサイズが小さくなるように、半導体集積回路を設計できるレイアウト設計装置を提供する。

【解決手段】ネットリスト及び遅延情報に基づいて、タイミング解析を行うタイミング解析部103と、タイミング解析にタイミングエラーが生じる場合、タイミングエラーに関連している調整対象セルを抽出する調整対象抽出部104と、第1セル枠は調整対象セルの境界線であり、第2セル枠の外側に第1拡散領域を有する複数の補強フィルセルを格納する補強フィルセルライブラリ105と、第2セル枠は複数の補強フィルセルの各々の境界線であり、調整対象セルに隣接する通常フィルセルと同じ大きさの第1補強フィルセルを、複数の補強フィルセルから抽出し、第1セル枠と第2セル枠とが隣接配置するように通常フィルセルを第1補強フィルセルに置き換え、トランジスタと第1拡散領域とを接続するセル置換部106とを具備する。

(もっと読む)

ESD保護検証装置及びESD保護検証方法

【課題】信頼性の高いESD保護検証を高速に実行する。

【解決手段】本発明の例に関わるESD保護検証装置は、第1のパッドに接続された素子を抽出する素子抽出部11と、抽出された素子の中から第1のパッドに第1の端子が接続された1つ以上の素子を判別し、その素子の寸法情報に基づく第1の演算値を算出する第1の素子情報調査/演算部12と、第1の基準値と第1の演算値とを比較し、素子が所定のESD耐圧を有するか否か判定する第1のエラー検出部13と、第1のパッドに第1の端子が接続された素子の中から第2の端子が第2のパッドに接続された1つ以上の素子を判別し、その素子の寸法情報に基づく第2の演算値を算出する第2の素子情報調査/演算部14と、第2の基準値と第2の演算値とを比較して、素子が所定のESD耐圧を有するか否か判定する第2のエラー検出部15と、を備える。

(もっと読む)

半導体装置及び半導体装置の補償容量の配置方法

【課題】回路セル内の領域を有効活用して十分な補償容量を確保し、電源電圧の変動を確実に抑制し得る半導体装置等を提供する。

【解決手段】本発明の半導体装置は、第1の方向に並んで配置された複数の素子を含む回路セル2と、この回路セル2の第1の方向に隣接して配置され回路セル2の電源に接続可能な補償容量C1、C2を有する基本端セル1(1a)とを備えて構成される。補償容量C1、C2を構成する拡散層10、11は、回路セル2の所定領域(素子間接続領域R1)を第1の方向に沿って延伸形成されている。また、拡散層10、11の上部にはゲート配線16、17が延伸形成されている。本発明の構成により、回路セル2の素子間接続領域R1を有効に活用しつつ、補償容量のC1、C2の容量値を増加させて電源変動の変動を確実に抑えることが可能となる。

(もっと読む)

マスクパターン生成装置、マスクパターン生成方法及び半導体装置

【課題】データ率を向上することが可能なレイアウト設計データを生成するマスクパターン生成装置を提供する。

【解決手段】マスクパターン生成装置1は、測定部3と、変更部4と、を含む。測定部3は、半導体装置の回路素子を構成する素子パターンと、回路素子を構成しないダミーパターンと、を含むレイアウト設計データに基づいて、ダミーパターンと他のパターンとの間隔を測定する。変更部4は、測定部3にて測定された間隔が予め指定された指定値よりも大きい場合、その間隔を規定しているダミーパターンを拡大して、その間隔が短縮するように、レイアウト設計データを変更する。

(もっと読む)

1 - 20 / 71

[ Back to top ]