Fターム[5F064DD39]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 特定用途素子、セル、ブロックに関する構造 (657) | テストに関するもの (161)

Fターム[5F064DD39]に分類される特許

1 - 20 / 161

半導体装置、半導体ウェハ及び半導体装置の製造方法

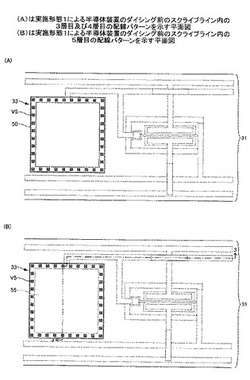

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体装置

【課題】被測定素子の配置密度を高めることが可能な半導体装置を提供する。

【解決手段】異なる層に設けられた列配線M1および行配線M2からなる単位アレイ配線21と、異なる層に設けられた列配線M3および行配線M4からなる単位アレイ配線22とを、互いに異なる層に設ける。複数の単位アレイ配線21,22には、それぞれ、複数の被測定素子11,12のいずれか一つを接続する。複数の単位アレイ配線21,22どうしを部分的に重ね合わせて(オーバーラップさせて)配置することにより、被測定素子11,12の配置密度を高めることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

半導体装置

【課題】ボンディングパッドの直下の酸化膜を壊すことなくウエハテストを行う。

【解決手段】半導体基板9と、半導体基板9上に形成された5層の配線層と、前記5層の配線層のうち、最上層の第5配線層5に形成され、それぞれ一部が露出した複数のボンディングパッド5eと、半導体基板9上に形成され、かつボンディングパッド5eの下において平面視でボンディングパッド5eと重なる位置に配置され、さらにボンディングパッド5eと電気的に接続されたトランジスタ素子等の能動素子と、を有しており、ボンディングパッド5eの直下には、5層の配線層のうちのいずれの配線層も設けられていない緩衝膜7が形成されている。

(もっと読む)

半導体集積回路の設計装置および設計方法

【課題】回路規模の増大を抑制しつつスキャンテスト時の消費電力を削減する半導体集積回路の設計装置および設計方法を提供する。

【解決手段】対象抽出部102は、組み合せ回路のうちの活性化状態が評価される対象となる回路部分を抽出する。削減量算出部104は、組み合せ回路に入力されるスキャンフリップフロップのそれぞれの出力信号を1個ずつ固定化してスキャンフリップフロップ毎の消費電力の削減量を算出し、評価部108は、その結果に基づいて、スキャンフリップフロップの出力信号を固定化したときの消費電力の削減量が最も多いスキャンフリップフロップを選択する。固定化情報蓄積部106は固定化情報を保持し、対象抽出部102はその固定化情報に基づいて、評価対象となる回路部分を抽出する。評価部108は、抽出された回路部分毎に1つのスキャンフリップフロップを選択し、削減できる消費電力値の合計が所定の値になるまで上記を繰り返す。

(もっと読む)

半導体装置

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

半導体装置の製造方法、半導体装置の検査方法、及び半導体装置

【課題】半導体装置の検査において、電極パッドの配列、スクライブ領域の幅に影響されることなくプローブカードを共有化し、プローブカードの製作費用を低減する。

【解決手段】基板20はチップ領域100、スクライブ領域200および電極パッド300を備えている。チップ領域100は基板20上の第1の方向に沿って、スクライブ領域200により互いに分離されるように並んでいる。電極パッド300は第1の方向に沿って周期性をもって配列している。接続用電極パッド320はチップ領域100に形成され、ダミー電極パッド340は少なくともスクライブ領域200に形成されている。電極パッド300の間隔はスクライブ領域200の幅よりも狭い。電極パッド300の配列と平行な方向における、チップ領域100とスクライブ領域200を合わせた幅は、電極パッド300間隔の整数倍である。

(もっと読む)

1 - 20 / 161

[ Back to top ]