Fターム[5F064DD34]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 特定用途素子、セル、ブロックに関する構造 (657) | 電源に関するもの (200)

Fターム[5F064DD34]の下位に属するFターム

Fターム[5F064DD34]に分類される特許

1 - 20 / 137

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体集積回路

【課題】内側のセル列と外側のセル列とでセルの形状が同じ場合において、内側のセル列におけるセルの配列ピッチを外側のセル列におけるセルの配列ピッチより大きくしなくても外側のセル列のセルに接続される配線のための領域を確保することができる。

【解決手段】半導体集積回路は、半導体チップの外周11に沿って配置される複数の第1セル40と、複数の第1セル40の内側で外周11に沿って配置される複数の第2セル40とを具備する。複数の第1セル40及び複数の第2セル40は同一の長方形形状に形成される。複数の第1セル40のそれぞれの長辺4aは外周11に平行である。複数の第2セル40のそれぞれの長辺4aは外周11に垂直である。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

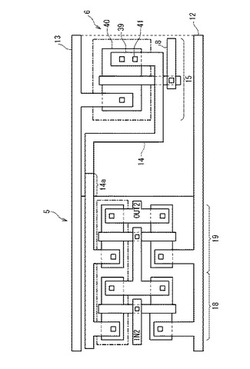

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

LSIの電源遮断領域拡張方法及びそのプログラム

【課題】LSIにおける電源遮断領域を拡張する方法及びそのプログラムを提供する。

【解決手段】回路要素とネット情報とを記述したハードウエア記述ファイルに対して,電源遮断領域の入力端子Aから第1のノードBであるラッチ回路または入力ポートをトレースによって抽出し,さらに,遮断領域の出力端子に接続される第1のアイソレーションセルの出力端子A’から第2のノードB’であるラッチ回路または出力ポートをトレースによって抽出する第1の抽出工程と,第1のノードBから第3のノードCとなるラッチ回路または出力ポートをトレースによって抽出し,さらに,第2のノードB’から第4のノードC’であるラッチ回路または入力ポートをトレースによって抽出する第2の抽出工程とにより,無駄に動作する組み合せ回路を抽出し、前記回路をハードウエア記述ファイルと電源仕様ファイルに追加するとともに,アイソレーションセルを移動する工程とを有する。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

半導体装置

【課題】スタンバイ電流を低減したい回路ブロックに電流の供給を制御するスイッチ回路のレイアウト面積を抑制する。

【解決手段】半導体基板上に、第1方向に延伸する第1及び第2電源線で、第1及び第2電源線は第1方向に直交に配置され、第1電源線に第1電源電位が供給され、第2電源線に第2電源電位が供給される第1及び第2電源線と、第1方向に延伸し、第2方向に配置された第3電源線と、アクティブ時に第1及び第2電源電位の間の第1電源電圧で動作する回路ブロックで、複数の第1導電型の第1トランジスタと複数の第2導電型の第2トランジスタを備え、複数の第1トランジスタの少なくとも1つは第3電源線に接続される回路ブロックと、第1電源線と第3電源線の間に接続され、回路ブロックがアクティブ状態のとき第1及び第3電源線を導通状態として第3電源線に第1電源電位を供給し、スタンバイ状態のとき第1及び第3電源線とを非導通状態とする第3トランジスタとを有する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置の性能を下げることなく、コスト低減及び小型化を図ることができる半導体集積回路装置を提供する。

【解決手段】内部回路と、外部から入力された入力信号を内部回路に供給及び内部回路から供給された出力信号を外部に出力する入出力回路と、を有する半導体集積回路装置であって、内部回路に駆動電圧を供給するための内部回路用電源端子と、入出力回路に駆動電圧を供給するための入出力回路用電源端子と、内部回路及び入出力回路に共通のグランド電圧を供給するための共通グランド端子と、を有し、内部回路用電源端子、入出力回路用電源端子、及び共通グランド端子が隣り合って配置されることによって当該3つの端子から単位端子群が形成されていること。

(もっと読む)

半導体装置の設計方法および、これに用いる標準セル

【課題】配線性の向上とレイアウトサイズの縮小を図る。

【解決手段】標準セル1は、長方形の領域を持つセルであり、論理回路用の入力端子6と出力端子7が存在する信号配線領域3と、信号配線領域3を挟んで標準セル1の長手方向の両側にそれぞれ位置し、論理回路用の電源端子8が信号配線領域3から延びて内在する電源配線領域2とからなる。各々の電源配線領域2は、標準セル1の長手方向の両端側に位置する電源端子8の一部を除去可能な領域9を含む。複数の標準セル1を縦および横方向に隣接させて列状に並べると、隣接する2つの電源配線領域2をセル長手方向にて合わせた範囲X内で電源配線10が移動可能である。電源配線10の位置に応じて領域9を取り除いて、電源端子8の長さを変更可能である。標準セル1の長手方向における信号配線領域3の範囲Yは、信号配線の混雑予測に応じて拡縮可能である。

(もっと読む)

半導体集積回路及びその制御方法

【課題】従来技術の半導体集積回路では、電源遮断領域において発生する電圧降下等を抑制することができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、高電位側電源ライン14及び低電位側電源ライン15と、部分電源ライン13a,13bと、高電位側電源ライン14と部分電源ライン13aとの間に設けられた電源スイッチSWA1〜SWAmと、部分電源ライン13aと低電位側電源ライン15との間に設けられた内部回路12aと、高電位側電源ライン14と部分電源ライン13bとの間に設けられた電源スイッチSWB1〜SWBnと、部分電源ライン13bと低電位側電源ライン15との間に設けられた内部回路12bと、部分電源ライン13a,13b間に設けられ、電源スイッチSWA1〜SWAm,SWB1〜SWBnがオンの場合にオンに制御される電源スイッチSWX1〜SWXpと、を備える。

(もっと読む)

レイアウト設計装置、レイアウト設計方法及びプログラム

【課題】半導体集積回路のレイアウト設計において、設計TATの増大を防ぐこと。

【解決手段】半導体集積回路のレイアウト設計装置であって、設計者の指示に基いて配置すべきモジュールをネットリストから選択する配置モジュール選択部と、前記ネットリストを参照して、前記選択されたモジュールの近傍に配置すべき1又は2以上のセルを特定するセル特定部と、前記セル又はセル群の面積を計算する面積計算部と、前記ネットリストにおいて前記選択されたモジュールに接続された配置済みのモジュールと前記選択されたモジュールとを結ぶ線分と、前記選択されたモジュールの外周線との間の交点を、前記セル又は前記セル群を配置すべき位置として決定する位置決定部と、前記面積を有する領域を前記位置に表示する表示部とを有する。

(もっと読む)

1 - 20 / 137

[ Back to top ]