Fターム[5F064EE03]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線の最適化 (421)

Fターム[5F064EE03]に分類される特許

1 - 20 / 421

設計支援装置

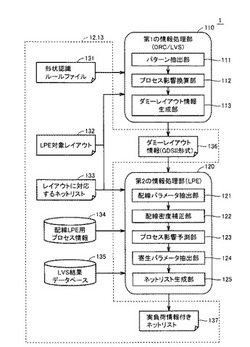

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】レイアウトデータの検証を行うLVS処理やDRC処理と、OPC処理には、プログラムの実装に重複(冗長)な処理が存在する。そこで、これらの処理を、統合することも考えられる。しかし、そのような統合を実際に行えば、プログラムの変更が大規模になり、半導体設計装置のコストを上昇させてしまう。そのため、既存のリソースを有効活用しつつ、OPC処理の処理スピードを向上させた半導体設計装置が、望まれる。

【解決手段】半導体設計装置は、半導体集積回路のレイアウトデータの検証を行うレイアウトデータ検証部と、レイアウトデータ検証部が生成するOPC処理用中間データを用いて、OPC処理を行うOPC処理部と、を備えている。

(もっと読む)

半導体集積回路のレイアウト設計装置、方法、及びプログラム

【課題】アナログ回路において最適な配線効率を実現するためのレイアウト設計を可能にする。

【解決手段】機能ブロックを構成する素子をその種類毎にグループ化する。機能ブロック内の素子の配置を各素子の接続関係に基づいて決定する。この時、グループを構成する素子の分割数を考慮してもよい。機能ブロックの配置順序を面積又は幅が大きい順に配置されるように決定する。また、配置順序はユーザの指定により調整できることが好ましい。配置順序と回路全体の接続情報とに基づいて各機能ブロックの配置位置を決定する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

集積回路の配線方法、集積回路の配線プログラム及びそれを記憶した記憶媒体

【課題】 要求性能を満たすとともに、消費電力を削減することができる配線方法を提供すること。

【解決手段】 本発明の実施形態による集積回路の配線方法は、所定の動作周波数を満たすように第1の配線を求め、前記所定の動作周波数と前記第1の配線のクリティカルパスとを用いて最大迂回配線長を算出し、集積回路の配線を複数の群に分けた場合に、配線群に含まれる前記第1の配線を、前記第1の配線を含む他の配線群内の配線を用いて迂回させることで第2の配線を求め、前記第2の配線と前記第1の配線との差分が前記最大迂回配線長以下ならば、前記第2の配線によって前記第1の配線を更新し、前記第2の配線と前記第1の配線の差分が前記最大迂回配線長よりも大きければ、前記第1の配線を更新しないことを特徴としている。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体集積回路装置の解析方法

【課題】半導体集積回路装置に含まれる回路素子および寄生素子の中から電位変動の発生源から観測点への電位変動の伝播経路の要因となる素子を容易に特定する。

【解決手段】半導体集積回路装置に含まれる回路素子および寄生素子の各々の電位変動量が登録された素子電位変動情報(11)と回路素子および寄生素子の各々の配置位置が登録された素子配置情報(12)とを入力する。素子電位変動情報(11)および素子配置情報(12)を参照して、回路素子および寄生素子の中から予め設定された電位変動閾値よりも大きい電位変動量に対応する素子を選別し、選別された素子の電位変動量および配置位置を示す情報を素子選別情報(10)に登録する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の設計において、EM検証結果がNGとなる確率を低減する。

【解決手段】半導体集積回路の設計方法は、(A)設計対象回路のネットリスト中のネットに仮の寄生容量及び0個以上の仮の寄生抵抗が付加された寄生RC付きネットリストを作成するステップと、(B)寄生RC付きネットリストを用いて回路シミュレーションを行い、ネットにつながるそれぞれの素子端子の電流である素子端子電流及び仮の寄生容量の電流である寄生容量電流を算出するステップと、(C)寄生容量電流をそれぞれの素子端子に分配することによって、素子端子電流の値を変更するステップと、(D)変更後の素子端子電流に基づいて、ネットに関する配線幅制約を算出するステップと、を含む。

(もっと読む)

半導体集積回路の配線設計検証方法

【課題】検証に要する時間をより短縮できる半導体集積回路の配線設計検証方法を提供する。

【解決手段】設計仕様(S7)に基づいてユーザが回路図(S8)に入力した各配線部の最大許容電流値Imaxと、電流密度Jと、配線膜厚hとを抽出し、これらに基づいて各配線部の最小配線幅情報Wmin(S12)を求める。またレイアウトのデータ(S1)から、各配線部に対応する配線経路の情報を付した配線経路ネットリスト(S4)と、各配線部について配線幅情報を付した配線幅ネットリスト(S6)とを作成し、配線経路ネットリストにおける各配線経路について各配線部の最小配線幅情報Wminを付したものと、配線幅ネットリストにおいて対応する配線部の配線幅情報とを比較して、各配線部に流れる電流が許容されている電流値以下か否かを検証する(S13)。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】チップ面積を小さくすることのできるレイアウト設計方法を提供する。

【解決手段】レイアウト設計方法は、所定のタイミング制約F1を満足させるように、セルを配置し、低抵抗配線が形成される第1配線層を使用してセル間のパスの接続配線を形成する処理(ステップS2〜S4)を有する。また、レイアウト設計方法は、タイミング制約F1を満足させたまま、パスの接続配線のうち、セル間に配置されるバッファ回路によって区切られる複数のステージ中の少なくとも一つのステージに対応する接続配線におけるレシーバ側からの一部を、第1配線層から該第1配線層よりも配線遅延が大きくなる第2配線層に置き換えて形成する配線置換処理(ステップS5)を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

クロックツリー設計装置及びクロックツリー設計方法

【課題】クロックレイテンシを最小にする条件下において、クロックスキュー及びバッファ数を比較的少なくする。

【解決手段】実施形態のクロックツリー設計装置は、ターゲットシンクからのマンハッタン距離と最遠シンクからのマンハッタン距離とが等しくなる等距離点の集合を求める等距離点集合算出部と、クロックパスのパス長を最短のマンハッタン距離にするパス設定ブロック領域を設定するパス設定ブロック設定部と、等距離点の集合のうちパス設定ブロック領域内でクロックソースから最も遠い距離の点を分岐点とする分岐点設定部と、クロックソースから分岐点までのパス設定ブロック領域内にターゲットシンクと最遠シンクとの共有パスを設定すると共に、分岐点からターゲットシンクまでのクロックパス及び分岐点から最遠シンクまでのクロックパスをパス長が最短のマンハッタン距離となるように設定するパス設定部とを具備する。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

1 - 20 / 421

[ Back to top ]