Fターム[5F064EE06]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 単位セル、ブロック内(上)の配線 (232) | 不使用セル、ブロックにおける配線 (78)

Fターム[5F064EE06]に分類される特許

1 - 20 / 78

ビア故障から保護するための方法及び構造

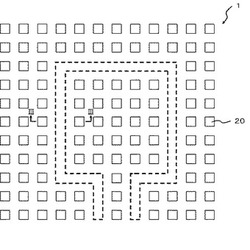

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

回路のレイアウト装置,処理方法およびプログラム

【課題】 回路のレイアウト装置で,EOEの発生しやすい箇所を推定することを目的とする。

【解決手段】 回路レイアウト装置1は,被研磨対象となる回路の配線パターンを含む回路情報を取得する回路情報取得部11,回路を任意の単位領域でメッシュ状に区切り,各メッシュ領域について,メッシュ領域の配線密度とメッシュ領域の各辺に隣接する周辺領域の各々における配線密度とを示すメッシュ情報を生成するメッシュ情報生成部12,各メッシュ領域について,メッシュ領域と各周辺領域の密度の関係がEOEの発生条件に該当するメッシュ領域を抽出し,そのエラー情報を生成するエラー抽出部13を備える。

(もっと読む)

半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラム

【課題】レイアウト設計において、複数のI/Oバッファセルを2列以上に配列する場合、I/Oバッファ領域の近傍にリピータを挿入する領域を確保し、手戻りをできるだけ抑えることができる、半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラムを提供する。

【解決手段】リピータを含まないフィルセル(FC)と、リピータを含むフィルセル(FCR)とが用いられる。フィルセル(FC)は、同列で互いに隣接したI/Oバッファセル(Bm=1、n、Bm=1、n+1など)間に配置される。なお、複数のI/Oバッファセルは、2列に配置されている。I/Oバッファセルからプリミティブセルまでの配線長に基づいて、すでに配置されているフィルセル(FC)が、リピータを含むフィルセル(FCR)に置換される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】情報が読み取られることを防止する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置10は、コンタクト15aを有する第2絶縁層15と、コンタクト17aを有する第3絶縁層17と、第2絶縁層15と第3絶縁層17との間に配置された第2配線層16と、を備え、コンタクト15aとコンタクト17aとの間の第2配線層16の部分には配線が配置されておらず、コンタクト15aとコンタクト17aとの間の距離は、コンタクト15a又はコンタクト17aと、第2絶縁層15及び第3絶縁層17及び第2配線層16内の他のコンタクト又は配線との間の距離よりも短い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

ダミーパターンの設計方法

【課題】チップ面積の増大を抑えつつ半導体集積回路装置の金属配線パターンPTの寄生抵抗に起因する動作不良を抑制可能なダミーパターンの設計方法を提供する。

【解決手段】ビアPTがマトリクス状に配置されたデータ、第1配線PTを含む第1配線層データ、第1配線PTに対して重なり領域を有する第2配線PTを含む第2配線層データ、第2配線PTに対して第1値だけオーバーサイズしたデータ、第1配線PTからオーバーサイズPTとの重なり領域を消去した図形データ、図形を第2値だけアンダーサイズし、第2値以下の図形が消去されたデータ、アンダーサイズPTを第2値だけオーバーサイズして元のサイズに戻した第1ダミーPTデータ、複数のビアPTから第1ダミーPTに対応する領域内のビアPTを抽出したデータ、第2配線PTと第1ダミーPTとを合成した第2配線層データ、上記第2配線層の隙間を埋める第2ダミーPTデータを各々作成する。

(もっと読む)

半導体集積回路装置

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

半導体集積回路、及び半導体集積回路のレイアウト方法

【課題】ロジックセルを配置するためのスペースを十分に確保することのできる、半導体集積回路、半導体集積回路のレイアウト方法、半導体集積回路のレイアウトプログラム、及び半導体集積回路のレイアウト装置を提供する。

【解決手段】自動配置配線ツールにより、ロジックセル、及び前記ロジックセルに接続される信号配線をレイアウトし、ロジックセルレイアウトデータを生成するステップと、前記自動配置配線ツールにより、可変容量セル及び前記可変容量セルの容量を制御する制御配線をレイアウトし、可変容量セルレイアウトデータを生成するステップと、前記ロジックセルレイアウトデータ及び前記可変容量セルレイアウトデータに基づいて、半導体集積回路のレイアウトデータを生成するステップとを具備する。前記可変容量セルレイアウトデータを生成するステップは、前記制御配線を、同一配線層内で単位長あたりの抵抗が前記信号配線のそれと同じになるように、レイアウトするステップを含んでいる。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】レイアウト工程を再度行わずに、タイミング違反が発生した配線の遅延時間を微調整することができ、レイアウトプロセスのTATを短くすることができるレイアウト設計方法及びレイアウト設計装置を提供する。

【解決手段】半導体集積回路のレイアウト設計方法は、レイアウトデータにおける第1の論理セルと第2の論理セルの間の対象配線が配置される領域に、ダミーセル(電源間容量セル、バッファセル)を配置するダミーセル配置ステップ(S2)を含む。また、レイアウト後にタイミング検証を実行し(S4)、タイミング違反が発生した対象配線近傍の電源間容量セルを容量セルへ置換し(S8)、対象配線へ接続する(S9)。又は、タイミング違反配線を第1の配線、第2の配線に切断し、バッファセルの入力端子を第1の配線へ、出力端子を第2の配線へと接続する。

(もっと読む)

ダミーパターンの配置方法及びダミーパターンを備えた半導体装置

【課題】従来よりも簡単にダミーパターンを配置し、スクライブ領域に隣接した半導体チップの形成領域において、層間絶縁膜が薄くなるのを抑制する方法を提供する。

【解決手段】配線層を備えた半導体チップの形成領域と、該形成領域を囲むスクライブ領域とを備えた半導体チップにおいて前記配線層と同じ層からなるダミーパターンを配置する方法であって、前記配線層から少なくとも所定距離だけ離間する位置に第1のダミーパターンを設定する段階と、前記スクライブ領域に隣接する所定幅の範囲内において、前記配線層から少なくとも所定距離だけ離間しかつ前記第1のダミーパターンから少なくとも所定距離だけ離間する位置に第2のダミーパターンを設定する段階と、を備えたダミーパターンの配置方法を提供することによって、上記課題を解決できる。

(もっと読む)

半導体集積回路設計装置および半導体集積回路設計方法

【課題】タイミングマージンの厳しい信号のメタル配線における膜厚変動を抑制することのできる半導体集積回路設計装置および半導体集積回路設計方法を提供する。

【解決手段】半導体集積回路設計装置1は、指定信号メタルパターン抽出部11が、指定された信号名のメタルパターンを記憶装置1000に格納されたレイアウトデータから抽出し、メタルパターン周囲領域設定部12が、指定信号メタルパターン抽出部11により抽出されたメタルパターンの周囲に所定の領域を設定し、メタル被覆率評価部13が、メタルパターン周囲領域設定部12により設定された周囲領域のメタル被覆率を算出して、そのメタル被覆率が所定値以上あるかどうかを評価し、メタル被覆率が所定値未満と評価されたときは、ダミーメタル挿入部14が、上述の周囲領域にダミーメタルを挿入する。

(もっと読む)

半導体集積回路装置及びその設計方法

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】応力の影響を受けるパッド下側のセル配置位置、又はパッド配置位置若しくはバンプ配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトしておく。

(もっと読む)

フィールド酸化物上で終端する見かけの金属接点線を使用してリバースエンジニアリングに対して保護された集積回路及びこれを製造するための方法

【課題】リバースエンジニアリングに対して保護された集積回路及びこれを製造する方法の提供。

【解決手段】半導体基板の接点領域を限定する開口を有する前記半導体基板上に配置されたフィールド酸化物層4と、前記接点領域内に位置する前記フィールド酸化物の部分の上に配置されたメタルプラグ接点7と、前記メタルプラグ接点に接続された金属10とを備える。前記メタルプラグ接点が、前記フィールド酸化物層の前記部分と接触しており、そして、前記フィールド酸化物層の前記部分は、前記メタルプラグ接点を前記接点領域から絶縁していることを特徴とする半導体デバイス。

(もっと読む)

半導体集積回路設計方法及び設計プログラム

【課題】配線膜厚がCMP工程から受ける影響を精度良くモデル化し、従来手法における配線膜厚に対する誤差を削減する方法を提供すること。

【解決手段】半導体集積回路設計方法において、まず、配線が形成された2次元領域における配線の面積割合(配線データ率)及びその2次元領域における配線以外の要素の面積割合(非配線データ率)を独立変数として含む関数により配線の膜厚をモデル化する(ステップS11)。次に、その関数により膜厚をモデル化した配線に基づいて配線設計を行う(ステップS12)。

(もっと読む)

レイアウトパターン生成方法、半導体装置の製造方法、プログラム、レイアウトパターン生成装置

【課題】リワークセル上でのダミー配線に起因するショートエラーを抑制すること。

【解決手段】レイアウトパターン生成方法は、半導体チップ領域に配置されたリワークセルとフィルセルのうち、編集に使用されるリワークセルを特定し、該特定リワークセルの配線層に所定形状の特定パターンを生成するステップと、前記リワークセルのうち前記特定リワークセル以外の非特定リワークセルと前記フィルセルの少なくとも一部の前記配線層にダミー配線パターンを配置するステップと、前記特定リワークセルの前記配線層から前記特定パターンを削除するステップと、前記特定リワークセルを論理セルとして配線して、前記特定リワークセルの前記配線層に配線パターンを配置するステップとを具備している。

(もっと読む)

半導体装置

【課題】MISトランジスタにおいて、リーク電流の発生を抑え、チャネル移動度と信頼性とを共に向上させた半導体装置を提供する。

【解決手段】半導体装置は、第1のウエル領域3a及び第2のウエル領域3bと、素子分離領域2に囲まれた第1の活性領域21aと、素子分離領域2、2Bに囲まれた第2の活性領域21bと、第1の活性領域21a上に形成され、凹部内に埋め込まれたSi混晶層からなるソース/ドレイン領域を有する第2導電型の第1のMISトランジスタMP2と、第2の活性領域21b上に形成された第1導電型の第2のMISトランジスタMN2と、第1の活性領域21a上に形成された第2導電型の分離用MISトランジスタDP2とを備える。第1のMISトランジスタのソース/ドレイン領域は、第1の活性領域21aにおけるゲート長方向の端部に位置する素子分離領域2に接していない。

(もっと読む)

1 - 20 / 78

[ Back to top ]