Fターム[5F064EE36]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | ポリシリコン (91)

Fターム[5F064EE36]に分類される特許

1 - 20 / 91

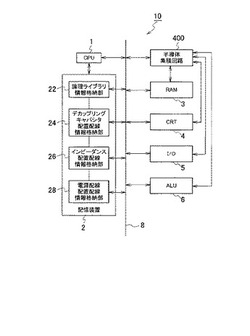

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

チャージアップダメージの検証方法および検証装置

【課題】 配線と非配線とを分けて扱い、マクロ等にも半導体集積回路全体にも適用できるアンテナルールを用いるチャージアップダメージの検証方法等を提供できる。

【解決手段】 配線層毎のアンテナ比の上限値を、注目配線層の階層数と総配線層数とに基づいて設定する第1のステップS10、半導体集積回路のレイアウトデータに基づいて、配線層毎に所与のゲートにチャージアップダメージを与えるノードの面積を演算し、下位の配線層に含まれる同一のノードの面積との積算値を求める第2のステップS20、半導体集積回路のモジュール毎に、注目モジュールに含まれる所与のゲートにチャージアップダメージを与えるノードについて、注目モジュールの最上位配線層までの面積の積算値と所与のゲートの面積とに基づいてアンテナ比を求め、注目モジュールの最上位配線層におけるアンテナ比の上限値と比較する第3のステップS30を含む。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

半導体装置の配線抵抗算出装置

【課題】配線に多数のスルーホールが存在する場合にも、多数のスルーホール分割要素に分割されることを回避し、分割要素の数の増大を抑制し、配線抵抗の算出時間を短縮する装置の提供。

【解決手段】第1配線層と第2配線層の配線を接続する複数のスルーホールを有する領域に、複数のスルーホールを含む枠図形FF1を設定し、枠図形を複数の枠領域FR1〜3に分割する。各枠領域内の複数のスルーホールを合成して1つのスルーホールにまとめ、各枠領域内にはそれぞれ1つの合成スルーホールCT1〜3が設定される。各枠領域に1つに設定されたスルーホールの位置を基準として、第1配線層、第2配線層における枠図形に対応する配線抵抗を分割した抵抗値RL11〜14、RL21〜22と、各枠領域内で1つに設定されたスルーホールの抵抗値RCT1〜3とを用いて、抵抗回路網を作成し、抵抗回路網を1つの抵抗RSに合成する。

(もっと読む)

半導体装置

【課題】 配線に対するエレクトロマイグレーションの影響を排除する点で、従来の構造は十分とはいえない。

【解決手段】 半導体基板の上に第1の配線が配置されている。半導体基板の上であって、第1の配線とは異なる高さに第2の配線が配置されている。第1のビアが、第1の配線と第2の配線とを高さ方向に接続する。第2のビアが、高さ方向に関して第1のビアとは反対側において第1の配線に接続される。第1の配線は、第1のビアとの接続点から基板面内の第1の方向に延在し、第2のビアは、第1のビアよりも第1の方向にずれた位置に配置されており、第2のビアは、高さ方向に電流を流す電流路として作用しない。

(もっと読む)

半導体集積回路のレイアウト装置

【課題】 本発明の課題は、半導体集積回路のレイアウト処理におけるセル配置の際に、隣り合う2つのセルの特性を考慮した配置によって最適化することことを目的とする。

【解決手段】 上記課題は、隣接して配置されるセルの組み合せ毎にショート可否とセル枠のオーバーラップ可能な距離との対応付けを含む最適化ライブラリを格納する第一記憶領域と、デザインルールを満たすセル配置において、前記第一記憶領域に格納されている前記最適化ライブラリを参照することによって、前記ショート可能なセルの組み合せに対して前記セル枠をオーバーラップさせて配置する第一最適化手段とを有することを特徴とする半導体集積回路のレイアウト装置により達成される。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体集積回路装置、設計方法、設計装置、およびプログラム

【課題】チップの面積をより小さくする。

【解決手段】アンテナ比演算部12は、レイアウトデータ蓄積部11から読み出したレイアウトデータに基づいて一の拡散層領域に2以上の独立した金属配線が接続されている構成要素を抽出し、この構成要素に対し、2以上の独立した金属配線のそれぞれの面積と、それぞれの金属配線に接続されるそれぞれの電極の面積とを求め、それぞれの金属配線の面積とそれぞれの金属配線に接続される電極の面積とのアンテナ比をそれぞれ求め、一の金属配線の面積に対する、一の拡散層領域に接続される全ての金属配線の総面積の比に基づいて、一の金属配線に係るプラズマチャージダメージに関する設計基準の緩和値を求める。レイアウト検証部13は、一の金属配線に対応するアンテナ比に対し、一の金属配線に係る緩和値で緩和された設計基準によって検証する。

(もっと読む)

アンチヒューズ構造およびアンチヒューズ構造の製造方法

【課題】低い印加電圧(3V以下)で導通状態を変更可能なアンチヒューズ素子(アンチヒューズ構造)を提供する。

【解決手段】本発明のアンチヒューズ構造100は、第一配線3と、前記第一配線3上に順次積層された、不純物を含有した第一の多結晶シリコン膜6、第一のタングステンシリサイド膜7、第一の窒化タングステン膜8からなる第一のアンチヒューズ部20aと、前記第一のアンチヒューズ部20a上に接続された第二配線10と、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその配置配線方法

【課題】プリミティブセルに用いる金属配線層を増やすことなくプリミティブセルを小型化する。

【解決手段】素子形成領域に複数の回路素子によってプリミティブセルを構成する場合に、素子形成領域に前記プリミティブセルを構成するために必要な第1導電型の第1半導体ウェル領域及び第2導電型の第2半導体ウェル領域を並列的に複数個形成し、その上に前記素子形成領域の延在方向に一定ピッチで規則的に複数のゲート配線を配置したとき、形成された前記第1半導体ウェル領域及び前記第2半導体ウェル領域にL字型に屈曲された形状があるとき、これをL字形の屈曲部分を隣のウェル領域に延長してT字形の形状とし、延長した部分に、ソース電極とドレイン電極が共に電源ライン又はグランドラインに接続するダミーMOSトランジスタを構成し、プリミティブセルを構成する素子の接続を一層の金属配線層の金属配線を用いて行う。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法

【課題】I/Oバッファ変更があった場合であっても、リワーク性を有する半導体集積回路を提供する。

【解決手段】半導体集積回路(7)のチップの外周部に沿って形成されたI/O配置領域(2)と、その外周部の内側に形成されたプリミティブブロック配置領域(3)とを具備する半導体集積回路(2)を構成する。その半導体集積回路(7)は、そのプリミティブブロック配置領域(3)は、容量セルの配置を許容する許容領域(3)と、そのI/O配置領域(2)に沿って形成され、その容量セルの配置が禁止された禁止領域(11)とを含む。

(もっと読む)

半導体装置及び半導体装置のレイアウト設計方法

【課題】アナログ回路に利用される抵抗素子の配置領域面積を低減し、抵抗素子の相対精度を向上させる半導体装置及び半導体装置のレイアウト設計方法を提供する。

【解決手段】一の方向に並列配置されたトランジスタ素子(トランジスタ素子Q1及びトランジスタ素子Q2)と、トランジスタ素子上に層間絶縁膜(層間絶縁膜14)を介して形成された抵抗素子(抵抗素子R1及び抵抗素子R2)を有し、平面視において抵抗素子の長さ方向はトランジスタ素子のチャネル幅方向に直交する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性および集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板1)と、シリコン基板1に設けられた第1のトレンチ3と、第1のトレンチ3に埋め込まれた受動素子層10と、第1のトレンチ3と受動素子層10との間に設けられた第1の絶縁膜(シリコン窒化膜4)と、を備え、上面視において、第1のトレンチ3形成の周縁部分と第1の絶縁膜(シリコン窒化膜4)の周縁部分とが略一致している。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 半導体素子領域のサイズを小さくし、半導体素子領域のレイアウトに必要な時間を短縮する。

【解決手段】 第1領域と第2領域との間に生成される第1半導体素子領域内に第1および第2ゲート電極を生成する。第1配線と、第1配線より外側に位置する第2配線とを、第1半導体素子領域上を延在して配線する。そして、第1ゲート電極と第2配線とを第1領域上または第2領域上で接続し、第2ゲート電極と第1配線とを接続して半導体装置を生成する。これにより、第2配線と第1ゲート電極との接続部分のレイアウトルールを考慮することなく、第1半導体素子領域における第2配線側の境界を設定できる。この結果、第1半導体素子領域のサイズを小さくできる。また、第1半導体素子領域の境界を一度のレイアウトで設定できるため、第1半導体素子領域のレイアウトに必要な時間を短縮できる。

(もっと読む)

1 - 20 / 91

[ Back to top ]