Fターム[5F064EE46]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | ノイズ (477) | クロストーク (189)

Fターム[5F064EE46]に分類される特許

1 - 20 / 189

閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム

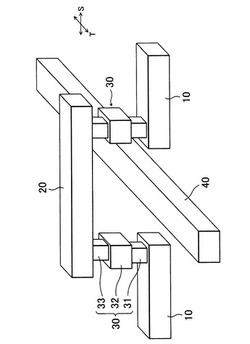

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

マクロ用レイアウト検証装置及び検証方法

【課題】マクロのレイアウト情報に基づいて、当該マクロが使用されるLSIのレイアウト設計時に発生する可能性がある設計規則違反を予め検出する。

【解決手段】マクロ用レイアウト検証装置は、マクロの端子にビアコンタクトを配置したと仮定する手段と、ビアコンタクトとマクロ内レイアウトとの関係が設計規則に違反するか否かを判定する手段と、を具備する。

(もっと読む)

配線配置情報検証方法および配線配置情報検証装置

【課題】半導体集積回路の製造工程等におけるマスクレイアウト等の配線配置情報において、配線のループを効率良く検証する。

【解決手段】マスクレイアウトにおいて、分岐配線毎に矩形状のセグメントに分割し(ステップS01〜S03)、各セグメントの隣接関係の判定条件から配線の端部を特定し(ステップS04〜S05)、配線の末端から縮退加工処理を、末端図形の削除が発生しなくなるまで(ステップS08)、繰り返し行うことで(ステップS06〜S07)、真のループ配線箇所のみ検出し、オリジナルのマスクレイアウト上に強調表示して、配線ループの検証を支援する。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

設計支援装置、設計支援方法および設計支援プログラム

【課題】処理の高速化を図ること。

【解決手段】記憶部1a1は、複数の階層を有する半導体集積回路モデル2の階層Cに属するモジュール2dが備える配線のうち、階層Cより上位の階層A、Bに属するモジュール2a、2bが備える配線に対し加害者ネットまたは被害者ネットとなる可能性のある配線L1に関する配線情報D1を記憶する。配線特定部1bは、階層Bに属するモジュール2b内で閉じた配線であり、かつ、記憶部1a1に記憶されている配線情報D1の配線L1に対する被害者ネットまたは加害者ネットとなる配線を特定する。

(もっと読む)

半導体集積回路装置

【課題】バイアス電流を配給する際のノイズ耐性を大幅に向上させる。

【解決手段】基準バイアス電流回路11は、基準バイアス電流Ipと該基準バイアス電流Ipと電流の極性が逆となる基準バイアス電流Inとを生成し、2本の配線を1ペアとしたバイアス電流用配線H1を介してバイアス電流回路2aに供給する。ペアの配線のうち、一方の配線は他方の線の近傍に平行してレイアウトされており、これら配線の配線長が略同じとしている。バイアス電流回路2aでは、基準バイアス電流Ipを反転させ、基準バイアス電流Inに加算した後、必要なバイアス電流となるように調整し、バイアス電流を生成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

半導体集積回路の設計方法

【課題】設計期間の短縮が可能な半導体集積回路の設計方法を提供する。

【解決手段】本実施形態によれば、半導体集積回路の設計方法は、第1配線層、前記第1配線層上に設けられる第2配線層、及び前記第2配線層上に設けられる第3配線層を有する半導体集積回路の設計方法である。この方法は、前記第2配線層に、第1方向に沿って複数のスペア配線を配置し、前記第3配線層に、前記第1方向に直交する第2方向に沿って複数のスペア配線を配置する工程を備える。さらに、この方法は、前記スペア配線の配置後に、前記第1配線層に素子を配置する工程と、前記素子の配置後に、前記第1乃至第3配線層の少なくともいずれか1つに信号配線を配置する工程と、前記スペア配線を用いて、配線の設計変更を行う工程と、を備える。

(もっと読む)

半導体集積回路階層設計方法

【課題】対象階層マクロブロックから他の階層マクロブロックへの配線間容量を更に抑制すること。

【解決手段】本発明では、チップ全体を階層的に分割した複数の階層マクロブロックを生成する(S2)。階層マクロブロック30に対する回路図データから、初段、最終段のセルを表す境界セル群40〜43、44〜47と、上位の階層マクロブロック60のセル71、72及び境界セル群40〜43、44〜47を接続する境界パス群53、54とを抽出する(S3)。階層マクロブロック30において、境界31の一部分32から内部に延びる境界回路領域61と、境界回路領域61を囲う境界セル領域62と、それ以外の領域63とを決定し(S4)、境界セル群40〜43、44〜47を境界セル領域62に配置する(S5)。階層マクロブロック60にセル71、72を配置すると同時に、境界回路領域61に境界パス群53、54を配置する(S9)。

(もっと読む)

半導体集積回路のレイアウト方法及び半導体集積回路

【課題】クロストークノイズ及び配線遅延を効果的に抑制することができる半導体集積回路のレイアウト方法及び半導体集積回路を提供すること。

【解決手段】本発明は、被シールド配線である信号配線1aを配置する。次に、フローティングメタル7を、信号配線1aに沿う方向に、信号配線1aと隣接させて複数配置する。次に、フローティングメタル7が信号配線1a及び信号配線1b又は1cとカップリング容量を形成している場合には、当該フローティングメタル7を電源電位VDD又はグランド電位GNDと接続する。そして、残存するフローティングメタル7と信号配線1aとの間のカップリング容量値が予め定められた容量値Ccよりも大きければ、残存するフローティングメタル7を削除する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及びプログラム

【課題】半導体集積回路において、シールド配線を配置することで配線間のクロストークの影響を削減するとともに、配置したシールド配線の電位を安定化させること。

【解決手段】半導体集積回路の設計方法は、コンピュータが、半導体集積回路の配線パターンにおいて、配置済の信号配線に対して複数のシールド配線を配置する工程と、前記複数のシールド配線のそれぞれを電源配線に接続する工程と、前記複数のシールド配線を相互に接続する工程と、前記複数のシールド配線のうちの電源配線に接続されていないものを除去する工程と、を含む。

(もっと読む)

伝送線のためのシールド構造体

シールド構造体は、集積回路上の第1金属化層に形成された櫛状構造体が複数の歯を備え櫛状構造体の歯は他方の櫛状構造体に向かって延びる第1、第2櫛状構造体と、第1櫛状構造体から上方に延びる複数の第1導電性ビアと、第2櫛状構造体から上方に延びる複数の第2導電性ビアと、第1金属化層の上方の第2金属化層に配置された第1、第2平面構造体と、第1平面構造体から複数の第1導電性ビアに向かって下方に延びる複数の第3導電性ビアと、第2平面構造体から複数の第2導電性ビアに向かって下方に延びる複数の第4導電性ビアとを備え、第1、第2櫛状構造体、第1、第2平面構造体及び第1〜第4導電性ビアは全て同電位であり接地されることが好ましい。ある実施形態では1つ以上の信号線が第1、第2平面構造体間の第2金属化層に配置され、他の実施形態では1つ以上の信号線が第1、第2平面構造体間の第3金属化層に配置される。 (もっと読む)

配線構造

【課題】電源・信号間の干渉および結合の抑制と、電源ノイズの抑制と、信号間の干渉・クロストークの抑制と、インピーダンス不連続による信号反射の抑制とを、全てバランスよく満たす低コストな高速デバイスを提供する。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

(もっと読む)

半導体集積回路

【課題】チップ面積が増大することなく設計において大きな後戻りをしなくてすむ半導体集積回路を提供すること。

【解決手段】一列に配列された各IOバッファ1〜5と、各IOバッファ1〜5に対応して配列されたパッド接続用配線21〜25と、各IOバッファ1〜5に対応して一列に配列されるとともに、IOバッファ1〜5及びパッド接続用配線21〜25と異なる層にて対応するパッド接続用配線の一部と重なるように配置され、かつ、対応するパッド接続用配線の隣の他のパッド接続用配線まで延長して配線されたIOバッファ切替用配線31〜35と、を備え、各IOバッファ切替用配線31〜35は、隣の他のIOバッファ切替用配線と短絡しないように同じ形状に形成され、各IOバッファ1〜5は、同じ位置にて対応するIOバッファ切替用配線31〜35と電気的に接続される。

(もっと読む)

半導体装置の設計方法

【課題】クロストークノイズによるディレイ変動量を正確に測定する。

【解決手段】複数のインバータを奇数段直列に接続したリングオシレータROと、リングオシレータROの一部の配線(被害側配線)VICに沿って設けられる第1配線(加害側配線)AGGと、前記第1配線AGGに供給する第1パルスを発生するパルス発生回路PGENと、前記第1配線AGGと前記パルス発生回路PGENの間に接続された第1バッファ(加害ゲート)AGと、前記パルス発生回路PGENと前記第1バッファAGとの間に接続される第2配線を具備し、前記第1配線AGGと前記リングオシレータROの一部の配線VICとの間の距離は、前記第2配線と前記リングオシレータROの一部の配線VICとの間の距離より短くする。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

回路のジッタを計算する方法、論理装置及びシステム並びに回路のクロックツリーを合成する方法、論理装置及びシステム

【課題】チップレベルの設計に関する問題に対処し、クロストークカップリングが存在する場合でも正確な経路遅延を計算すること。

【解決手段】一実施例でのクロックツリーにてジッタを計算する方法は、クロックツリーを複数のステージに分割し、クロックツリーに関連する回路の少なくとも一部分のモデルに従って、1以上のステージのジッタを算出する。モデルは回路のジッタのソース各々の表現を含む。本方法は、クロックツリー中の経路又は経路対に関するジッタを計算するため、クロックツリー中の経路又は経路対の各ステージのジッタを互いに統計的に合成するステップを含む。一実施例では、ジッタを効率的に計算し且つクロックスキューゼロを達成するため、モデルは回路の対称的なクロックツリーを合成し、そのツリーでは区六浮くツリーのルートからクロックツリーのシンクに至る全てのパス中の関連するステージは、近似的に電気的に互いに等価な性質を示す。

(もっと読む)

1 - 20 / 189

[ Back to top ]