Fターム[5F083AD18]の内容

Fターム[5F083AD18]に分類される特許

1 - 11 / 11

半導体記憶装置

【課題】データ保持のためのリフレッシュ動作の頻度を低減し、消費電力の小さいDRAMを提供する。また、DRAMに占めるキャパシタの面積を縮小し、集積度の高い半導体記憶装置を提供する。

【解決手段】ビット線、ワード線、トランジスタおよびキャパシタからなる半導体記憶装置であり、トランジスタは、ソース電極およびドレイン電極と、少なくともソース電極およびドレイン電極の上面と接する酸化物半導体膜と、少なくとも酸化物半導体膜の上面と接するゲート絶縁膜とを有し、上面から見て網状の導電膜の網の目の部分に設けられる。ここで、キャパシタは、一対の電極の一方と、網状の導電膜と、一対の電極の一方および網状の導電膜の間に設けられた第2の絶縁膜と、を有する。

(もっと読む)

エンベデッドメモリセルおよびその製造方法

エンベデッドメモリセルは、半導体基板(110)と、少なくとも一部が半導体基板に埋め込まれたソース/ドレイン領域(121)を含むトランジスタ(120)と、少なくとも一部が半導体基板に埋め込まれたキャパシタ(130)とを備える。キャパシタ(130)は、第1の電気絶縁材料(133)で互いから電気的に絶縁されている第1の電極(131)および第2の電極(132)を含む。第1の電極は半導体基板に電気的に接続されており、第2の電極は、トランジスタのソース/ドレイン領域に電気的に接続されている。 (もっと読む)

半導体装置の製造方法及びその製造方法による半導体装置

【課題】隣接するトレンチのストレージノード電極同士のショートを防止する半導体装置を提供する。

【解決手段】半導体基板1の複数のトレンチ8の内部表面に第1のポリシリコン膜12を堆積し、第1のポリシリコン膜12表面に不純物ドープのシリカガラス膜13を堆積した後、シリカガラス膜13をプレート電極形成領域の深さまでエッチングし、シリカガラス膜13から導電型不純物を導入して導電型不純物含有ポリシリコン膜16aと拡散層16bとを有するプレート電極16を形成する。次にトレンチ内部表面にキャパシタ絶縁膜17を形成後、トレンチ8内部に第1の導電膜を堆積し、ストレージノード電極18を形成する。その後、第1及び第2導電層21,22でストレージノード電極とセルの拡散層とを接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化した場合であっても電気的特性の良好なキャパシタを得ることができる半導体装置及びその製造方法を提供する。

【解決手段】トレンチ12cが形成された半導体基板10と、半導体基板上及びトレンチの側壁に形成されたキャパシタ誘電体膜30aと、キャパシタ誘電体膜上に形成されたキャパシタ電極38とを有するキャパシタ40とを有し、キャパシタ電極は、半導体基板上及びトレンチ内に形成された第1の層32aと、第1の層が形成されたトレンチ内に埋め込まれた第2の層34と、第1の層上及び第2の層上に形成された第3の層36aとを有している。

(もっと読む)

アモルファス膜の形成方法および形成装置、ならびに半導体デバイスの製造方法

【課題】超臨界成膜法を用いて基板上にアモルファス膜を形成するにあたり、形成したアモルファス膜のモフォロジーを悪化させることなく、膜中の不純物量を低減し、膜密度を向上させることによって、膜の電気特性を改善させることができる方法および装置を提供する。

【解決手段】(a)膜前駆体を超臨界流体に溶解させた前駆体溶液を成膜チャンバ内に供給して、基板上にアモルファス膜を成膜する工程と、(b)熱処理雰囲気ガス下、前記アモルファス膜をその結晶化温度より低い温度で熱処理する工程とを有する方法により、基板上にアモルファス膜を形成する。前記工程(b)は前記成膜チャンバ内で行ってもよく、前記成膜チャンバとは異なる熱処理チャンバ内で行ってもよい。

(もっと読む)

半導体装置及び半導体装置の容量形成方法

【課題】より低コストに容量素子を含む半導体装置を製造することが可能な半導体装置の容量形成方法を提供する。

【解決手段】GaAs半導体基板3上に少なくともトランジスタと容量素子とが配置される半導体装置の容量形成方法であって、GaAs半導体基板3に少なくとも2個の深さの異なる溝6,ヴィアホール7を同時に掘り込む工程1と、GaAs半導体基板3上及び溝6,ヴィアホール7の内部に、容量素子の電極である容量構造を同時に形成する工程2と、工程2の後に、GaAs半導体基板3の裏面を研磨する工程3とを含む。

(もっと読む)

基板処理方法

【課題】フォトレジストをアッシングする際に、金属膜が酸化されるのを防止する。

【解決手段】窒化チタン膜62の下部電極62A以外の部分のエッチングに使用されたフォトレジスト63をMMT装置を使用して除去するアッシングステップにおいて、ウエハ1がサセプタ21の上に移載された後に、ウエハ1を室温〜90℃の範囲内の所定の温度に加熱し、水素ガスと酸素ガスの混合ガスを流量比が2以上になるように制御して供給し、高周波電力を筒状電極15に高周波電源17から整合器18を介して印加する。筒状磁石19、19でマグネトロン放電が発生し、ウエハ1の上方空間に電荷をトラップしてプラズマ生成領域16に高密度プラズマが生成される。酸素の酸化作用によるフォトレジストのアッシングと、水素の還元作用による窒化チタン膜の酸化防止が同時に作用するので、窒化チタン膜の酸化を防止しつつ、フォトレジストを除去できる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の膜質を向上できる半導体装置の製造方法及び半導体装置を提供すること。

【解決手段】MOS構造のゲートを有する半導体装置100の製造方法であって、半導体基板10上に、気相成長法により気相酸化膜31を形成する気相酸化工程と、気相酸化工程後、気相酸化膜31の形成部位を熱酸化し、気相酸化膜30と半導体基板10との間に熱酸化膜32を形成する追加熱酸化工程を備えることを特徴とする。

(もっと読む)

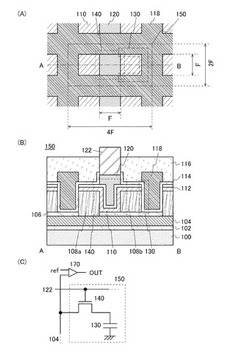

電子素子の製造方法

【課題】本発明は、容量構造が非常に小さくとも、好適な容量特性や記録特性が得られるDRAM半導体メモリまたは電界効果トランジスタ等の電子素子の製造方法を提供する。

【解決手段】誘電体(130)と少なくとも一つの接続電極(120、140)を有する少なくとも一つの容量(150)が形成されている電子素子、特に、DRAM半導体メモリまたは電界効果トランジスタの製造方法において、容量構造が非常に小さくとも、最適な容量特性を得るように容量を作成するため、該誘電体(130)または接続電極(120、140)を、過渡的な分極発生を抑制または少なくとも軽減するように形成する。

(もっと読む)

誘電体層および対応する半導体デバイスを製造するための方法

【課題】多結晶誘電体層の形成方法と前記誘電体層を用いた半導体デバイスの提供。

【解決手段】多結晶誘電体層20は、酸化物または窒化物を含む第1の誘電体材料と前記誘電体層の重量の1重量%未満の第2の材料より形成される。第1の誘電体材料の粒子21境界に沿った漏洩電流が低減するように、前記第1の誘電体材料のエンタルピーより低いエンタルピーを有する非導電性の酸化物または窒化物を形成する第2の材料を含み、第1の誘電体材料の粒子境界に配置される。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

1 - 11 / 11

[ Back to top ]