Fターム[5F083AD61]の内容

Fターム[5F083AD61]の下位に属するFターム

成膜工程時に粒界を形成(HSGなど) (80)

エッチング工程で凹凸を形成 (7)

Fターム[5F083AD61]に分類される特許

1 - 16 / 16

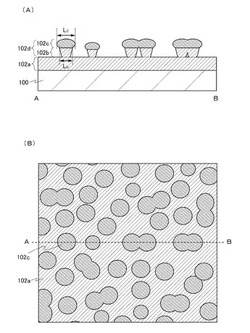

シリコン構造体、当該シリコン構造体を用いた容量素子および当該シリコン構造体の作製方法

【課題】3次元的に複雑な形状のシリコン構造体を提供する。また、当該シリコン構造体を、自然と秩序が生じて自分自身で秩序的なパターン形成が行われる現象を用いて簡便に作製する方法を提供する。

【解決手段】アモルファスシリコン層に水素雰囲気下でプラズマ処理を行って、当該シリコン層表面に微結晶シリコンを成長させる反応過程と、露出しているアモルファスシリコン層をエッチングする反応過程を並行して進行させ、当該シリコン層上に微結晶状の上部構造体とアモルファス状の下部構造体からなるナノ構造体を形成することにより、3次元的に複雑な形状のシリコン構造体を提供することができる。

(もっと読む)

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

DRAMセルキャパシタの電極表面積拡大方法

【課題】DRAMセルのキャパシタ下部電極の形成方法、及び該方法により形成されたキャパシタの提供。

【解決手段】コンテナの絶縁層の上に炭化水素ブロック及びシリコン含有ブロックを含む高分子材料を堆積してテクスチャライジング層38”を形成し、紫外線照射及びオゾンへの暴露によりレリーフ又はポーラス・ナノ構造へ高分子フィルムを変換して、テクスチャライジングされたポーラス又はレリーフのシリコンオキシカーバイドフィルムを得る。次いで、前記テクスチャライジング層の上に導電材料40”を堆積させ、下部電極が上部粗面を有する。別の態様において、第一及び第二の導電金属層を堆積させ、該金属層をアニーリングして周期的ネットワークとして構造化された表面転位を形成し、前記テクスチャライジング下層を形成し、導電金属を気相堆積させて前記テクスチャライジング層の表面転位の上に凝集して、アイランドクラスタ形態のナノ構造を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルの高集積化およびメモリセルのキャパシタの容量増大を図る。

【解決手段】半導体基板の活性領域40を規定する分離トレンチ2内にはフィールドシールド電極であるN型導電性膜4nが形成される。各活性領域40には、その両端に形成されたキャパシタと、ゲート電極12を有する2つのトランジスタとから成る2つのDRAMセルが形成される。活性領域40の両端のキャパシタは、分離トレンチ2の内壁(活性領域40の側壁)の不純物拡散層をストレージ電極とし、分離トレンチ2内のN型導電性膜4nをセルプレート電極とする。活性領域40の両端のキャパシタのセルプレート電極であるN型導電性膜4nは、互いに分離トレンチ2内で繋がっている。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに隣接するシリコンエピタキシャル層同士のショートを防止する。

【解決手段】活性領域13の露出面をドライエッチング又はウェットエッチングで掘り下げることにより、活性領域13の露出面には凹部13aが形成される。これにより、素子分離領域12を構成するフィールド酸化膜12の側面部分12aが露出し、凹部13aの周囲がフィールド酸化膜の側面部分12aで囲まれた状態となる。その後、凹部13aが形成された活性領域13の露出面にシリコンエピタキシャル層19を形成する。ここで、活性領域の露出面は掘り下げられており、活性領域13の幅方向の両端はフィールド酸化膜による壁で囲われていることから、シリコンエピタキシャル層19の横方向への成長を抑制することができ、互いに隣接するシリコンエピタキシャル層19、19間のショートを防止することができる。

(もっと読む)

半導体記憶装置

【課題】金属電極を用いるキャパシタの容量増大を、主に誘電体膜を高誘電率化することで達成する。一般に、より高誘電率の材料は同時に禁制帯幅が小さくなる傾向がある。また、チタン酸ストロンチウムを代表とする比誘電率50程度以上の誘電体は、多くの場合結晶化によって初めて高い誘電率が発現するが、いずれの場合もリーク電流増大という副作用が伴う。材料の置換えは製造装置や工程の大幅変更になり、製造コスト増大となる。

【解決手段】二酸化ハフニウムを他材料に置き換えるのではなく、それ自身の誘電率を向上させることで容量増大を図る。イットリウムなど、イオン半径の大きな元素の微量添加がハフニウムの誘電率を非晶質のまま向上させることを利用する。この非晶質を保持するキャパシタ工程を適用して、低コストで作製可能なDRAMを実現する。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMキャパシタにおいて、上部電極内に発生する応力を低減することにより、容量絶縁膜の劣化を抑制する。

【解決手段】溝部12内に形成された下部電極13と、下部電極13の上を覆う容量絶縁膜14と、容量絶縁膜14を挟んで複数の下部電極13を覆う上部電極15とを備え、上部電極15には、開口部である応力緩衝部17が形成されている。応力緩衝部17である開口部は、上部電極15の上にマスクを形成してエッチングを行うことにより形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程の簡素化及び製造コストの低減が図れる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11からなる活性領域上にゲート絶縁膜13a、13bを介してゲート電極14a、14bを形成する。その後、ゲート電極14a、14bの側面上にサイドウォール16a、16bを形成する。そして、半導体基板11上の全面に、絶縁膜17を形成した後、絶縁膜17にソース・ドレイン形成領域に到達するコンタクトホール18a、18b、18cを形成する。その後、絶縁膜17及びサイドウォール16a、16bをマスクにして、N型不純物のイオン注入を行い、N型ソース領域19a、19c及びN型ドレイン領域19bを形成する。そして、コンタクトホール18a、18b、18c内にコンタクトプラグ20a、20b、20cを形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMとロジックLSIとを混載した半導体集積回路装置の製造において、DRAMのコンタクトホール形成プロセス(ゲート−SAC)とロジックLSIのコンタクトホール形成プロセス(L−SAC)とを両立させる。

【解決手段】DRAMのメモリセル選択用MISFETのゲート電極8A(ワード線WL)を形成する領域の上部のみに窒化シリコン膜9を残し、ロジックLSIを構成するMISFETのゲート電極8Bの上部およびSRAMのメモリセルを構成するゲート電極8C、8Dの上部には窒化シリコン膜9を残さないようにする。その後、上記窒化シリコン膜9とフォトレジスト膜10とをマスクに用いたエッチングで、ゲート電極8A(ワード線WL)およびゲート電極8B〜8Dを同時にパターン形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMとロジックLSIとを混載した半導体集積回路装置の製造プロセスを簡略化する。

【解決手段】ロジックLSIを構成するMISFETのゲート電極7B、ソース、ドレイン(n+型半導体領域16)のそれぞれの表面と、後の工程でDRAMのメモリセル選択用MISFETのゲート電極となる多結晶シリコン膜7の表面とにCoシリサイド層20を同時に形成することによって、製造プロセスの簡略化を実現する。

(もっと読む)

デバイス、カーボンナノウォール、カーボンナノウォールの製造方法

【課題】ナノスケールを有する新規なカーボン構造物を利用した新規なデバイス、カーボンナノウォール、カーボンナノウォールの製造方法を提供する。

【解決手段】デバイスは、伝導領域がカーボンナノウォールを基材として形成されている。カーボンナノウォールはヘテロ原子が含有されているものでも、ヘテロ原子を含有しないものでも良い。ヘテロ原子を含むカーボンナノウォールは、ヘテロ原子と炭素源とを含む原料ガスをプラズマCVD法により製造できる。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMキャパシタにおいて、上部電極内に発生する応力を低減することにより、容量絶縁膜の劣化を抑制する。

【解決手段】本発明の半導体装置は、第1の層間絶縁膜11内に設けられた複数の溝部12の表面を覆う下部電極13と、下部電極13の上を覆う容量絶縁膜14と、容量絶縁膜14を挟んで複数の下部電極の上方を覆う上部電極15とを備えている。上部電極15には、クラック17a、溝17bまたは凹部17cといった応力緩衝部17が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】 縮小化されたセル面積でも大きな静電容量を有するキャパシタを得る。

【解決手段】 メモリセルの製造工程において、下部電極となる多結晶シリコンをフッ酸と酸化剤とを含むエッチング液で洗浄して、その表面を粗面化されて表面積を増大する。

(もっと読む)

半導体記憶装置の製造方法および当該半導体記憶装置

【課題】水素供給が容易かつ効率的な構造を有する半導体記憶装置と、その製造方法を提供する。

【解決手段】セルトランジスタTRのソース領域3に接続するキャパシタを形成する際に、層間絶縁膜8を形成し、これにソース領域3を開口するコンタクトホール8Dを形成する。コンタクトホール8Dの側面および底面を覆う水素含有絶縁膜、たとえば第1のプラズマ窒化膜9Aを形成し、水素雰囲気中で熱処理を行う。このとき水素がソース領域に供給され、ダングリングボンドを終端させる。その後、第1のプラズマ窒化膜9Aをエッチングし、これをコンタクトホール8Dの側面に残存させ、コンタクトホール8Dをプラグ10で埋め込んで、プラグ10上に下部電極12Aが接続するようにキャパシタCAPを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】キャパシタ容量およびデータ保持特性をさらに向上させることができる半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板と、半導体基板に形成されたトランジスタTrと、半導体基板に形成されたトレンチに形成され、トランジスタの一方のノードに接続する第1記憶ノード電極を有する第1メモリキャパシタCtと、トランジスタを被覆して形成された層間絶縁膜と、層間絶縁膜上に形成され、一方のノードに接続する第2記憶ノード電極を有する第2メモリキャパシタCsと、層間絶縁膜を貫通して形成され、第1記憶ノード電極と第2記憶ノード電極を接続する記憶ノードコンタクトプラグとを有し、第1メモリキャパシタ、第2メモリキャパシタおよびトランジスタを有するメモリセルが複数個配置されている構成とする。

(もっと読む)

半導体装置

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

1 - 16 / 16

[ Back to top ]