Fターム[5F083BS25]の内容

Fターム[5F083BS25]の下位に属するFターム

Fターム[5F083BS25]に分類される特許

1 - 9 / 9

論理回路とそれを使用するメモリ

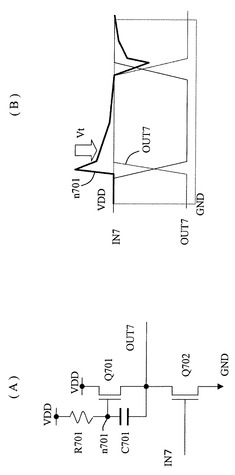

【課題】

低い電源電圧でも動作可能な論理回路を提供する。

【解決手段】

論理回路は,電源電圧側に接続された第1導電型の第1のMOSFETと,基準電圧側に接続されゲートに入力信号が供給される第1導電型の第2のMOSFETと,第1,第2のMOSFETの電流端子の接続ノードに接続された出力端子と,第1のMOSFETのゲートとソース間に設けられたカップリングキャパシタと,第1のMOSFETのゲートと電源電圧との間に設けられた抵抗とを有する。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

半導体メモリー素子

【課題】セルアレイ構造においてコンタクトとゲートラインの間の正確な工程マージンが確保されることで高密度及び高機能の具現が可能な半導体メモリー素子を提供する。

【解決手段】水平ライン形態であり中間部分が上へと延長形成された第1アクティブ領域と、第1アクティブ領域の下に水平ライン形態に形成されて両側端が屈曲して下へと延長形成されて中間部分が下へと延長形成された第2アクティブ領域と、垂直ライン形態であり第1アクティブ領域及び第2アクティブ領域の水平ラインに跨ってそれぞれ形成された第1ゲートライン及び第2ゲートラインと、水平ライン形態であり第2アクティブ領域の延長形成された両側に跨って形成された第3ゲートラインと、第1アクティブ領域の各端、第2アクティブ領域の各端及び両側の屈曲部分、第1アクティブ領域及び第2アクティブ領域の間の第1ゲートライン及び第2ゲートラインに形成された多数のコンタクトを含む。

(もっと読む)

半導体記憶装置および半導体集積回路装置

【課題】SRAMセルのダイナミックスタビリティを考慮して、メモリセルの安定性をさらに増大させる。

【解決手段】フラッシュメモリセルのフローティングゲート(FG)およびコントロールゲート(CG)を製造する工程を利用して、容量素子(C1,C2)を、記憶ノード(SN,/SN)に接続する。すなわち、SRAMセルの負荷トランジスタ(PT1,PT2)およびドライバトランジスタ(NT1,NT2)のゲート電極を、フローティングゲートと同一層の配線で形成し、コントロールゲートと同一の配線層の配線を、負荷およびドライバトランジスタのゲート電極と整列して配置するキャパシタ電極として形成する。

(もっと読む)

MOSFETゲート電極のランディング・パッドのための構造および方法

マイクロエレクトロニクス・トランジスタおよび製作方法の性能および製造可能性を強化するための新たな技術を提供する。

【課題】

【解決手段】トランジスタ装置およびそれを形成する方法であって、基板と、基板上の第1のゲート電極と、基板上の第2のゲート電極と、第2のゲート電極に重なり合うフランジ付き端部の対を備えるランディング・パッドとを備え、第2のゲート電極の構造は、ランディング・パッドの構造と不連続である。

(もっと読む)

半導体記憶装置

【課題】 小面積かつ高速なデータ読出が可能なSRAMセルを有する半導体記憶装置を提供する。

【解決手段】 本発明に係る半導体記憶装置は、トランジスタQN1〜QN4およびトランジスタMN1およびMN2とで構成される。そして、トランジスタQN3およびQN4は非導通に設定される。これに伴い、トランジスタQN1およびQN4の組で対称な構造が形成される。また、トランジスタQN3およびQN2の組で対称な構造が形成される。サブスレッショルドリーク電流は互いの組で同じ値となるため2本の互いに相補のビット線の電位レベルは同じ値を維持する。

(もっと読む)

強誘電体コンデンサラッチ回路

【課題】

従来の主な強誘電体メモリはデータを破壊読み出しするので再書き込みを必要とするか、あるいはメモリセルを行列状に配置して、データを破壊しなとような制御をしていた。したがって、制御回路が複雑で、かつデータ読み出しの際のサイクルタイムが長く、一般的ICの中に取り組むのが容易でなかった。

【解決手段】

強誘電体薄膜を有する強誘電体コンデンサと、MOSFETからなるインバータ回路を2個たすき掛けにしたラッチ回路を組み合わせた構成とした。

(もっと読む)

半導体装置

【課題】 4つのトランジスタで構成したメモリセルを用いた半導体装置において、リフレッシュを伴わない情報保持と安定した読出し動作、低待機電力を実現すること。

【解決手段】 メモリセルMCの記憶ノードN1,N2にキャパシタC1,C2を設け、情報読み出し時には、破壊読み出しをした後に再書き込みを行い、情報保持時には、ビット線BL,/BLを一定電位に保ち、トランジスタMP1,MP2を流れるリーク電流により記憶ノードN1,N2の電位を保持する。その際、トランジスタMN1,MN2のオフ状態でのインピーダンスは、トランジスタMP1,MP2のオフ状態でのインピーダンスよりも大きくする。さらに、チャネル部が5nm程度以下のTFTトランジスタを用いて、リーク電流を低減させる。

(もっと読む)

1 - 9 / 9

[ Back to top ]