Fターム[5F083CR17]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | PROM(Programmable ROM) (484) | 電気的手段によらないで書き込むもの (50) | レーザービームの照射による書き込み (43)

Fターム[5F083CR17]に分類される特許

21 - 40 / 43

半導体記憶装置及びその制御方法

【課題】半導体記憶装置の高速読み出しを可能にする。

【解決手段】半導体記憶装置40には、ビット線とワード線WLとがマトリックス状に配置される。ビット線BLとワード線WLの交差する部分に、ビット線BLとワード線WLの間に並列接続されたダイオード及びヒューズから構成されるメモリセルMCが配置される。メモリセルMCに配置されるダイオードは、カソードがワード線WLに接続され、アノードがビット線BLに接続される。メモリセルMCに配置されるヒューズは、一端がワード線WLに接続され、他端がビット線BLに接続される。

(もっと読む)

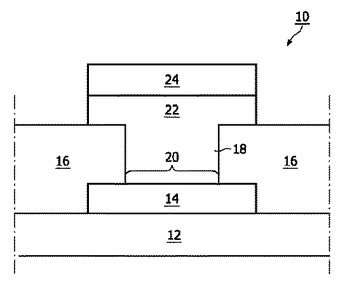

電気スイッチング素子

第1の層14と第2の層22とを含むスイッチング素子10であり、このスイッチング素子は、第1の状態と第2の状態とを有し、第1の状態において、第1の層14及び第2の層22が接触領域22において積層され、第2の状態において、第1の層及び第2の層が接触領域22において剥離され、このスイッチング素子は、当該スイッチング素子に対するスイッチング刺激の印加により第1の状態から第2の状態へと非可逆的に切り換わる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】メモリセル11は、一端に書き込み電圧を印加され絶縁膜破壊でデータを書き込む不可逆性記憶素子12と、一端が前記不可逆性記憶素子の他端に接続される書き込みゲートN型及び読み出しゲートN型トランジスタ13、14とを備える。各メモリセル11には、書き込みゲートN型及び読み出しゲートN型トランジスタ13、14のゲートに接続された書き込みワード線WLWp、読み出しワード線WLRpと、書き込みゲートN型及び読み出しゲートN型トランジスタ13、14の他端に接続された書き込みビット線BLWn、読み出しビット線BLRpとが接続する。書き込みワード線WLWp及び読み出しワード線WLRpは、選択的に駆動するローデコーダ2、読み出しビット線BLRpは、データ書き込み時、所定電圧に充電するライトディスターブ保護回路33を設ける。

(もっと読む)

スケーラブルな2端子ナノチューブスイッチを有する、不揮発性抵抗変化メモリ、ラッチ回路、および動作回路

【課題】

ナノファブリック材料およびスケーラブルな不揮発性ナノチューブスイッチに基づく、スケーラブルなラッチ回路、不揮発性メモリおよび動作回路を提供する。

【解決手段】

不揮発性抵抗変化メモリが提供される。このメモリは少なくとも1つの不揮発性メモリセルと選択回路とを含む。各メモリセルは、導電端子間に配置され、かつ導電端子と電気的に結合しているナノチューブファブリック部材を有する2端子ナノチューブスイッチングデバイスを含む。選択回路は、読出しおよび書込み動作のために2端子ナノチューブスイッチングデバイスを選択するように動作する。制御信号に応答して、書込み制御回路が書込み信号を選択されたメモリセルに供給して、ナノチューブファブリック部材の抵抗変化を引き起こし、この抵抗がメモリセルの情報状態に対応する。選択されたメモリセルと結合している抵抗検知回路は、ナノチューブファブリック部材の抵抗を検知し、制御信号を書込み制御回路に提供する。読出し回路はメモリセルの対応する情報状態を読み出す。複数の不揮発性レジスタファイル内で使用する不揮発性ラッチ回路および不揮発性レジスタファイル構成回路もまた提供される。

(もっと読む)

半導体装置とその作製方法

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131〜134と、ゲート絶縁膜と、ゲート電極103〜106とを有する薄膜トランジスタ118〜121と、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホール142を含む第1のコンタクトホールと、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホールに含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホール142の底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関するものである。

(もっと読む)

メモリ素子、データ記録方法及びICタグ

【課題】導電性液晶半導体を用いて半導体塗液の塗布や室温域での真空蒸着等の単純なプロセスにより情報記録部を作製することができる新規なメモリ素子、これを用いたデータ記録方法及びICタグを提供すること。

【解決手段】本発明のメモリ素子は、液晶化合物を含む導電性液晶半導体材料層にレーザー光をスポット照射して選択的に加熱処理を行い該液晶化合物の液晶状態の分子配向を利用して情報を記憶するメモリ素子であって、互いに平行な複数本の線状の電極から形成された第1の電極群と、前記第1の電極群を覆うように形成された、長い直線的共役構造部分を持ち液晶相としてスメクチック相を有する液晶化合物を含む導電性液晶半導体材料層と、前記導電性液晶半導体材料層上に前記第1の電極群の電極と交差する方向に延びる互いに平行な複数本の線状の透明電極から形成された第2の電極群と、を有することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】レーザ照射パターンを切り替えながら、所望の位置に高速にレーザ照射を行う方法を用いた半導体装置の作製方法を提供する。

【解決手段】一対の導電層に有機化合物層が挟まれた構造を有する有機メモリ素子において、該有機メモリ素子へのデータの書き込みをレーザ照射装置を用いたレーザ照射により行う。また、レーザ発振器から射出したレーザビームは、回折光学素子により複数に分岐され、一度の照射で該有機化合物層上の複数箇所にレーザビームを照射される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】より高機能、高信頼性の記憶素子を有する半導体装置、及びそのような半導体装置を工程、装置を複雑化することなく低コストで、歩留まりよく作製できる技術を提供することを目的とする。

【解決手段】記憶素子の形状として周辺に凹凸部を有するような矩形、単数または複数の屈曲部を有するジグザグ形状、櫛形、内部に開口(空間)を有するような輪状などの形状を用いる。また、短辺の長さに対する長辺の長さの比が大きい長方形、短径に対する長径の比が大きい楕円形なども用いることができる。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】微細・高集積化に対応して多層配線化された半導体集積回路装置において、ヒューズ部の切断による信頼性の低下や製造歩留りの低下を招くことなく、ヒューズ部の上部の開口部の形成時間を短縮して製造時間を短縮する。

【解決手段】半導体基板11上に形成された絶縁膜41と、絶縁膜41上に形成された配線層からなるヒューズ部13を備え、ヒューズ部13の配線層は、少なくとも銅からなる導電用金属層13Aを有する。また、ヒューズ部13の配線層は、絶縁膜41上に形成されたバリア金属層40をさらに備え、導電用金属層13Aは、バリア金属層40上に形成されている。

(もっと読む)

半導体装置及びその動作方法

【課題】チップの内で大きな面積を占めるメモリ領域の低コスト化を図ることにより、チップ全体の製造コストを抑えることを課題とする。

【解決手段】薄膜からなる無線チップが有するメモリ領域において、有線の接続で入力された信号によりデータの書き込みを行い、無線による信号により読み出しを行う。有線の接続による信号に基づき生成されたアドレスを指定する信号により、有機メモリを構成するビット線及びワード線がそれぞれ選択され、選択されたメモリセルに電圧が印加される。このようにして書き込みが行われる。また読み出しは、無線の信号により生成されたクロック信号等により行われる。

(もっと読む)

記憶装置および半導体装置

【課題】製造時以外にデータの書き込み及び消去が可能である不揮発性の記憶装置及びそれを有する半導体装置を提供することを目的とする。また、小型で安価な不揮発性の記憶装置及びそれを有する半導体装置の提供を課題とする。

【解決手段】少なくとも一方が透光性を有する第1の導電層及び第2の導電層と、第1の導電層又は第2の導電層に接する有機化合物層とを有し、有機化合物層は、層内に分散された導電性粒子を有すると共に光異性化しうる部位を有する有機化合物で形成される記憶素子を有する記憶装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】 本発明は、工程、装置を複雑化することなく、要求される特性を有する半導体装置を低コストで、歩留まりよく作製できる技術を提供することを目的とする。

【解決手段】 本発明の半導体装置の一は、基板上に設けられた薄膜回路部と、薄膜回路部と電気的に接続し、基板上及び薄膜回路部上に連続的に設けられた導電層とを有する。また、本発明の半導体装置の作製方法の一は、基板上に薄膜回路部を設置し、基板上及び薄膜回路部上に、流動性を有する導電性材料を含む組成物を付着させ、薄膜回路部と電気的に接続する導電層を形成する。

(もっと読む)

記憶装置および半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを目的とする。また、信頼性が高く、安価な不揮発の記憶装置及びそれを有する半導体装置の提供を課題とする。

【解決手段】本発明の一は、第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される絶縁層とを有し、第1の導電層は凸部を有することを特徴とする記憶装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶装置および半導体装置を安価で提供することを課題とする。

【解決手段】基板上に設けられた、第1のトランジスタと第2のトランジスタとを含む素子形成層と、素子形成層上に設けられた記憶素子と、記憶素子の上方に設けられたセンサ部とを有し、記憶素子は、第1の導電層と有機化合物層と第2の導電層との積層構造を有し、第1の導電層と第1のトランジスタとが電気的に接続され、センサ部と第2のトランジスタが電気的に接続されるように設ける。

(もっと読む)

記憶装置及びその作製方法並びに半導体装置及びその作製方法

【課題】不揮発性であり、作製が簡単であり、追記が可能な記憶装置、半導体装置を提供することを課題とする。

【解決手段】一対の導電層間に組成物層が挟まれた単純な構造の記憶素子を有することを特徴とする。上記特徴により、不揮発性であり、作製が簡単であり、追記が可能な記憶装置を提供することができる。また、複数のメモリセル、第1の方向に延在する複数のビット線、及び第1の方向と垂直な第2の方向に延在する複数のワード線を有することを特徴とする。複数のメモリセルの各々は記憶素子を有する。記憶素子は、ビット線を構成する第1の導電層と、ワード線を構成する第2の導電層と、光学的作用により硬化する組成物層を有することを特徴とする。組成物層は、第1の導電層と第2の導電層の間に設けられている。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性であって、作製工程が簡単であり、追記が可能な記憶回路およびアンテナを有する半導体装置及びその作製方法の提供を課題とし、さらに不本意な無線チップの情報の書き換え防止や、無線チップ自体の偽造防止を図り、無線チップのセキュリティの確保を課題とする。

【解決手段】無線通信信号により情報確認が可能なICタグであり、且つ、ICタグのメモリ(書き換え不可能なメモリ)の情報確認が光学読み取り装置でも可能とすることを特徴とする。本発明のICタグのメモリには情報確認が光学読み取り装置で可能な識別面を有している。

(もっと読む)

半導体装置およびその作製方法

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の有機メモリおよび当該有機メモリを有する半導体装置を提供することを目的とする。また、信頼性が高く、安価な半導体装置の提供を課題とする。

【解決手段】第1の方向に延びた複数のビット線と、第1の方向と垂直な第2の方向に延びた複数のワード線と、記憶素子部を備えたメモリセルと、複数のメモリセルからなるメモリセルアレイとを有し、記憶素子部は、ビット線を構成する導電層とワード線を構成する導電層との間に設けられた有機化合物層を有し、当該有機化合物層に、無機化合物と有機化合物とを混合して設けられた層を設けることを特徴としている。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】フューズ素子に接続されたトランジスタの酸化膜や拡散層が破壊されるのを防止する。

【解決手段】半導体記憶装置は、第1及び第2端子を有し、且つ前記第1端子と前記第2端子との間がレーザーにより電気的に切断されたか否かにより情報を記憶するフューズ素子1と、前記フューズ素子の情報が転送されるノードと、前記フューズ素子1と前記ノードとの間に設けられ、且つ前記フューズ素子1の情報を前記ノードにセットするN型トランジスタ2と、前記第1端子に接続されたアノードとカソードとを含み、且つ前記フューズ素子1が前記レーザーにより切断される際に発生する電荷を逃がすダイオード9とを含む。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】P型領域と、N型領域とを備え、電子キャリア濃度が1018/cm3未満である非晶質酸化物、又は電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質酸化物をN型領域に用いている。電子キャリア濃度が1018/cm3未満である非晶質酸化物又は電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質酸化物からなる第1領域と、第1領域に対してヘテロ接合を形成する第2領域と、を具備する。

(もっと読む)

21 - 40 / 43

[ Back to top ]