Fターム[5F083EP14]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098) | 配置 (221) | ドレインとの重なり (51)

Fターム[5F083EP14]に分類される特許

1 - 20 / 51

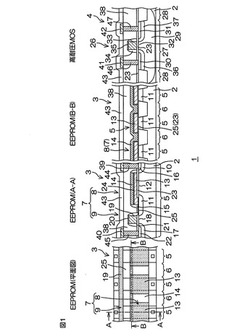

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極を、掘り下げ領域に埋め込んで形成し、ドレイン領域内のトンネル領域と掘り下げ領域に埋め込まれて形成されたフローティングゲート電極の側面との間にトンネル絶縁膜を設ける。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部近傍の領域には、フローティングゲート電極とガード絶縁膜を介してドレイン電極と同電位に固定されたトンネル領域エッジ部ガード電極を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】第2導電型のトンネル領域のフローティングゲート電極のエッジ部の下部に、第1導電型の領域からなるフローティングゲート電極エッジの電界集中防止用領域を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】ドレイン領域内のトンネル領域とフローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、トンネル領域のエッジ近傍のフローティングゲート電極の不純物濃度は、その他の箇所のフローティングゲート電極の不純物濃度に比べて低く設定した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、前記フローティングゲート電極は第1導電型の導電体で形成されている電気的書き換え可能な半導体不揮発性メモリ装置。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】膜質の劣化を抑え、トンネル領域のエッジ部への電界集中を防止し、占有面積を増加することなくトンネル絶縁膜の劣化を抑制して、高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、ドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、第1のトンネル絶縁膜と第2のトンネル絶縁膜が設けられており、第1のトンネル絶縁膜は、トンネル領域のエッジ部近傍に形成されており、第2のトンネル絶縁膜はトンネル領域の前記第1のトンネル絶縁膜か形成されていない領域に形成されており、第1のトンネル絶縁膜の膜厚は、第2のトンネル絶縁膜の膜厚よりも大きく、ゲート絶縁膜よりも小さく形成した。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、メモリ周辺回路の信頼性を向上させることのできる技術を提供する。

【解決手段】メモリ周辺回路領域の高圧系nMISおよび高圧系pMISのゲート絶縁膜14を、半導体基板1の主面上に順次積層された下層の絶縁膜11b、電荷蓄積層CSLおよび上層の絶縁膜11tにより構成し、続いて上層の絶縁膜11t上に積層されたn型の導電膜により高圧系nMISのゲート電極GHnまたは高圧系pMISのゲート電極GHpを構成する。メモリ周辺回路領域の低圧系nMISおよび低圧系pMISのゲート絶縁膜8を、半導体基板1の主面上に形成された酸化シリコン膜により構成する。

(もっと読む)

EEPROM

【課題】データの書き込み効率の向上およびデータの書き込み時間の低減を達成することができる、EEPROMを提供する。

【解決手段】半導体層には、第1不純物領域5、第2不純物領域6、第3不純物領域7、第4不純物領域8および第5不純物領域9が形成されている。第1セレクトゲート11は、第1不純物領域5と第2不純物領域6との間の領域に、第1絶縁膜10を挟んで対向している。第1フローティングゲート12は、第2不純物領域6と第3不純物領域7との間の領域に、第1絶縁膜10を挟んで対向している。第2フローティングゲート19は、第3不純物領域7と第4不純物領域8との間の領域に、第1絶縁膜10を挟んで対向している。第2セレクトゲート20は、第4不純物領域8と第5不純物領域9との間の領域に、第1絶縁膜10を挟んで対向している。

(もっと読む)

EEPROM

【課題】2つのメモリトランジスタに同一のデータを確実に書き込むことができる、W(ダブル)セル方式のEEPROMを提供する。

【解決手段】半導体層には、第1不純物領域8、第2不純物領域9、第3不純物領域10、第4不純物領域11、第5不純物領域12および第6不純物領域13が形成されている。セレクトゲート15は、第1不純物領域8と第2不純物領域9との間の領域に、第1絶縁膜14を挟んで対向している。第1フローティングゲート16は、第2不純物領域9と第3不純物領域10との間の領域および第5不純物領域12に、第1絶縁膜14を挟んで対向している。第2フローティングゲート20は、第3不純物領域10と第4不純物領域11との間の領域および第6不純物領域13に、第1絶縁膜14を挟んで対向している。第5不純物領域12および第6不純物領域13は、第2不純物領域9と接続されている。

(もっと読む)

EEPROMの製造方法

【課題】高い不純物濃度を有する拡散領域によってメモリセルトランジスタと選択トランジスタとが確実に接続されるEEPROMの製造方法を提供する。

【解決手段】半導体基板にメモリセルトランジスタのソース及びドレイン領域を形成し、半導体基板上にメモリセルトランジスタ及び選択トランジスタのゲート電極構造を形成した後に、メモリセルトランジスタのドレイン領域と部分的に重ねて選択トランジスタのソース領域を形成する。

(もっと読む)

半導体記憶装置

【課題】大容量化、低電圧化を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体基板1の表面層のチャネル領域4の両側に、ソース2及びドレイン3が形成されている。半導体基板1のチャネル領域4上に、トンネル絶縁膜5が形成されている。トンネル絶縁膜5の上に、フローティングゲート電極6が、ソース2及びドレイン3のいずれにも重ならないように配置されている。フローティングゲート電極6を覆うように、チャネル領域4の上方にゲート絶縁膜7が形成されている。ゲート絶縁膜7の上に、ソース2及びドレイン3に接するかまたは部分的に重なるようにコントロールゲート電極8が配置されている。フローティングゲート電極6に電荷が注入された状態において、チャネル領域4とコントロールゲート電極8との間に外部から電圧を印加しない状態のときに、フローティングゲート電極6のフェルミ準位がチャネル領域の禁制帯の中に位置する。

(もっと読む)

半導体装置

【課題】セルサイズのさらなる縮小を図ることができる、半導体装置を提供すること。

【解決手段】半導体層2に、トレンチ5が形成されている。半導体層2の表層部には、第1拡散領域3およびドレイン領域が形成されている。第1拡散領域3は、トレンチ5に対して所定方向の一方側に形成され、トレンチ5に隣接している。第2拡散領域6は、所定方向においてトレンチ5に対して第1拡散領域3と反対側に形成され、トレンチ5に隣接している。トレンチ5の底面および側面上には、第1絶縁膜8が形成されている。第1絶縁膜8上には、フローティングゲート11が設けられている。フローティングゲート11は、第1絶縁膜8を挟んで、トレンチ5の底面および側面と対向している。フローティングゲート11上には、第2絶縁膜12が形成されている。第2絶縁膜12上には、コントロールゲート13が設けられている。

(もっと読む)

1 - 20 / 51

[ Back to top ]