Fターム[5F083GA21]の内容

Fターム[5F083GA21]に分類される特許

781 - 791 / 791

不揮発性半導体メモリ装置及びその製造方法

【課題】 トンネル絶縁膜を欠陥が生成されにくい高品質な絶縁膜にすることができ、書き込み・消去電圧を低減して、素子特性や信頼性の向上をはかる。

【解決手段】 第1導電型の半導体基板11の主面上に第1のゲート絶縁膜13を介して選択的に形成されたフローティングゲート電極14と、フローティングゲート電極14上に第2のゲート絶縁膜15を介して形成されたコントロールゲート電極16と、各ゲート電極に対応して基板11の主面に形成された第2導電型のソース・ドレイン領域18とを具備してなる不揮発性半導体メモリ装置であって、第1のゲート絶縁膜13は、シリコン窒化膜13aをシリコン酸化膜13b,13cで挟んで形成された3層構造であり、且つシリコン窒化膜13aは三配位の窒素結合となっている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 強誘電体キャパシタをその下層に含まれる水素から保護する。

【解決手段】 層間絶縁膜8上に第1の水素バリア膜10及び中間層11を形成する。中間層11上に強誘電体キャパシタ13を形成し、強誘電体キャパシタ13の上面及び側面、ならびに中間層11上を含む全面上に、第2の水素バリア膜14を形成する。次いで第2の水素バリア膜14及び中間層11を、少なくとも強誘電体キャパシタ13の上面及び側面に位置する部分を残して除去する。次いで第2の水素バリア膜14上、第2の水素バリア膜14及び中間層11それぞれの側面上、ならびに第1の水素バリア膜10上に第3の水素バリア膜15を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 強誘電体キャパシタを水素から保護する。

【解決手段】 下地膜8上に、下部電極10a、強誘電体膜10b及び上部電極10cをこの順に積層した強誘電体キャパシタ10を形成する工程と、強誘電体キャパシタ10の上面及び側面を、水素バリア膜11で覆う工程と、水素バリア膜11上及び下地膜8上に第1の層間絶縁膜12を形成する工程と、第1の層間絶縁膜12上に上部SBT膜13を形成する工程と、上部SBT膜13上に第2の層間絶縁膜14を形成する工程とを具備する。下地膜8上に下部SBT膜を形成する工程を更に具備してもよい。この場合、強誘電体キャパシタ10は下部SBT膜上に形成される。

(もっと読む)

積層抵抗可変メモリ・ディバイスおよびその製造方法

【構成】この発明は,記憶保持特性およびスイッチング特性を高めた抵抗可変メモリ素子を提供する方法および装置に関する。この発明によれば,好ましくはGexSe100-x組成を有する2つのカルコゲナイド・ガラス層(17,20)と上部,下部電極(14,22)との間に,好ましくはセレン化銀層である少なくとも1つの金属含有層(18)を設けた抵抗可変メモリ素子が提供される。少なくとも第2のカルコゲナイド・ガラス層(20)の上に,好ましくは銀層である金属層(50)を設け,前記銀層の上に導電性接着層(30)を配置する。この発明の他の実施形態によれば,第1のカルコゲナイド・ガラス層(17)と,前記第1のカルコゲナイド・ガラス層の上にある銀層(40’)と,前記銀層の上にあるセレン化銀層(18)と,前記セレン化銀層の上にある第2のカルコゲナイド・ガラス層(20)とを有する抵抗可変メモリ素子が提供され,前記第2のカルコゲナイド・ガラス層の上に第2の銀層が任意に設けられる。 (もっと読む)

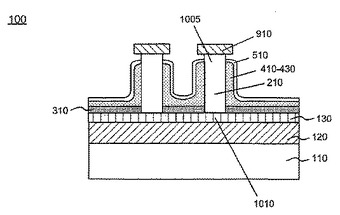

フラッシュメモリデバイス

メモリデバイス(100)は、導電構造(210)、複数の誘電層(410−430)、及び、制御ゲート(510)を含む。誘電層(410−430)は導電構造(210)の周りに形成され、制御ゲート(510)は誘電層(410−430)上に形成される。導電構造(210)の一部はメモリデバイス(100)のドレイン領域(1005)として機能し、また、誘電層(410−430)の少なくとも1つは、メモリデバイス(100)の電荷蓄積構造として機能する。誘電層(410−430)は、酸化物−窒化物−酸化物層を含む。  (もっと読む)

(もっと読む)

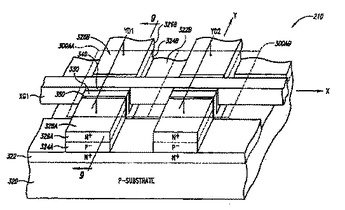

縦型スプリットゲートNROMメモリ装置及びその形成方法

【課題】NROMセルの利点と縦型メモリセルの利点とを備えるメモリデバイスを提供する。

【解決手段】スプリットゲート縦型NROMメモリセル(1890)は、複数の酸化物柱状体(1830、1831)から構成される。複数の酸化物柱状体の各々の上部にはソース/ドレイン領域(1840、1841)が形成される。溝部が、酸化物柱状体の各対の間に形成される。ポリシリコン制御ゲート(1800)が、酸化物柱状体の対の間の溝部に形成される。ポリシリコンプログラムゲート(1805、1806)が、制御ゲートと各酸化物柱状体との間に形成される。プログラムゲートは、各酸化物柱状体の側壁に沿って延在する。ゲート絶縁層(1802、1803)が、各プログラムゲートとその近傍の酸化物柱状体との間に形成される。各ゲート絶縁層は、少なくともひとつの電荷を捕獲する電荷捕獲構造を有する。一実施形態において、ゲート絶縁構造は、酸化物−窒化物−酸化物の層である。中間絶縁層(1822、1824)が、プログラムゲートと制御ゲートとの間に形成される。

(もっと読む)

不揮発性メモリを電荷トラッピングするための改善された消去および読み取り手法

本発明は、不揮発性電荷トラッピング型メモリデバイスのアレイを動作させるための方法を述べる。方法は、アレイの実質的に全ての不揮発性メモリデバイスのブロック消去ステップの前に、アレイの実質的に全ての不揮発性メモリデバイスにブロック書き込みするステップを備える。本発明の利点は、これを行なうことにより、さらなる電荷トラッピング型不揮発性メモリデバイスを、基準セルとして使用できることであり、基準セルは、アレイ内のメモリセルのブロック書き込みおよびブロック消去によって書き込みおよび消去され、したがって、基準セルは、アレイ内のメモリセルと同一の繰り返し履歴を示す。この特性を用いて、読み取りパラメータを目盛りセルの経年変化に適応させることができる。また、対応するデバイスも、提供される。  (もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

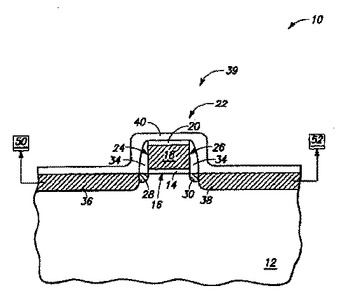

耐久性が改善された分離トランジスタメモリ及びその製造方法

本発明は、フラッシュメモリ装置のような不揮発性メモリ装置に使用されるフローティングゲートトランジスタ構造を有する。1つの実施の形態において、システムはCPUとメモリ装置とを有し、該メモリ装置は複数のメモリセルを有するアレイを具備する。メモリセルは複数の柱状構造とこれら柱状構造間に挿入され、これら柱状構造のうちの1つに近接するフローティングゲート構造とを有する。他の実施の形態において、メモリ装置10は、複数のメモリセルを有するアレイを具備する。メモリセルは隣接する複数のFETを有し、これらFETは、ソース/ドレイン領域と共通のフローティングゲート構造を有し、該フローティングゲート構造は、1つのFETのソース/ドレイン領域から第1間隔だけ離間し、且つ、他のFETのソース/ドレイン領域から第2間隔だけ離間している。さらに他の実施の形態において、メモリ装置は、基板上に複数の柱状構造を配置し、これら複数の柱状構造間にフローティングゲートを、これら柱状構造のうちの1つに近接するように挿入することによって形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

半導体記憶装置

【課題】 ゲート絶縁膜の劣化を防止すると共に、浮遊ゲート内のキャリアの電荷量を正確に制御できるようにする。さらに、書き込み時の消費電力を不要にする。

【解決手段】 開示されている半導体記憶装置は、浮遊ゲート6に一部分が接すると共に他部分がP型シリコン基板1に接するようにモット絶縁体7を設け、このモット絶縁体7に金属−絶縁相転移を生じさせる。そして、浮遊ゲート6に対してキャリアである電子の注入又は放出を行う場合、ゲート酸化膜5を通じてではなく、モット絶縁体7の金属相を通じてキャリアの注入又は放出を行う。

(もっと読む)

781 - 791 / 791

[ Back to top ]