Fターム[5F083JA37]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | Cu、Cu系合金 (2,136)

Fターム[5F083JA37]に分類される特許

2,001 - 2,020 / 2,136

磁気ランダムアクセスメモリ

【課題】磁気抵抗効果素子をリソグラフィの解像限界以下のシャープな輪郭の形状にすることで、磁気特性の向上を図る。

【解決手段】磁気ランダムアクセスメモリは、複数のコーナーを有する平面形状であり、一つ以上のコーナーにおける曲率半径が20nm以下である磁気抵抗効果素子MTJを具備する。

(もっと読む)

記憶装置

【課題】状態遷移閾値に非対称なヒステリシスループが生じている抵抗変化素子を用いた場合であっても、その抵抗変化素子からの情報読み出しにあたって、誤書き込みや記憶情報破壊等が生じることなく、しかもその情報読み出し時における安定性を十分に確保する。

【解決手段】2つの電極11,12の間に記録層13を有してなり、前記電極11,12に極性の異なる電位を印加することにより前記記録層13の抵抗値が可逆的に変化する抵抗変化素子において、状態遷移閾値の絶対値が高抵抗状態から低抵抗状態への変化時と前記低抵抗状態から前記高抵抗状態への変化時とで互いに異なる場合に、前記記録層13の抵抗値を検出するための読み出し信号を、前記状態遷移閾値の絶対値が大きいほうの極性で、かつ、当該絶対値よりも小さい値で印加する。

(もっと読む)

記憶素子及びメモリ

【課題】 スピン注入効率を向上することにより、書き込みに要する電流値を低減することができる記憶素子を提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層32の上下に、中間層14,18を介して磁化固定層31,33が設けられ、これら磁化固定層31,33のそれぞれ記憶層32に最も近い強磁性層13,19の磁化M13,M19の向きが略平行であり、記憶層32が非磁性導体層16を介して積層された複数層の強磁性層15,17から成り、記憶層32の最上層の強磁性層17の磁化M17と最下層の強磁性層15の磁化M15とが、互いに向きが反平行であり、積層方向に電流を流すことにより、記憶層32の磁化M15,M17の向きが変化して、記憶層32に対して情報の記録が行われる記憶素子3を構成する。

(もっと読む)

半導体装置

【課題】プログラム電圧が低下された場合、e-フューズを確実にプログラムすることが困難であった。

【解決手段】フューズ素子11は、多結晶シリコン層と金属シリサイド層が積層されている。MOSトランジスタ19は、フューズ素子に接続され、フューズ素子にプログラム電圧を供給する。プログラム電圧がMOSトランジスタを介して供給された際、フューズ素子を融解するために必要な最低抵抗値Rminにおけるジュール熱Jの最小値をJO、最高抵抗値Rmaxにおいて温度を上昇させるに必要なジュール熱Jの最小値をJ1とし、フューズ素子の最低抵抗値Rminにおけるジュール熱をJ(Rmin)、フューズ素子のプログラム時の最高抵抗値Rmaxにおけるジュール熱をJ(Rmax)とした場合、J(Rmin)>JO、且つJ(Rmax)>J1(JO>J1)を満たしている。

(もっと読む)

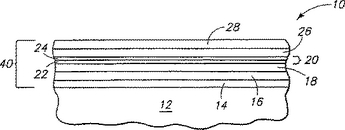

薄フィルムおよび、ECAE−ターゲットを使用して薄フィルムを形成する方法

本発明は、バリヤー層を形成するための方法を含む。材料はECAEターゲットからアブレートされ、基体表面上にわたって1%未満またはそれと同等の1シグマの厚みバラツキを有する層を形成する。本発明は、トンネル接合を形成する方法を含む。薄フィルムは、第1の磁性層と第2の磁性層との間に形成される。その薄フィルム、第1の磁性層および/または第2の磁性層は、ECAEターゲットから材料をアブレートすることにより形成され、非ECAEターゲットを使用して形成された対応する層と比較して改善された層厚み均一性を呈する。本発明は、物理蒸着ターゲットおよびそのターゲットを使用して形成された薄フィルムを含む。そのターゲットは、アルミニウムとGa、ZrおよびInから選択された少なくとも1つの合金化元素との合金を含有する。得られたフィルムは、その薄フィルム上にわたって1.5%未満の1シグマの厚みバラツキを有する。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 情報の読み出し時に、チャネル領域からの多数キャリアの放出による情報の変化と情報の保持時間の短縮を防止し、高速動作の可能な半導体記憶装置を提供する。

【解決手段】 半導体基板3上にチャネル領域4を直立に設け、このチャネル領域4の少なくとも一端にソース/ドレイン層5(6)を設け、チャネル領域4の両側面にゲート絶縁膜7、8を介して第1及び第2のゲート電極9、10を設ける。そして、チャネル領域4に情報の書き込みを行い、その情報の読み出しは、チャネル領域4とソース/ドレイン層5、6間のpn接合を逆方向バイアス状態にしておき、第1及び第2のゲート電極9、10に所定電位を印加することにより両ゲート電極9、10間に流れるトンネル電流量を検知することによって行う。

(もっと読む)

半導体記憶装置

【課題】追加の工程を必要とすることなく強誘電体膜への水素拡散を防止することができる構造の強誘電体キャパシタを備える半導体記憶装置を提供すること。

【解決手段】半導体基板上に形成された層間絶縁膜と、層間絶縁膜中に形成され、一端が半導体基板に電気的に接続されたコンタクトプラグと、層間絶縁膜上に形成され、第1の電極と、強誘電体膜と、コンタクトプラグの他端に電気的に接続された第2の電極と、からなる強誘電体キャパシタと、強誘電体キャパシタを被覆すると共に、第1の電極を露出する開口部を有する絶縁膜と、強誘電体キャパシタ及び絶縁膜を被覆し、開口部によって露出された第1の電極と電気的に接続された配線膜であって、導電性を有しかつ水素拡散防止機能をも有する材料からなる配線膜と、を備えた半導体記憶装置。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化に有利で信頼性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、ゲート電極上に金属層31を備えたトランジスタSTと、順次設けられた第1バリア膜23、第1絶縁層24、第2バリア膜25、第2絶縁層26と、前記第2バリア膜に第1幅W1で開口し第1方向に伸びる溝と、前記第2絶縁層を貫通して前記第2バリア膜中に底部40を有し前記底部が前記第1方向に交差する第2方向に前記第1幅よりも大きい第2幅W2を有するコンタクトホール上部39−1と、前記コンタクトホール上部から前記溝を介して前記第1絶縁層および第1バリア膜を貫通して前記拡散層上に設けられ前記第2方向に上面が前記1幅W1を有するコンタクトホール下部39−2と、前記コンタクトホール上部内および前記コンタクトホール下部内に連続して導電体が埋め込まれたコンタクト39を具備する。

(もっと読む)

強誘電体キャパシタ及びその製造方法

半導体基板(11)上にMOSトランジスタ(14)を形成し、更にWプラグ(24)の埋込までの工程を行った後、全面にIr膜(25a)、IrOx膜(25b)、PZT膜(26)及びIrOx膜(27)を順次形成する。このとき、PZT膜(26)の組成に関し、Pb量をZr量及びTi量に対して過剰にする。次に、Ir膜(25a)、IrOx膜(25b)、PZT膜(26)及びIrOx膜(27)を加工した後、アニールを行うことにより、IrOx膜(27)の形成時等にPZT膜(26)に生じた損傷を回復させると共に、IrOx膜(27)中のIrをPZT膜(26)中に拡散させる。この結果、PZT膜(26)中に拡散したIrは、IrOx膜(27)とPZT膜(26)との界面及びPZT膜(26)中の結晶粒界に集合し、これらにおけるIr濃度が結晶粒内よりも高くなる。  (もっと読む)

(もっと読む)

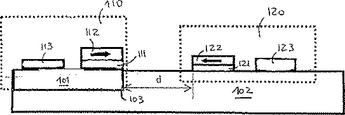

スピン検出磁気メモリ

【課題】 スピン極性化電子の注入及び/又は検出が著しく改善されたスピン検出磁気メモリを提供する。

【解決手段】 本発明のメモリは、二つの隣接領域が形成する半導体接合部(103)上に配置され、該第1と第2の領域(101,102)がそれぞれ第1種と第2種の導電性を呈し、前記接合部(103)の各側に配置した第1と第2の接続セル(110,120)を備え、各セルが磁化モジュール(111と112,121と122)を備えるスピン検出磁気メモリであって、前記セルのうちの少なくとも一つが前記磁化モジュールに加えバイアス電極(113,123)を含む、ことを特徴とする。  (もっと読む)

(もっと読む)

薄膜キャパシタ

【課題】

薄膜キャパシタに発生する応力を分散・低減して、リーク電流特性の劣化を抑え、歩留まりや信頼性の向上を図る。

【解決手段】

薄膜キャパシタの上部電極18の端部であって、直線的な傾斜20Aを有するように、層間絶縁膜20が形成される。すなわち、A点から上部電極18の端部までの距離をLとし、A−Bの主面上における距離をWとしたときに、W/2>Lの大小関係が成り立つように、層間絶縁膜20の傾斜20Aが形成される。これにより、該界面において薄膜キャパシタ側に生ずる応力が傾斜に沿って分散され、薄膜キャパシタの外に逃げるようになる。従って、薄膜キャパシタ内部に生ずる応力場の集中が緩和され、更にはリーク電流特性の劣化が抑制されるようになる。

(もっと読む)

高密度不揮発性メモリを製作するための改良された方法

【課題】密度の高い三次元モノリシックメモリを製作するための改善された方法を開示する。

【解決手段】本方法は、望ましくはタングステンから成る導体を形成し、次いで充填と平坦化処理を行い;導体の上方に、好ましくは2つのダイオード部分とアンチヒューズを備えた半導体要素を形成し、次いで充填と平坦化処理を行い;多階層のメモリとして導体と半導体要素を継続的に形成する段階を含んでいる。処理工程の配設と材料の選択によって、各メモリセルのアスペクト比を小さくし、これによって空隙充填の信頼性を改善し、エッチングによるアンダーカットを防止している。  (もっと読む)

(もっと読む)

低消費電力磁気メモリ及び磁化情報書き込み装置

【課題】超低消費電力な高集積磁気メモリを提供する。

【解決手段】自由層311と、自由層の膜厚方向に形成された第一の固定層313と、自由層と第一の固定層との間に形成された絶縁障壁層312とを有する第一の素子部と、前記自由層311と、自由層の膜面方向に形成された第二の固定層315と、自由層と第二の固定層との間に形成された非磁性層314とを有する第二の素子部を備える。磁化情報の書き込みに際しては第二の素子部の膜面方向に電流Iwを流し、磁化情報の読み出しに際しては第一の素子部の膜厚方向に電流IRを流す。

(もっと読む)

記憶素子

【課題】 比較的単純な層構成でスピン注入磁化反転効率を上げることができ、微細加工が容易であり、高密度に集積可能な記憶素子を提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層17と、この記憶層17に対して非磁性層16を介して設けられた磁化固定層21とを少なくとも有し、非磁性層16を通じて、記憶層17と磁化固定層21との間に電流を流すことにより情報の記録が行われ、記憶層17に対して、磁化固定層21とは反対側に、非磁性層18を介して磁化の向きを変化させることが可能な磁化自由層19が設けられている記憶素子10を構成する。

(もっと読む)

相変化材料および並列ヒータを有する電子デバイス

電子デバイス(1,100)は、第1相と第2相の間で変化することが可能な相変化材料を備える抵抗器(7,107)を有するボディ(2,102)を持つ。抵抗器(7,107)は、相変化材料が第1相にあるときは第1電気抵抗を、相変化材料が第2相にあるときは、第1電気抵抗とは異なる第2電気抵抗を有する。ボディ(2,102)は、第1相から第2相への遷移を可能にする電流を伝えることができる発熱体(6,106)を、さらに有する。発熱体(6,106)は、抵抗器(7,107)と並列して配置される。  (もっと読む)

(もっと読む)

ポリマー電極を有する強誘電性ポリマーメモリ装置及びその製造方法

導電性ポリマー電極を有する強誘電体メモリモジュールの製造方法と該方法に従って製造される強誘電体メモリモジュールとが開示される。強誘電性ポリマーメモリモジュールは、内部にトレンチを規定するILD層(102);トレンチ内に配置された第1電極層(104);第1電極層(104)上に配置された第1導電性ポリマー層(106);第1導電性ポリマー層(106)上に配置された強誘電性ポリマー層(108)を含む第1レイヤーセットを有する。該モジュールは更に、内部にトレンチを規定するILD層(114);ILD層(114)のトレンチ内に配置された第2導電性ポリマー層(112);第2導電性ポリマー層(112)上に配置された第2電極層(116)を含む第2レイヤーセットを有する。第1導電性ポリマー層(106)及び第2導電性ポリマー層(112)は、電極層(104、116)と強誘電性ポリマー層(108)との間に反応障壁及び/又は拡散障壁をもたらすように電極層(104、116)を覆う。  (もっと読む)

(もっと読む)

相変化材料を備える電子デバイス

電子デバイス(1,100)は、第1相と第2相の間で変化することが可能な相変化材料を備える抵抗器(7,250)を有するボディ(2,101)を持つ。抵抗器(7,250)は、相変化材料が第1相か第2相かに依存する電気抵抗を有する。抵抗器(7,250)は、第1相から第2相への遷移を可能にする電流を伝えることができる。相変化材料は、高速成長材料(fast growth material)であり、式Sb1−cMcの組成物としても良く、ここで、cは、0.05≦c≦0.61を満たし、Mは、Ge、In、Ag、Ga、Te、ZnおよびSnの群から選択された1つまたは複数の元素であり、あるいは、式SbaTebX100−(a+b)の組成物としても良く、ここで、a、bおよび100−(a+b)は、1≦a/b≦8および4≦100−(a+b)≦22を満たす原子百分率を表わし、Xは、Ge、In、Ag、GaおよびZnから選択された1つまたは複数の元素である。  (もっと読む)

(もっと読む)

電子素子およびこの電子素子を用いた記録方法

【課題】大記憶容量と読み書き速度とを有し、製造コストが安く、半導体メモリ並みにコンパクトである電子素子を得る。

【解決手段】電流を印加した時にエレクトトマイグレーションによって少なくとも形状あるいは組成が変化する記憶コア101を有する電子素子であって、電流印加のための2つの電極102,103と表面電位あるいは電気抵抗あるいは接合抵抗の変化を感知する電極104を有する。

(もっと読む)

磁気電子デバイスに使用される磁束集中系路を作製するための方法

磁気電子デバイスに使用される磁束集中系路(62)を作製するための方法が提供される。本方法は、基板(12)に形成されたビットライン(10)を設ける工程と、上記ビットライン(10)及び上記基板(12)を覆う第1材料層(24)を形成する工程とからなる。エッチングは、上記第1材料層(24)内に深溝(52)を形成するように実施され、クラッド層(56)が、上記深溝(52)内に堆積される。バッファ材料層(58)が、上記クラッド層(56)を覆って形成され、上記バッファ材料層(58)の一部及び上記クラッド層(56)の一部が除去される。  (もっと読む)

(もっと読む)

記憶素子及びメモリ

【課題】 スピン注入効率を向上することにより、書き込みに要する電流値を低減することができる記憶素子を提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層17の上下に、中間層16,18を介して磁化固定層31,32が設けられ、それぞれの中間層16,18がいずれも絶縁層から成り、記憶層17の上下の磁化固定層31,32のそれぞれ記憶層17に最も近い強磁性層15,19の磁化M15,M19の向きが互いに反対向きであり、記憶層17の上下2つの中間層16,18が面積抵抗値に有意差を有しており、積層方向に電流を流すことにより記憶層17の磁化M1の向きが変化して、記憶層に情報が記録される記憶素子3を構成する。

(もっと読む)

2,001 - 2,020 / 2,136

[ Back to top ]