Fターム[5F083KA10]の内容

Fターム[5F083KA10]に分類される特許

1 - 20 / 22

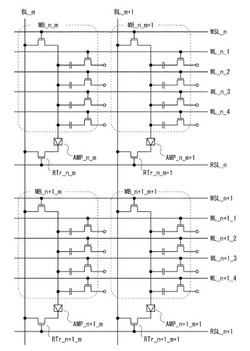

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

3次元半導体装置の配線構造体

【課題】集積度及び信頼性を共に向上させた3次元半導体装置を提供する。

【解決手段】3次元半導体装置の配線構造が提供される。3次元半導体装置は3次元基板上に2次元的に配列された積層構造体、第1配線を含み、積層構造体の上部に配置される第1配線層及び第2配線を含み、第1配線層の上部に配置される第2配線層を含み、積層構造体各々は順次に積層された複数の下部ワードラインを含む下部構造体及び順次に積層された複数の上部ワードラインを含み、下部構造体の上部に配置される上部構造体を含み、第1配線各々は下部ワードラインの内の何れか1つに連結し、第2配線各々は上部ワードラインの内の何れか1つに連結する。

(もっと読む)

不揮発性半導体記憶装置

【課題】従来に比してメモリセルの積層数を抑えながら記憶密度を高めることができる不揮発性半導体記憶装置を提供する。

【解決手段】柱状の半導体膜131の側面に形成される電荷蓄積層133、および電荷蓄積層133上に形成されるゲート電極膜134を備えるトランジスタが半導体膜131の高さ方向に複数設けられるメモリストリングスMSが、半導体基板101上に略垂直にマトリックス状に配置され、第1の方向に配置されたメモリストリングスMSの同じ高さのトランジスタのゲート電極膜134間が接続された不揮発性半導体記憶装置において、第1の方向に隣接するメモリストリングスMSの少なくとも最上層のトランジスタ形成位置における半導体膜131間の距離は、電荷蓄積層133の厚さの2倍よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

クロスポイント型半導体メモリ装置及びその製造方法

【課題】1つのメモリセルの大きさが4F2を下回る大きさである構成、構造を有するクロスポイント型半導体メモリ装置を提供する。

【解決手段】クロスポイント型半導体メモリ装置は、第1の方向に延びる複数の第1の配線41A、41B;第1の配線とは垂直方向に異なる所に位置し、第1の方向とは異なる第2の方向に延びる複数の第2の配線42;及び、第1の配線と第2の配線とが重複する領域に設けられたメモリ部43から構成され、奇数番目の第1の配線41Aと、偶数番目の第1の配線41Bとは、上下方向に異なる層間絶縁層21,22上に配置されている。

(もっと読む)

ブースト電圧クランプを改善するためのペアビットラインプログラミング

プログラミング技法は、プログラム外乱を回避するために阻止されたチャネルのクランプブースト電位を上昇させる選択ビットラインパターンを使用してプログラミングすることによって、不揮発性記憶素子のセットでのプログラム外乱を削減する。1つの態様では、隣接するビットラインの交互のペアを第1のセット及び第2のセットにグループ化する。二重プログラミングパルスが、選択されたワードラインに印加される。ビットラインの第1のセットは、第1のパルスの間にプログラミングされ、ビットラインの第2のセットは、第2のパルスの間にプログラミングされる。次に、全てのビットラインに検証動作が実行される。ある特定のビットラインが阻止されると、その隣接ビットラインの少なくとも1つも阻止され、その特定のビットラインのチャネルが十分にブーストされる。別の態様は、2ビットラインおきに別々にプログラミングする。修正されたレイアウトによって、ビットラインの隣接するペアは、奇数−偶数検出回路を使用して検出できる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】メモリチップの縮小化およびデータの高密度化を可能とする半導体記憶装置を提供する。

【解決手段】ワード線と、第1のビット線と、第2のビット線と、プレート線と、第1の強誘電体キャパシタと、第1の強誘電体キャパシタのそれぞれに対応して設けられ、ワード線をゲートとするセルトランジスタと、第2の強誘電体キャパシタと、第1のビット線または第2のビット線を介して第1の強誘電体キャパシタに記憶されたデータまたは第2の強誘電体キャパシタに記憶されたデータを検出し、あるいは、第1の強誘電体キャパシタまたは第2の強誘電体キャパシタにデータを書き込むセンスアンプとを備え、第1の強誘電体キャパシタおよびセルトランジスタは、第1のビット線とプレート線との間に直列に接続され、第2の強誘電体キャパシタは、第2のビット線とワード線との間に接続されている。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】互いに隣接するビットライン間に形成される寄生キャパシタの容量を減少させてフラッシュメモリ素子の動作速度を改善すると共にコンタクトプラグにボイドが発生する現象を改善する半導体メモリ素子及びその製造方法を提供する。

【解決手段】半導体メモリ素子は、ゲートパターン210間の半導体基板200上に形成されたコンタクトプラグ214a、214b,コンタクトプラグとそれぞれ連結され、一方の方向と他方の方向に延びた第1及び第2の導電性パッド220,320、第1及び第2の導電性パッドの延びた縁部の上部に互いに異なる高さでそれぞれ形成された第1及び第2のパッドコンタクトプラグ228,328、第1のパッドコンタクトプラグ228とそれぞれ連結される第1のビットラインBL1、及び第2のパッドコンタクトプラグ328とそれぞれ連結される第2のビットラインBL2を含む。

(もっと読む)

半導体集積回路装置

【課題】設計寸法のさらなる微細化に対応できるようにする。

【解決手段】シリコンからなるチップ10の主面上には、512kbitの容量を持つ第1のSRAMブロック11と、128kbitの容量を持つ第2のSRAMブロック12とが集積化されている。第1のSRAMブロック11を構成する1ビット当たりのセルの面積を2.4μm2 とし、第2のSRAMブロック12を構成する1ビット当たりのセルの面積を共に3.5μm2 としている。これにより、第1のSRAMブロック11は、ビットセルを構成する複数のトランジスタの各ゲートが延びる方向が特定の方向に設定されており、設定された方向において、リソグラフィ条件が最適化されている。その結果、ビットセル面積は、ビットセルを構成するトランジスタのゲート幅方向に依存して異なるように設定されている。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

ワード線ストラップ回路

【課題】DRAMの機能的歩留まりを向上させるワード線ストラップ回路。

【解決手段】第1の下側導体の一方の端が第1の信号源に結合される。第1の上側導体が2つの端を持ち、隣接する下側導体の間の許容し得る間隔より小さい距離だけ、第1の下側導体から隔たっている。第1の上側導体の一方の端が第2の信号源に結合される。第2の上側導体が2つの端を持っている。第2の上側導体の一方の端が第1の下側導体の別の端に結合され、第1の信号源からの信号を受け取る。第2の下側導体が2つの端を持ち、隣接する下側導体の間の許容し得る間隔より小さい距離だけ、第2の上側導体から隔たっている。第2の下側導体の一方の端が、第1の上側導体の別の端に結合され、第2の信号源からの信号を受け取る。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMセルにおける放射線損傷による不具合を防止する。

【解決手段】

第2、第3層間絶縁膜103、104を両側面とし、第1層間絶縁膜102の主面102aを底面とする開口111が構成されている。開口111の内側面には、ノード電極である下部電極105が形成されている。下部電極105は、キャパシタの下部電極として機能すると同時に、SRAMセルのノード配線としても機能する。第3層間絶縁膜104の主面104a及び開口111内側面の下部電極105上には容量絶縁膜106が形成されている。開口111の内部及び開口111周囲の第3層間絶縁膜104上には上部電極107が形成されている。埋め込まれた上部電極107は、開口111の周囲の第3層間絶縁膜104上にも形成され、キャパシタの上部電極として機能する。開口111の間口部分より上に形成される上部電極107の幅L1は、開口111の幅L2よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】高記憶容量化が可能な半導体装置およびその製造方法を提供する。

【解決手段】基板10上にビットライン層15a、15b、15cに上下を挟まれた複数のチャネル層14a、14bが積層された積層構造17と、積層構造17中にチャネル層14a、14bに形成された溝部18の側方に設けられたゲート電極30と、ゲート電極30とチャネル層14a、14bとの間に設けられた電荷蓄積層24と、を有する半導体装置。

(もっと読む)

スタックにおける電気的相互垂直接続

【課題】基板により支持され、又はサンドイッチ自己支持構造を形成した少なくともスタックされた2層を有するメモリ及び/又はデータ処理装置の提供である。

【解決手段】前記層は、メモリ及び/又は前記層間及び/又は前記基板における回路に対する相互接続を有する処理回路を備え、前記層は、連続する層が前記装置の少なくとも1エッジ上にジグザク構造を形成するように相互に配列され、少なくとも1エッジ電導体を一度に1層のエッジを越え、1ステップ下がって設けて、前記スタックにおいて次に続く層のいずれかにおける導電体に対する接続を可能にする。この種の装置を製造する方法は、複数の層がジグザク構造を形成するように1度に1層を連続的に前記複数の層に付加する工程と、1以上の層に少なくとも1電気接触パッドを設けて1以上の中間層エッジ・コネクタに連結させる工程を備えている。

(もっと読む)

強誘電体素子を適用した半導体メモリ装置及びそのリフレッシュ方法

【課題】本発明は、不揮発性特性を有する1T-FET型(1 transistor-Field Effect Transistor Type)強誘電体メモリセルをDRAMに適用して電源のオフ時にもリフレッシュ情報を失わず、データ維持(Retention)特性を向上させることができるようにする技術を開示する。

【解決手段】本発明は、1-T(One-Transistor) FET(Field Effect Transistor)型メモリセルを含む半導体メモリ装置において、ロー方向に配列された複数個のワードライン、及び複数個のワードラインと垂直の方向に配列された複数個のビットラインを含み、メモリセルは複数個のビットラインのうち互いに隣接したビットライン対の間に連結され、ワードラインと前記ビットライン対に印加される電圧に応じて強誘電体層の極性が変化しデータの読取り/書込みが行なわれる。

(もっと読む)

半導体素子の金属配線とその形成方法

【課題】奇数番(odd)の列と偶数番(even)の列に位置するビット線間のローディングキャパシタンスを減少させ、ビット線どうしが接触するビットラインブリッジの発生を防止できる半導体素子の金属配線とその形成を提供する。

【解決手段】第1金属配線と第2金属配線とを異なる層に段差をもって形成する。そうすることで第1,第2金属配線どうしの間隔が拡大し、配線間のロードキャパシタンスを減少させ、配線どうしの接触による相互干渉でいわゆるブリッジが発生するのを有効に防止できる。たとえば、第1金属配線が奇数番の列に位置するオードビット線115であり、第2金属配線が偶数番の列に位置するイーブンビット線121であるような場合、オードビット線115とイーブンビット線121を異なる層に段差をもって形成する。それによって、オードビット線115とイーブンビット線121との距離が拡大されるので、ビットラインブリッジの発生を防げる。

(もっと読む)

半導体記憶装置

【課題】安定且つ高速にロウ方向の全セルを同時に読み出すことを可能とする。

【解決手段】メモリセルアレイ1には、複数のワード線WL0〜WL31と、複数のビット線BL0e〜BL8koと、複数のワード線及び複数のビット線に接続された複数のメモリセルMCが配置されている。複数のソース線SRC0e〜SRC8koは、複数のビット線のそれぞれに沿って配置され、データの読み出し時に複数のビット線のそれぞれに接続される。

(もっと読む)

フラッシュメモリ素子のビットライン形成方法

【課題】ビットラインの間隔が最小化されると同時にビットラインの静電容量が増加することを防止してセンシングタイムを減らす。

【解決手段】半導体素子の形成された半導体基板10上にドレインコンタクトホールに埋め込まれると同時に第1層間絶縁膜12の上部に所定の厚さ形成されるように第1金属物質14を形成する段階と、前記第1層間絶縁膜12の上部に所定の厚さ形成された第1金属物質14をパターニングし、第1金属配線の奇数番目に配置される第1金属層、及び前記第1金属層の間に位置するランディングパッドを形成する段階と、前記第1金属層及びランディングパッドが形成された結果物の全面に第2層間絶縁膜16を形成した後パターニングして、前記ランディングパッドを露出させるトレンチを形成する段階と、前記トレンチの内部にのみ第2金属物質18が埋め込み、第1金属配線の偶数番目に配置される第2金属層を形成する段階とを含む。

(もっと読む)

1 - 20 / 22

[ Back to top ]