Fターム[5F083NA04]の内容

Fターム[5F083NA04]に分類される特許

1 - 20 / 42

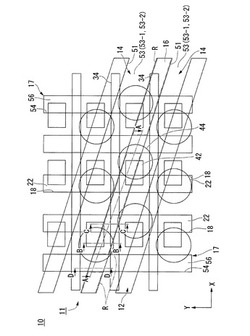

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】素子分離層の幅を狭くしつつ、素子分離層の底部を介した電流のリークを抑制する。

【解決手段】基板111と、ゲート絶縁膜121と、第1のゲート電極層122と、トランジスタ間の第1のゲート電極層122及びゲート絶縁膜121を貫通し、基板111とゲート絶縁膜121との界面S1よりも深い位置に底面を有する素子分離溝Tと、素子分離溝Tに埋め込まれた素子分離層131と、ゲート間絶縁膜123と、選択トランジスタ102を構成するゲート間絶縁膜123を貫通する第1の穴H1と、周辺トランジスタ103を構成するゲート間絶縁膜123を貫通する第2の穴H2と、素子分離層131上のゲート間絶縁膜123を貫通し、素子分離層131とゲート間絶縁膜123との界面S2よりも深い位置に底面を有する第3の穴H3と、第1から第3の穴H3に埋め込まれた部分を有する第2のゲート電極層124とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ストレージ拡散層を介したリーク電流の抑制が図られたメモリセルの作製に適した、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1導電型領域上に、ゲート絶縁膜とゲート電極の積層構造、及びキャパシタ絶縁膜とキャパシタ電極の積層構造を有する半導体基板を準備する工程と、ゲート電極とキャパシタ電極とを覆って半導体基板上に絶縁膜を形成する工程と、ゲート電極とキャパシタ電極との間の第2領域、及びゲート電極に対しキャパシタ電極と反対側の第3領域に、絶縁膜を通して第1導電型と反対の第2導電型の不純物を注入する工程と、絶縁膜をエッチングしてゲート電極側壁上にサイドウォールを残す工程と、第2領域上にマスク部材を形成する工程と、ゲート電極と、キャパシタ電極と、マスク部材と、ゲート電極側壁上のサイドウォールをマスクとし、第3領域に第2導電型不純物を注入する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、チャネルストップ領域を素子分離絶縁膜の下の半導体基板中に制御性良く形成することを目的としている。

【解決手段】 本発明は、第1導電型の半導体基板100の表面に設けられた第1の溝部6aと、第1の溝部6aの底面中央部から前記半導体基板の裏面方向に延び、前記第1の溝部6aの幅より小さい幅を有する第2の溝部6bとからなる分離溝6と、この分離溝6内に埋め込まれた素子分離絶縁膜5と、分離溝6の両側の前記半導体基板の表面にそれぞれの側で互いに離間して設けられた前記第1導電型と反対の第2導電型の拡散層10と、拡散層間10の半導体基板上にゲート絶縁膜7を介して形成されたゲート電極20と、第2の溝部6bの底部表面から所定深さにわたり設けられた、第1導電型と同じ導電型でありかつ半導体基板100の不純物濃度よりも高い不純物濃度を有するチャネルストップ領域30と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11上の素子領域に設けられるゲート絶縁膜13と、ゲート絶縁膜上に設けられるゲート電極14と、ゲート電極を挟むように半導体基板中に隔離して設けられるソースSまたはドレインDと、半導体基板中に形成される素子分離溝35中の底部および所定の深さDpの側面部にわたって設けられるp型絶縁層15−1と、絶縁層15−1と共に素子分離溝の底部および所定の深さDpの側面部を挟むように半導体基板中に設けられ、素子分離溝の側壁方向に沿ってソースまたはドレインと所定の距離(dS,dD)をもってオフセットするp型不純物拡散層15−2と、絶縁層上おける素子分離溝中の所定の深さDpに設けられる第1素子分離絶縁膜12−1と、第1素子分離絶縁膜上に設けられる第2素子分離絶縁膜12−2とを具備する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高耐圧トランジスタが形成される回路領域の面積を低減できる半導体記憶装置を提供する。

【解決手段】トランジスタHVTrは、半導体基板11上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14と、ゲート電極14の両側の半導体基板11内に形成されたソース領域15及びドレイン領域16とを有する。半導体基板11にはトランジスタを分離する素子分離領域12が形成されている。素子分離領域12下の半導体基板11内には不純物領域17が形成され、半導体基板11の表面領域には拡散層18が形成されている。拡散層18下で半導体基板11の表面から不純物領域17と同じ深さの半導体基板11内に、不純物領域17と同じ不純物濃度を持つ不純物領域19が形成されている。さらに、拡散層18上には基板コンタクト21が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子形成領域の端部のチャンネル起因の閾値電圧低下の抑制や、隣接素子との間のリーク電流の低減を可能にする。

【解決手段】シリコン基板1の表面は素子分離絶縁膜2により島状の素子形成領域である活性領域3に分離されている。活性領域3内にゲート絶縁膜4を介して矩形の環状をなすゲート電極GWが形成されている。ゲート電極GWの内部側Dinに内部拡散領域1bが、外部側Doutに外部拡散領域1cが形成されている。ゲート電極GWは活性領域3内に形成されるので、端部でのチャンネル発生を抑制できる。内部拡散領域1b側に高電圧を印加することで、隣接する素子との間のリーク電流の低減が可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化した場合であっても電気的特性の良好なメモリセルを得ることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上及びトレンチ12cの側壁に形成されたキャパシタ誘電体膜30aと、キャパシタ誘電体膜上に形成されたキャパシタ電極36aとを有するキャパシタ40と、キャパシタ40に接続されたメモリセルトランジスタ54と、メモリセルトランジスタとキャパシタとが形成されたメモリセル領域4における半導体基板に形成された第2導電型の第1のチャネルドープ層26aと、メモリセル領域における半導体基板内に形成され、第1のチャネルドープ層よりも浅い第2導電型の第2のチャネルドープ層27とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】より微細化が可能な半導体装置を提供する。

【解決手段】基板の表面から所定の深さまでの領域に設けられたソース電極およびドレイン電極と、これら2つの電極よりも基板内の深い位置に設けられたゲート電極とを含むMOSトランジスタが複数設けられ、複数のMOSトランジスタのソース電極またはドレイン電極と接続され、基板においてソース電極およびドレイン電極と同層または基板の表面よりも深い位置に設けられた配線を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化した場合であっても電気的特性の良好なキャパシタを得ることができる半導体装置及びその製造方法を提供する。

【解決手段】トレンチ12cが形成された半導体基板10と、半導体基板上及びトレンチの側壁に形成されたキャパシタ誘電体膜30aと、キャパシタ誘電体膜上に形成されたキャパシタ電極38とを有するキャパシタ40とを有し、キャパシタ電極は、半導体基板上及びトレンチ内に形成された第1の層32aと、第1の層が形成されたトレンチ内に埋め込まれた第2の層34と、第1の層上及び第2の層上に形成された第3の層36aとを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ワード線間又はビット線等における不純物プロファイルが適正に制御され、さらなる微細化が可能な半導体装置及びその製造方法を実現できるようにする。

【解決手段】半導体装置は、第1導電型の半導体基板11にストライプ状に形成された、第2導電型の不純物の拡散層である複数のビット線14と、半導体基板11の上における複数のビット線14同士の間の領域に形成された複数のゲート絶縁膜12と、半導体基板11の上に、各ゲート絶縁膜12を介在して形成され、複数のビット線14と交差する方向に延びる複数のワード線16と、半導体基板11における複数のワード線16同士の間の領域に形成された、第1導電型の不純物の拡散層である複数のビット線分離拡散層18とを備えている。各ビット線分離拡散層18は、不純物の拡散を抑制する拡散抑制物18Bを含む。

(もっと読む)

半導体素子の製造方法

【課題】エッチング工程時の感光膜の損傷率及びイオン不純物の浸透を防止すること。

【解決手段】半導体基板上にゲート絶縁膜パターン及びゲート電極膜パターンを形成する段階;前記ゲート電極膜パターンを含む前記半導体基板上に前記ゲートパターンの間の領域の一部を露出させる感光膜パターンを形成する段階;前記感光膜パターンの表面に前記半導体基板よりエッチング速度が遅い保護膜を形成する段階;前記保護膜及び前記感光膜パターンをエッチングマスクとして用いるエッチング工程で前記半導体基板に第1のトレンチを形成する段階;及び前記第1のトレンチが形成された前記半導体基板にイオン注入工程を行う段階を含む半導体素子の製造方法。

(もっと読む)

FLOTOX型EEPROMおよびその製造方法

【課題】トンネルウインドウに過剰な電圧が印加されたときに、トンネルウインドウがダメージを受けないように、トンネルウインドウの耐圧を周辺回路の耐圧よりも低くすることが望まれていた。

【解決手段】トンネルウインドウ12の下に形成される不純物領域としてのN領域25と、LOCOS酸化膜18の下に形成されるチャネルストッパ領域19との間に所定の間隔Yをあける。

【効果】トンネルウインドウ12に印加される電圧を制限して、トンネルウインドウ12にかかるストレスを低減し、書き換え回数が向上されたFLOTOX型EEPROMとすることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化に有利な、二重ウェル、及びこの二重ウェルから離れたウェルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板1内に形成された第1導電型の第1ウェル10と、第1ウェル10に形成された複数のメモリセルトランジスタQ5−1、Q5−2と、第1ウェル10の側面領域を囲む第1部分7、及び第1ウェル10の下部領域を囲む第2部分9を有し、第1ウェル10を半導体基板1から電気的に分離する第2導電型の第2ウェルと、半導体基板1内に形成された第2導電型の第3ウェル領域5と、を備える。

(もっと読む)

FLOTOX型EEPROM

【課題】Wセル方式のFLOTOX型EEPROMの設計においては、微細化のため、セルのレイアウトを工夫することが必須であるという課題があった。

【解決手段】Wセル方式のFLOTOX型EEPROMとするため、対をなす2つのフローティングゲート25a,25bと、2つのトンネルウインドウ30a,30bと、2つのソース26a,26bと、共有のコントロールゲート31と、共有のセレクトゲート32とを設けるとともに、ドレイン27も共有とした。

【効果】高信頼性設計、高耐圧設計が実現されたWセル方式のFLOTOX型EEPROMを実現できる。

(もっと読む)

垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法

【課題】垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法が開示される。

【解決手段】アクセス素子及びこれを形成する方法において、アクセス素子は、下部ソース/ドレイン領域と上部ソース/ドレイン領域を分離する垂直方向のチャンネル、チャンネル上に具備されるゲート絶縁膜、ゲート絶縁膜を横切って前記チャンネルを連結する一体型ゲート電極/連結ラインを含み、一体型ゲート電極/連結ラインはゲート絶縁膜と隣接するように具備され、下部ソース/ドレインの一部と少なくともオーバーレイされるディセンディングリップ領域を含むことができる。

(もっと読む)

半導体装置および半導体ウェハ

【課題】チャネルストップ注入層が活性領域に形成されることを防止して、トランジスタ特性の低下を防止した半導体装置を提供する。

【解決手段】ランダムロジック部RPはボディコンタクト部BDを有するのに対し、SRAM部SPはボディコンタクト部BDを有していない。また、SRAM部SPの周辺回路PPは、ランダムロジック部にはPTI構造を採用し、そのMOSトランジスタはPDSOI−MOSトランジスタとしてボディ固定される構成となっている。

(もっと読む)

半導体記憶装置

【課題】半導体装置、特にフラッシュメモリ等の不揮発性半導体メモリの周辺回路部において抵抗素子と基板との容量を小さくすることが可能な半導体記憶装置を提供する。

【解決手段】フラッシュメモリは、半導体基板1内に形成され、素子領域を区画する素子分離絶縁膜2と、素子分離領域2により分離された素子領域3にゲート酸化膜4、フローティングゲート(FG)として機能する第1のゲート電極5、第1の絶縁膜6上に、セルトランジスタの制御ゲート(CG:ワード線)として機能する第2のゲート電極材7が形成されている。周辺回路部において、素子分離絶縁膜2上に第1の絶縁膜6を介して第2のゲート電極材からなる抵抗素子7aとを備える。抵抗素子7a下の半導体基板1の不純物濃度は、バルクと同等かあるいはバルクの不純物濃度以下である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体基板に形成した溝部の側壁部分を用いる半導体記憶装置において、ワード線(ゲート電極)の加工を容易にし、高集積化を図れるようにする。

【解決手段】半導体記憶装置は、溝部1aを有する半導体基板1と、該半導体基板1に互いに間隔をおき且つ溝部1aと交差して形成された一対の不純物拡散層からなるソース・ドレイン領域11と、溝部1aの一壁面上に形成され、絶縁性を有するトラップ膜7と、半導体基板1におけるトラップ膜7と対向する領域に形成されたチャネル領域8と、溝部1aにトラップ膜7と接するように形成されたゲート電極9と、半導体基板1における溝部1aの底部又は溝部1aの下側に形成された素子分離領域6とを有している。

(もっと読む)

1 - 20 / 42

[ Back to top ]