Fターム[5F083PR06]の内容

Fターム[5F083PR06]に分類される特許

881 - 887 / 887

半導体構成及び半導体構造の形成方法

本発明は、ケイ化物を含む埋込みビット線を有する半導体構造を含む。縦型SGT(サラウンド・ゲート・トランジスタ)構造がビット線の上に形成される。SGT構造は、DRAMデバイスなどのメモリ・デバイスに組み込むことができる。本発明は4F2DRAMデバイスの形成に利用することができる。  (もっと読む)

(もっと読む)

容器コンデンサ及び作製方法

【課題】半導体構造体、及び複数のコンデンサ装置の作製方法を提供する。

【解決手段】本発明の例示的方法においては、絶縁材(28)中の開口部内に導電性蓄積ノード部材(60)が形成されて導電性容器が作製される。保持構造体(30)が容器の少なくとも一部と物理的接触状態となるように形成され、次いで絶縁材(28)が除去されることにより容器の外側表面が露出される。保持構造体(30)によって容器構造体のぐらつきあるいは他の構造上の欠陥が減じられる。導電性容器は第一コンデンサ電極に相当する。容器の外側側壁が露出された後、絶縁材(100)が容器内に露出された外側側壁に沿って形成される。その後に第二コンデンサ電極(103)が絶縁材上へ形成される。これら第一及び第二コンデンサ電極と絶縁材とによって複数のコンデンサ装置が作製される。

(もっと読む)

半導体集積メモリーおよび半導体集積メモリーの製造方法

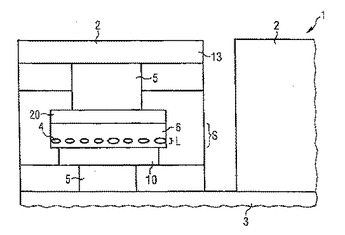

本発明は、2つの電極(10,20)間に配置された記憶媒体(6)を備えた半導体集積メモリー(1)に関する。上記記憶媒体(6)は、例えば相変化媒体であってもよい。記憶媒体(6)は、電流によって第1状態または第2状態に設定される。その結果、情報項目を記憶させることができる。本発明によれば、材料(4)からなる不純物粒子が注入された面(L)が設けられている。その結果、記憶媒体における電流密度が局部的に上昇し、プログラミングのために必要とされるプログラミング電流を低減できる。その結果、相変化媒体を含むメモリー素子の電流消費を低減できる。したがって、相変化媒体を含むメモリー素子を、トランジスタなどの他の部品と共に、最小構造寸法で実施することができ、単一の半導体回路に集積することができ、別個のサブ回路に配置する必要がなくなる。  (もっと読む)

(もっと読む)

半導体装置作製における垂直向きコンデンサ用支持体

半導体装置に用いる両面コンデンサの作製方法であって、該方法は、ウェハー加工間、コンデンサ底板(110)を支持する絶縁体構造体(86)を形成する工程を含む。前記構造体は、底板外側を露出させて両面コンデンサを作製するため底部絶縁体層(84)の除去中底板を支える点において特に有用である。支持構造体によって、セル誘電体層(200)、コンデンサ上板(202)及び最終絶縁体(204)の作製中も底板が支持される。また本発明による構造体についても開示されている。

(もっと読む)

(もっと読む)

FETベースの磁気ランダム・アクセス・メモリ・デバイス用の自己整列型導電線およびこれを形成する方法

【課題】下部メタライズ線(302)に導電的に結合された横方向の金属ストラップ(326)を含む、電界効果トランジスタ(FET)ベースの磁気ランダム・アクセス・メモリ(MRAM)デバイス用の導電線構造を提供すること。

【解決手段】金属ストラップ(326)上に磁気トンネル接合(MTJ)スタック(316)が形成され、MTJスタック(316)を覆って金属シールド(324)が形成され、金属シールド(324)は金属ストラップ(326)に対して自己整列される。上部メタライズ線(332)は金属シールド(324)に導電的に結合され、金属シールド(324)は上部メタライズ線(332)の形成時にエッチ・ストップとして働く。

(もっと読む)

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

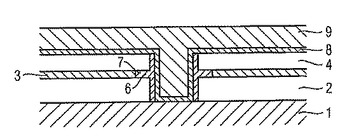

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

881 - 887 / 887

[ Back to top ]