Fターム[5F083PR38]の内容

Fターム[5F083PR38]の下位に属するFターム

Fターム[5F083PR38]に分類される特許

61 - 70 / 70

半導体素子の製造方法

【課題】本発明は半導体素子の製造方法に関し、特に半導体基板上に不純物を含むプラグ用ポリシリコン層を形成したあと、素子分離膜とゲートラインを形成して半導体素子の接合特性を向上させることができ、工程を単純化することができる技術を提供する。

【解決手段】プラグ用ポリシリコン層と半導体基板を連結するとき発生するコンタクトオープン面積の問題と半導体基板損傷の問題を解決するため、半導体基板上にプラグ用ポリシリコン層を形成したあと素子分離膜とゲートラインを形成する。

(もっと読む)

セルダイオードを採用する相変移記憶素子及びその製造方法

【課題】 セルダイオードを用いる相変移記憶素子及びその製造方法を提供すること。

【解決手段】 相変移記憶素子は、第1導電型の半導体基板及び前記半導体基板上に配置された複数のワードラインを備える。前記ワードラインは、前記第1導電型と異なる第2導電型を有して実質的に平らな上部面を有する。前記ワードラインのそれぞれの上部面上に前記ワードラインの長さ方向に沿って一次元的に配列された第1半導体パターンを提供する。前記第1半導体パターンは、前記第1導電型または前記第2導電型を有する。前記第1半導体パターン上に前記第1導電型を有する第2半導体パターンが積層される。前記ワードライン間のギャップ領域、前記第1半導体パターン間のギャップ領域、及び前記第2半導体パターン間のギャップ領域は絶縁膜で埋められる。前記絶縁膜の上部に複数の相変移物質パターンが二次元的に配列される。前記相変移物質パターンは前記第2半導体パターンにそれぞれ電気的に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜の凹凸の緩和にSOG膜が利用され、かつ段違いにホールが接近して形成される場合でも回路配線に信頼性が得られる半導体装置及びその製造方法を提供する。

【解決手段】コンタクトホール12とビアホール15の平面的な離間距離D1は、1μm以下の最小スペースとなっている。周辺回路領域に隣り合うメモリセル領域の境界に沿って第1層目金属配線層によるダミーパターン18が形成されている。このダミーパターン18は、SOG膜塗布時、その膜流動性によりメモリセル領域側に過剰に移動しようとするのを塞き止める。これにより、凹凸の密なメモリセル領域へのSOG膜の塗布に関し、メモリセル領域内部と最外周とで残り方が変わらないようにする。

(もっと読む)

半導体装置、DRAM集積回路装置およびその製造方法

多層配線構造を有する半導体装置は、第1の導電領域と、前記基板に対して前記第1の導電領域よりも高い位置に上面を有する第2の導電領域と、前記第1および第2の導電領域を覆う絶縁膜と、前記絶縁膜中に、前記第2の導電領域を露出するように形成された配線溝と、前記絶縁膜中に前記第1の導電領域を露出するように形成されたコンタクトホールと、前記配線溝および前記コンタクトホールを充填する配線パターンとよりなり、前記配線パターンの上面は、前記絶縁膜の上面に一致する。  (もっと読む)

(もっと読む)

磁気電子デバイスに使用される磁束集中系路を作製するための方法

磁気電子デバイスに使用される磁束集中系路(62)を作製するための方法が提供される。本方法は、基板(12)に形成されたビットライン(10)を設ける工程と、上記ビットライン(10)及び上記基板(12)を覆う第1材料層(24)を形成する工程とからなる。エッチングは、上記第1材料層(24)内に深溝(52)を形成するように実施され、クラッド層(56)が、上記深溝(52)内に堆積される。バッファ材料層(58)が、上記クラッド層(56)を覆って形成され、上記バッファ材料層(58)の一部及び上記クラッド層(56)の一部が除去される。  (もっと読む)

(もっと読む)

ポリマー電極を有する強誘電性ポリマーメモリ装置及びその製造方法

導電性ポリマー電極を有する強誘電体メモリモジュールの製造方法と該方法に従って製造される強誘電体メモリモジュールとが開示される。強誘電性ポリマーメモリモジュールは、内部にトレンチを規定するILD層(102);トレンチ内に配置された第1電極層(104);第1電極層(104)上に配置された第1導電性ポリマー層(106);第1導電性ポリマー層(106)上に配置された強誘電性ポリマー層(108)を含む第1レイヤーセットを有する。該モジュールは更に、内部にトレンチを規定するILD層(114);ILD層(114)のトレンチ内に配置された第2導電性ポリマー層(112);第2導電性ポリマー層(112)上に配置された第2電極層(116)を含む第2レイヤーセットを有する。第1導電性ポリマー層(106)及び第2導電性ポリマー層(112)は、電極層(104、116)と強誘電性ポリマー層(108)との間に反応障壁及び/又は拡散障壁をもたらすように電極層(104、116)を覆う。  (もっと読む)

(もっと読む)

直接トンネル型半導体記憶装置およびその製造方法

【課題】 セルサイズが小さく、平坦性の良い直接トンネル型半導体記憶装置、およびその製造方法を提供する。

【解決手段】 STI型の素子分離領域を有する直接トンネル型半導体記憶装置において、基板上に形成されたフローティングゲート電極の側壁面上に、コントロールゲート電極の一部を構成する導電部を誘電体膜を隔て形成し、さらに前記素子分離領域により画成された素子領域中においてソースおよびドレイン拡散領域を、前記STI構造を形成する素子分離溝の表面に、前記フローティングゲート電極直下の領域から離間するように形成し、かつ前記導電部を、前記素子領域中、前記素子分離溝から離間して形成する。

(もっと読む)

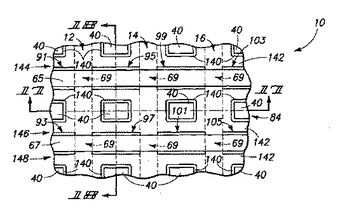

DRAMセル用の分離領域を有する半導体構造及び製造方法

本発明は、垂直に延びるピラー(80,82)を含む半導体構造、及び、そのような構造を形成する方法を含む。垂直に延びるピラーは、トランジスタデバイス(80,95)内に組み込まれることができ、トランジスタデバイスの垂直に延びるチャネル領域を含むことができる。トランジスタデバイスは、集積回路内に組み込まれることができ、ある態様では、たとえば、ダイナミックランダムアクセスメモリ(DRAM)構造などのメモリ構造に組み込まれる。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

ビット線拡散領域にコンタクト形成するにあたり周りのウェルとの短絡を確実に防止する構成の半導体記憶装置及びその製造方法の提供。

【解決手段】

メモリセル領域をなすpウェル101の、ワード線と、ワード線と交差する選択ゲートとによって覆われていないエリアにおいて、ビット線拡散領域のまわりに溝118を備え、溝118に絶縁膜119が埋め込まれている。

(もっと読む)

相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路

【課題】 相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路を提供する。

【解決手段】 第1不揮発性メモリ素子と、前記第1不揮発性メモリ素子上に積層された、第1不揮発性メモリ素子と相補的関係にある第2不揮発性メモリ素子とを含む相補型不揮発性メモリ素子であって、さらに、前記第1及び第2不揮発性メモリ素子の間にボンディング材が備えられた不揮発性メモリ素子である。

(もっと読む)

61 - 70 / 70

[ Back to top ]