Fターム[5F101BA28]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 絶縁膜材料 (1,647) | 不純物ドープ (27)

Fターム[5F101BA28]に分類される特許

1 - 20 / 27

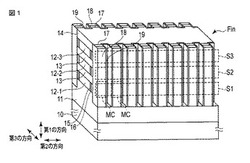

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

不揮発性半導体記憶装置

【課題】コントロールゲートとフローティングゲートとの間の電極間絶縁膜に発生するリーク電流を低減させ、メモリセルの微細化に伴うリーク耐性の劣化を抑制する半導体不揮発性記憶装置を提供する。

【解決手段】半導体基板1上に複数の不揮発性メモリセルを集積した不揮発性半導体記憶装置であって、メモリセルは、半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜2a上に形成されたフローティングゲート電極3aと、フローティングゲート電極3aの上面に形成された第1の電極間絶縁膜4aと、フローティングゲート電極3aの側面及び第1の電極間絶縁膜4aを覆うように形成された第2の電極間絶縁膜5aと、電極間絶縁膜5a上に形成されたコントロール電極6aとを備えている。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体装置,及び半導体装置の製造方法

【課題】上部絶縁層と素子分離絶縁層の界面に起因する信頼性劣化が抑制された半導体装置を提供する。

【解決手段】半導体装置は,半導体基板と,前記半導体基板上に配置され,かつトンネル絶縁膜,電荷蓄積層,上部絶縁層,および制御電極が順に積層される積層構造と,前記積層構造の側面に配置される素子分離絶縁層と,前記半導体基板の前記トンネル絶縁膜の両側に形成された不純物ドーピング層と,を具え,前記素子分離絶縁層は,SiO2,SiN及びSiONの少なくとも一つからなり,前記上部絶縁層は,希土類金属,Y,Zr,及びHfからなる群より選ばれる少なくとも一つの金属M,及びSiを含む酸化物であり,前記電荷蓄積層,前記上部絶縁層,前記制御電極それぞれのチャネル長方向の長さLcharge,Ltop,Lgateが関係「Lcharge,Lgate < Ltop」を満たす。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高電界領域及び低電界領域のリーク電流を低減する揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101の表面領域に互いに離間して設けられたソース/ドレイン領域111と、ソース/ドレイン領域111間のチャネル上に設けられたトンネル絶縁膜102と、トンネル絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられ、かつランタンアルミシリコン酸化物若しくは酸窒化物を含む第1の誘電体膜105と、第1の誘電体膜105上に設けられ、かつハフニウム(Hf)、ジルコニウム(Zr)、チタン(Ti)、及び希土類金属のうち少なくとも1つを含む酸化物若しくは酸窒化物を含む第2の誘電体膜106と、第2の誘電体膜106上に設けられた制御ゲート電極107とを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルにおけるショートチャネル効果の抑制と誤書き込みの防止の両方を実現し、不揮発性半導体記憶装置の高性能・低コスト化をはかる。

【解決手段】 半導体基板101上に複数の不揮発性メモリセルを配置して構成される不揮発性半導体記憶装置であって、メモリセルは、基板101の表面部に離間して設けられたソース・ドレイン領域120と、ソース・ドレイン領域120の直下の基板101内に設けられ、基板101よりも誘電率が低い埋め込み絶縁膜151と、ソース・ドレイン領域120の間に形成されるチャネル領域上に設けられた第1ゲート絶縁膜102と、第1ゲート絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられた第2ゲート絶縁膜104と、第2ゲート絶縁膜104上に設けられた制御ゲート電極105とを備えた。

(もっと読む)

絶縁膜、およびこれを用いた半導体装置

【課題】リーク電流を減少させることのできる絶縁膜を提供することを可能にする。

【解決手段】金属と、水素と、窒素とを含む非晶質の酸化物誘電体膜を有し、前記酸化物誘電体膜内の前記窒素の含有量[N]および前記水素の含有量[H]は、

{[N]−[H]}/2≦1.0×1021cm−3

を満たす。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】電荷蓄積層および制御ゲート電極層間に設けられる絶縁膜を通じて流れるリーク電流を抑制できるようにする。

【解決手段】ゲート間絶縁膜7が、下層絶縁膜7a/高誘電体絶縁膜7b/上層絶縁膜7cの積層構造によって構成されている。下層絶縁膜7aがシリコン窒化膜7aa/シリコン酸化膜7ab/界面層7ac/シリコン酸化膜7adの積層構造により構成されている。界面層7acが電荷トラップ層として設けられている。特に書込時のリーク電流を抑制でき、特性改善を図ることができる。

(もっと読む)

半導体装置

【課題】回路面積の増加を抑制しつつ昇圧効率を向上出来る半導体装置を提供すること。

【解決手段】素子領域AAと、前記素子領域AA上に形成された複数のMOSトランジスタTR及び容量素子Cと、複数の前記MOSトランジスタTRが直列接続され、且つ前記MOSトランジスタTRに前記容量素子Cが接続された電圧発生回路4と、前記MOSトランジスタTRのソース及びドレインの少なくともいずれかの領域32上に形成されたコンタクトプラグCP4、CP5と、データを保持するメモリセルMTとを具備し、各々の前記素子領域AAにおいて、ゲート34と前記コンタクトプラグCP4、CP5との間の距離aは、前記直列接続において後段に位置する前記MOSトランジスタTRほど大きくされる。

(もっと読む)

半導体装置

【課題】 電極間絶縁膜に起因するリーク電流を十分に抑制することが可能な半導体装置を提供する。

【解決手段】 半導体基板11上に形成されたトンネル絶縁膜13と、トンネル絶縁膜上に形成された浮遊ゲート電極14と、浮遊ゲート電極上に形成された電極間絶縁膜15と、電極間絶縁膜上に形成された制御ゲート電極16とを備えた半導体装置であって、電極間絶縁膜は、主絶縁膜と、主絶縁膜内に存在する複数の微粒子とを含む。

(もっと読む)

半導体素子の製造方法

【課題】 本発明は、トンネル酸化膜の形成時に酸化膜に窒素を蓄積させた後、後続で酸素を注入するための工程を行ってSi−N結合をSi−O−N結合に変更することにより、窒素プロファイル(N profile)の変化による特性劣化の防止、電気的ストレスの緩和及び酸素密度の増加などを通じてサイクリング(cycling)及び電荷保存(retention)特性などの素子特性を向上させることができる半導体素子の製造方法を提供するものである。

【解決手段】 半導体基板上に第1の絶縁膜を形成する段階と、前記半導体基板と前記第1の絶縁膜の界面に窒素を蓄積させて第2の絶縁膜を形成する段階と、前記第2の絶縁膜に酸素を注入して第3の絶縁膜に変更させる段階とを含む構成としたことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】絶縁膜の改質により電荷捕獲・放出特性を改善し、電界緩和、電荷書込み/消去/保持、電荷の過消去、それぞれに対応することのできる半導体記憶装置及びその製造方法を提供すること。

【解決手段】ソース・ドレイン拡散層と、前記ソース・ドレイン拡散層の間のチャネル領域上に順次形成された第1のゲート絶縁層、第1の電荷蓄積層、第2のゲート絶縁層、及び制御電極とを具備する、電気的に情報を書込み・消去・読み出し・保持することが可能なMONOS型不揮発性半導体記憶装置において、前記第1の電荷蓄積層は、主要元素としてAl及びOを含む絶縁膜を有し、該絶縁膜は、格子間O原子とAl原子を置換した4価カチオン原子との複合体からなる欠陥対、又は酸素欠損とO原子を置換したN原子との複合体からなる欠陥対を有することにより、Al2O3の価電子帯端から2eVないし6eVの範囲内に電子非占有準位を有することを特徴とするMONOS型不揮発性半導体記憶装置。

(もっと読む)

ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】電荷供給層と電荷蓄積層との間における絶縁膜を介しての電荷移動効率を向上させる半導体装置及びその製造方法を提供する。

【解決手段】表層部にチャネル形成領域を有する半導体層10と、半導体層10の上に設けられ、シリコンとゲルマニウムと酸素とを含む絶縁膜4と、絶縁膜4の上に設けられ、絶縁膜4を介して半導体層10から供給される電荷を蓄積可能な電荷蓄積層5と、を備えている。

(もっと読む)

半導体装置

【課題】SiO2よりも高い誘電率を有する材料からなる絶縁膜上に設けられた金属電極の仕事関数が所望の値を有する半導体装置を提供することを可能にする。

【解決手段】基板1と、基板に形成されたN型半導体層2と、N型半導体層上に形成されたシリコンおよび酸素ならびに窒素を含むかあるいはシリコンおよび窒素を含む第1ゲート絶縁膜10と、第1ゲート絶縁膜上に形成される第1ゲート電極12と、第1ゲート絶縁膜と第1ゲート電極との界面に形成され13族元素を含む第1界面層11と、第1ゲート電極の両側のN型半導体層に形成されたソース・ドレイン領域5,6とを有し、界面層の前記13族元素の結合状態は酸化、窒化または酸窒化結合状態の総数よりも金属結合状態の総数が多いPチャネルMISトランジスタ19と、を備えている。

(もっと読む)

マルチゲート電極構造を備えた電子デバイス、および、その電子デバイスを製造するための方法

チャネル領域(32)の上に横たわるマルチゲート構造体を含み、層(42)によって互いに間隔が隔てられた第2のゲート電極(24)と第1のゲート電極(52)とを更に備えた電子デバイス(10)と、該電子デバイスを形成するためのプロセスを開示する。マルチゲート構造体(52,24)は、第1及び第2の部分を備えた側壁スペーサ構造(62)を有する。第1及び第2のゲート電極は異なる伝導型を有する。電子デバイスはまた、チャネル領域の上に横たわる第1の伝導型の第1のゲート電極と、第1のゲート電極とチャネル領域(32)との間に横たわる第2の伝導型の第2のゲート電極と、第1のゲート電極と基板(18)との間に横たわる電荷を蓄積することができる第1の層(42)とを含む。  (もっと読む)

(もっと読む)

1 - 20 / 27

[ Back to top ]