Fターム[5F101BB12]の内容

不揮発性半導体メモリ (42,765) | 制御 (5,368) | 制御装置 (5,154) | コントロールゲートなし (38)

Fターム[5F101BB12]の下位に属するFターム

SDとFG間容量による制御 (15)

Fターム[5F101BB12]に分類される特許

1 - 20 / 23

メモリ装置

【課題】配線電極間の双方向の電流値、書き込み及び消去の電圧値、および記憶保持時間が制御容易なメモリ装置を提供する。

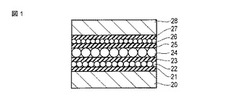

【解決手段】微結晶である第1の導電性微粒子を含む微結晶層22と、微結晶層22を挟むトンネル絶縁膜21、23とを有する第1の二重トンネル接合構造と、微結晶である第2の導電性微粒子を含む微結晶層26と、微結晶層26を挟むトンネル絶縁膜25、27とを有する第2の二重トンネル接合構造と、第1の二重トンネル接合構造と第2の二重トンネル接合構造との間に配置され、情報電荷を蓄積する電荷蓄積層と、第1の二重トンネル接合構造、電荷蓄積層、及び第2の二重トンネル接合構造を挟む第1、第2の導電層とを備える。第1の導電性微粒子の平均粒径は、第2の導電性微粒子の平均粒径と異なっている。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、ソース及びドレインの一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される第3の電界効果トランジスタと、を備える。

(もっと読む)

半導体装置

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。また、半導体装置の信頼性を向上させる。また、半導体装置の性能を向上すると共に、半導体装置の信頼性を向上する。

【解決手段】フローティングゲート電極FGを有するメモリトランジスタとこのメモリトランジスタに直列に接続された制御トランジスタとで構成されたメモリセルを、半導体基板の主面にX方向およびY方向にアレイ状に複数配列させる。そして、X方向に配列したメモリセルのメモリトランジスタのドレイン領域同士を接続するビット配線M1Bを、半導体基板上に形成された多層配線構造のうちの最下層の配線層に設け、このビット配線M1Bがフローティングゲート電極FG全体を覆うようにする。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルの面積を増大することなく、かつ、製造プロセスを変更することなく、不揮発性メモリセルのデータ書き込み速度およびデータ消去速度の向上を図ることのできる技術を提供する。

【解決手段】データ書き込み・消去用の容量部CWE、データ読み出し用のMIS・FETQRおよび容量部Cを互いに異なる位置に分離した状態で配置する。容量部Cの容量電極FGC2を覆う絶縁層6上にキャップ電極CAPを設けることにより、容量部Cは、容量電極FGC2とp型のウエルHPW1との間の容量およびキャップ電極CAPと容量電極FGC2との間の容量を加算した容量を有する。また、データ書き込み・消去用の容量部CWEにおけるデータの書き換えはチャネル全面のFNトンネル電流により行う。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】標準CMOSプロセスを用いて製造できる1層ポリシリコンのセル構造の半導体メモリ素子を実現すると共に、効率的な配置により実装面積を小さくし、記憶保持の信頼性を向上させた不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリセル4には、セレクトトランジスタTr41と、3つのメモリ素子Tr42、Tr43、Tr44とをトランジスタ形成部40に上下方向(縦方向)に順に配置する。不揮発性半導体メモリセル4をマトリックス状に配置するメモリセルアレイにおいて、セレクトトランジスタTr41のドレインを形成するn型拡散層401、コンタクト418及びメタル配線414を共用して上下方向に対称に配置し、更に、メモリ素子Tr41のソースを形成するn型拡散層405、コンタクト422及びメタル配線417を共用して上下方向に対称に配置する。

(もっと読む)

不揮発性半導体記憶装置

【課題】注入効率が高いソースサイドインジェクションによる電荷注入が可能で、標準的なCMOSプロセス工程内で基板上に実装可能な不揮発性半導体記憶装置を提供する。

【解決手段】第2不純物拡散領域7と第3不純物拡散領域8と第2ゲート電極14を有する選択トランジスタ2と、第1不純物拡散領域6と第3不純物拡散領域8と第1ゲート電極13を有するメモリトランジスタ3と、第4不純物拡散領域9に形成された第5不純物拡散領域10と第3ゲート電極17を有するMOSキャパシタ4を備え、第1ゲート電極13と第3ゲート電極17を電気的に接続してフローティングゲートFGとし、第4不純物拡散領域9と第5不純物拡散領域10を制御ゲートCGとし、第2ゲート電極14を選択ゲートとしてメモリセル1を構成し、第3不純物拡散領域8の不純物密度を第1及び第2不純物拡散領域6、7より低く5×1012ions/cm2以下に設定する。

(もっと読む)

不揮発性半導体記憶装置及びその使用方法

【課題】 セル面積の著しい増加を招かず、しかし、ディスターブの問題を解決した不揮発性記憶素子を提供すること。

【解決手段】 半導体基板に形成され第1の端子に接続されたp型の第1のウェルと、第1のウェルに形成され、第2の端子と第3の端子の間に直列に接続された第1のNMOSトランジスタ及び第2のNMOSトランジスタと、半導体基板に形成され第4の端子に接続されたn型の第2のウェルと、第2のウェルに形成され、第5の端子と第6の端子の間に直列に接続された第1のPMOSトランジスタ及び第2のPMOSトランジスタとを含み、第1のNMOSトランジスタのゲートは第7の端子を構成し、第1のPMOSトランジスタは第8の端子を構成し、第2のNMOSトランジスタと第2のPMOSトランジスタのゲートは共通に接続され、かつ、フローティング状態にあることを特徴とするメモリセルを含む不揮発性半導体記憶装置。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】不揮発性半導体記憶装置の構造を簡便化する。

【解決手段】半導体基板20の上にゲート絶縁膜30を介してポリシリコンからなるフローティングゲート40が設けられている。フローティングゲート40の両側壁には、側壁絶縁膜50が設けられている。第1の不純物拡散層60は、半導体基板20内に設けられ、フローティングゲート40から所定の距離だけ離間している。第2の不純物拡散層70は、半導体基板20内に設けられ、フローティングゲート40とオーバーラップしている。フローティングゲート40と容量カップリングした第2の不純物拡散層70に高電圧を印加することによりフローティングゲート40に電子が注入される。

(もっと読む)

半導体装置

【課題】浮遊ゲートをもち制御ゲートを備えていない不揮発性メモリセルを備えた半導体装置において、その不揮発性メモリセルの読出し特性を飛躍的に改善する。

【解決手段】不揮発性メモリセルは、P型半導体基板1上に形成された書込みメモリゲート酸化膜9及び書込みメモリゲート酸化膜9上に形成された電気的に浮遊状態のポリシリコンからなる書込み浮遊ゲート11をもつPMOS書込みトランジスタと、P型半導体基板1上に形成された読出しメモリゲート酸化膜15及び読出しメモリゲート酸化膜15上に形成された電気的に浮遊状態のポリシリコンからなる読出し浮遊ゲート17をもつNMOS読出しトランジスタを備えている。書込み浮遊ゲート11と読出し浮遊ゲート17は電気的に接続されている。不揮発性メモリセルへの書込みはPMOS書込みトランジスタによって行なわれ、読出しはNMOS読出しトランジスタによって行なわれる。

(もっと読む)

書込み可能型読出し専用メモリ

【課題】オフセルでのリーク電流が抑えられ、低コストで作製し易い書込み可能型読出し専用メモリを提供する。

【解決手段】半導体基板1に設けられた複数のメモリセルMC1を備え書込み可能型読出し専用メモリを構成するにあたり、半導体基板1上に第1ゲート絶縁膜9を介して配置された選択ゲート電極11と、半導体基板1上に第2ゲート絶縁膜13を介して配置された浮遊ゲート電極15と、選択ゲート電極11を挟んで互いに対峙する第1不純物拡散領域7aおよび第2不純物拡散領域7bと、浮遊ゲート電極11を挟んで第2不純物拡散領域に対峙する第3不純物拡散領域7cとにより個々のメモリセルを形成し、かつ第1不純物拡散領域7a、第2不純物拡散領域7b、および第3不純物拡散領域7cの各々をP型不純物拡散領域とすると共に、浮遊ゲート電極15での閾値電圧の絶対値を選択ゲート電極11での閾値電圧の絶対値よりも大きくする。

(もっと読む)

エージングデバイス及びその製造方法

【課題】エージングデバイスの寿命を正確にコントロールする。

【解決手段】本発明の例に関わるエージングデバイスは、上面が半導体基板11の上面よりも上にある素子分離絶縁層12と、素子分離絶縁層12により分離される第1及び第2素子領域13,14と、第1素子領域13内の半導体基板11内に形成される第1及び第2拡散層15a,15b,16a,16bと、第1及び第2拡散層間15a,15b,16a,16bの半導体基板11上に形成される第1ゲート絶縁膜19と、第2素子領域14内の半導体基板11上に形成される第2ゲート絶縁膜19と、第1及び第2ゲート絶縁膜19上に形成され、第1素子領域13から第2素子領域14まで跨って形成されるフローティングゲート電極20とを備え、第1及び第2拡散層15a,15b,16a,16bの最も深い部分は、素子分離絶縁層12から離れている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】書込み状態と消去状態の読出し電流の差である読み出しウィンドウを大きくとることができて、1デバイスにつき2ビット以上の記憶容量を有する信頼性の高いNROM等の半導体記憶装置を提供する。

【解決手段】p型の半導体層101には、チャネル領域108の中央部に、左右のn型の拡散領域106,107とは異なるp型の不純物の濃度が極大となる高濃度領域109が斜めイオン注入により形成されている。半導体層101上には、第一の絶縁膜102、電荷蓄積絶縁膜103、および第二の絶縁膜104を有しており、さらに、その上側に、ポリシリコン等よりなるゲート電極105を有する。

(もっと読む)

単層ポリシリコン不揮発性メモリーセルの動作方法

【課題】単層ポリシリコン・単一トランジスターOTPメモリーセルの動作方法を提供する。

【解決手段】この動作方法は、P型ウェルをP型ウェル電圧に電気的に接続し、N型ソースドープ領域とP型ウェルを接続するか、またはN型ソースドープ領域の電圧をP型ウェル電圧より大きくさせ、N型ドレインドープ領域を、P型ウェル電圧とN型ソースドープ領域の電圧に対しては正であるドレイン電圧に電気的に接続し、導電ゲートを、P型ウェル電圧に対しては正であるゲート電圧に電気的に接続し、N型チャンネルを強反転させるステップからなる。

(もっと読む)

半導体装置と半導体システム

【課題】シングルゲート構造でありながら、電荷の蓄積により一定時間オン又はオフするエージングデバイス又はEEPROMとして機能させる。

【解決手段】絶縁分離して形成された半導体領域10,20と、半導体領域10,20に跨るようにこれらの半導体領域10,20上にゲート絶縁膜を介して形成され、且つ半導体領域10に対する結合容量が半導体領域20に対するそれよりも大きくなるように形成された浮遊ゲート電極30と、半導体領域10の表面部に、浮遊ゲート電極30下のチャネル領域を挟んで形成され、一方がビット線BLに接続され他方がソース線SLに接続されたソース・ドレイン拡散層11,12と、半導体領域20の表面部に、浮遊ゲート電極下のチャネル領域を挟んで形成され、ワード線WLに共通接続された拡散層21,22とを備えた。

(もっと読む)

単一ゲート構造を有するEEPROM、該EEPROMの動作方法及び該EEPROMの製造方法

【課題】単一ゲート構造を有するEEPROM、該EEPROMの動作方法及び該EEPROMの製造方法を提供する。

【解決手段】互いに分離された第1活性領域、第2活性領域及び第3活性領域を有する半導体基板を備え、活性領域の上部を横切る共通の浮遊ゲートが提供され、浮遊ゲートの両側の第3活性領域にソース/ドレイン領域が形成され、第1活性領域に第1配線が接続し、第2活性領域に第2配線が接続し、ソース/ドレイン領域のうち一つに第3配線が接続するEEPROMである。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルのデータ書き込みおよび消去用の素子において、チャネル全面のFNトンネル電流によりデータを書き換える。

【解決手段】フラッシュメモリの形成領域の半導体基板1Sのn型の埋込ウエルDNW内にp型のウエルHPW1〜HPW3を互いに分離した状態で設け、そのウエルHPW1〜HPW3にそれぞれ容量部C、データ書き込み・消去用の容量部CWEおよびデータ読み出し用のMIS・FETQRを配置した。データ書き込み・消去用の容量部CWEでは、チャネル全面のFNトンネル電流によりデータの書き換え(書き込みおよび消去)を行う。

(もっと読む)

低不純物濃度MOSキャパシタを有する単一ポリEEPROMセル

【課題】標準CMOSプロセスでEEPROMメモリセルを製造するために、電気的に消去可能なプログラマブルリードオンリーメモリ(EEPROM)メモリセルおよび動作方法を開示する。

【解決手段】EEPROMメモリセルは、ほとんどまたはまったく追加の非標準処理を有しない標準CMOSプロセスで製造可能である。単一多結晶シリコン層を、低不純物濃度MOSキャパシタと組み合わせて使用する。EEPROMメモリセル300で使用される低不純物濃度キャパシタは、設計において非対称であり得る。非対称キャパシタによって領域が縮小する。反転によって引き起こされる更なるキャパシタンス変化も、複数の制御キャパシタを使用することによって低減できる。更に、複数のトンネルキャパシタ302を使用すると、カスタマイズされたトンネル経路の利点が提供される。

(もっと読む)

半導体装置

【課題】浮遊ゲートをもち制御ゲートを備えていないメモリトランジスタ及び選択トランジスタからなる不揮発性メモリセルと周辺回路トランジスタを備えた半導体装置において、メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板2上メモリゲート酸化膜15とメモリゲート酸化膜15上に形成された浮遊ゲート17をもつメモリトランジスタと、半導体基板2上に形成された選択ゲート酸化膜11と選択ゲート酸化膜11上に形成された選択ゲート13をもち、メモリトランジスタに直列に接続されている選択トランジスタを備えた不揮発性メモリセルと、半導体基板2上に形成された周辺回路ゲート酸化膜23と周辺回路ゲート酸化膜23上に形成された周辺回路ゲート25をもつ周辺回路トランジスタを備え、浮遊ゲート15のポリシリコン内の不純物濃度は周辺回路ゲート25のポリシリコン内の不純物濃度よりも薄くなっている。

(もっと読む)

1 - 20 / 23

[ Back to top ]