Fターム[5F101BD29]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | SOS (18)

Fターム[5F101BD29]に分類される特許

1 - 18 / 18

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体デバイス上に共形酸化物層を形成するための方法

半導体基板上に酸化物層を形成するための方法及び装置を開示する。1つ又は複数の実施形態では、半導体基板の温度を約100℃未満に制御することによって、プラズマ酸化を使用して、共形酸化物層を形成することができる。1つ又は複数の実施形態による半導体基板の温度を制御するための方法は、静電チャックならびに冷却剤及びガス対流を利用することを含む。  (もっと読む)

(もっと読む)

フラッシュ・メモリ・デバイスおよびその製造方法

【課題】 制御ゲートと浮動ゲートとの間にジグザグ容量を含み、浮動ゲートおよびチャネルに対する制御ゲートの結合を増大するフラッシュ・メモリ・デバイスを提供する。

【解決手段】 フラッシュ・メモリ・デバイスは、ウェハと、このウェハの上に配置されたゲート酸化物層と、このゲート酸化物層、ウェハ、またはそれらの組み合わせの上に配置された浮動ゲートであって、平坦な浮動ゲート部およびこの平坦な浮動ゲート部の選択された領域の上に配置された概ね矩形の浮動ゲート部を含む浮動ゲートと、浮動ゲートの上に配置された高K誘電材料と、高K誘電材料の上に配置された制御ゲートとを含み、高K誘電材料が浮動ゲートを制御ゲートに結合するジグザグ・パターンを形成する。

(もっと読む)

半導体デバイスの低温酸化のための方法

【課題】 半導体基板上に酸化物層を製造する方法の提供。

【解決手段】 ある実施形態において、半導体基板上に酸化物層を形成する方法は、プラズマリアクタの真空チャンバ内で基板支持体上に酸化すべき基板を載置するステップであって、チャンバが基板支持体から遠隔のイオン発生領域を有する、前記ステップと;チャンバにプロセスガスを導入するステップであって、プロセスガスが水素(H2)と酸素(O2)の少なくとも一つ - 約3:1までの水素(H2)と酸素(O2)の流量比で示される - 又は水蒸気(H2O蒸気)を含む、前記ステップと;チャンバのイオン発生領域に誘導結合プラズマを生成させて、基板上に酸化シリコン層を形成するステップと;を含む。

(もっと読む)

不揮発性メモリデバイス用インターポリ誘電体を形成するための統合スキーム

【課題】 不揮発性メモリデバイスの漏れ電流を維持するか又は減少させつつ、デバイス寸法の減少を可能にする電子デバイス及び電子デバイスを形成する方法の提供。

【解決手段】 一実施形態において、不揮発性メモリデバイスを製造する方法は、基板上にフローティングゲート多結晶層を堆積させるステップと、フローティングゲート多結晶層上に酸化シリコン層を形成するステップと、酸化シリコン層上に第一酸窒化シリコン層を堆積させるステップと、第一酸窒化シリコン層上に高k誘電物質を堆積させるステップと、高k誘電物質上に第二酸窒化シリコンを堆積させるステップと、第二酸窒化シリコン層上に制御ゲート多結晶層を形成するステップとを含む。一実施形態において、高k誘電物質層は、酸窒化シリコンハフニウムを含む。

(もっと読む)

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

半導体集積回路装置の製造方法

【課題】窒化シリコン膜の成膜工程において、ポリメタルゲートの一部を構成する高融点金属の酸化物による基板の汚染を低減する半導体集積回路装置の製造技術を提供する。

【解決手段】タングステン膜を含むゲート電極7A、7B、7C上に窒化シリコン膜11を形成する際、CVD装置のチャンバ内をタングステンの酸化物が還元される雰囲気にし、チャンバ内にアンモニアを供給し続けながら、ウエハ1を600℃以上の温度で昇温する。次に、チャンバ内にアンモニアとモノシランとを供給し、これらのガスを反応させることによって窒化シリコン膜11を堆積する。次に、モノシランの供給を止め、チャンバ内にアンモニアのみを供給し続けながらウエハ1を400℃まで降温した後、チャンバ内を窒素で置換し、ウエハをアンロードする。

(もっと読む)

半導体装置及びその作製方法

【課題】動作特性及び信頼性の向上した新規な構造の半導体装置及びその作製方法を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領域及びゲート電極の間に設けられた第2絶縁層と、を有する。半導体層は局所的に薄膜化され、薄膜化された領域にチャネル形成領域が設けられており、第2絶縁層は、少なくともゲート電極が重畳する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置、その制御方法およびその製造方法

【課題】ビットライン間隔の微細化または選択された範囲のメモリセルの半導体基板に電圧を印加すること。

【解決手段】本発明は、分離層12上に設けられた半導体層15内に設けられた半導体領域14と、半導体領域上に設けられたONO膜20と、半導体領域の両側の半導体層内に設けられ分離層に達するビットライン16と、半導体領域のビットラインが設けられた側部とは異なる両側に設けられ前記分離層まで達する素子分離領域18と、半導体領域に接続する第1電圧印加部34、44と、を有している。さらに、半導体領域はビットラインおよび前記素子分離により囲まれ、他の半導体領域から電気的に分離している半導体装置、その制御方法およびその製造方法である。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】一対の不純物領域の間にチャネル形成領域を形成する半導体基板と、その上層部に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極は少なくとも二層構造とし、第1の絶縁層に接する第1の浮遊ゲート電極は、半導体基板のバンドギャップより小さいことが好ましい。また、第2の浮遊ゲート電極は、金属材料若しくは合金材料又は金属化合物材料で形成されていることが好ましい。半導体基板のチャネル形成領域の伝導帯の底のエネルギーレベルより、浮遊ゲート電極の伝導帯底のエネルギーレベルを低くすることにより、キャリアの注入性を向上させ、電荷保持特性を向上させるためである。

(もっと読む)

半導体記憶装置

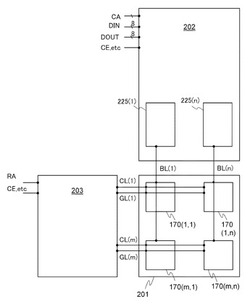

【課題】 個々のメモリ素子の特性バラツキに起因する読み出し動作余裕の低減を抑制し、高信頼性で高性能な読み出し動作が可能な半導体記憶装置を提供する。

【解決手段】 第1メモリ機能部Lの電荷蓄積量によりドレインとソースの一方から他方に流れる第1ドレイン・ソース電流Ids1が変化し、第2メモリ機能部Rの電荷蓄積量によりドレインとソースの他方から一方に流れる第2ドレイン・ソース電流Ids2が変化するメモリトランジスタ20と、第1ドレイン・ソース電流Ids1を流して得られる第1読み出し電圧と、第2ドレイン・ソース電流Ids2を流して得られる第2読み出し電圧を比較して、メモリトランジスタの記憶データを読み出す比較回路55を備え、第1メモリ機能部Lと第2メモリ機能部Rの各電荷蓄積量が、第1メモリ機能部Lに書き込まれるデータと第2メモリ機能部Rに書き込まれるデータが相補な関係になるように調整されている。

(もっと読む)

斬新な低電力不揮発性メモリおよびゲートスタック

良好な電荷保持のために、高い電荷ブロッキングバリアおよび深いキャリアトラッピングサイトを維持しながら、直接的なトンネルプログラミングと消去を可能にするNOR又はNANDメモリアーキテクチャにおいて、バンドギャップ技術に基づくゲートスタックを、反転モードおよび通常モードのフローティングノードメモリセルにおける非対称トンネルバリアと一緒に、使用することを促進する不揮発性メモリデバイスおよびアレイが記載されています。低電圧で直接的なトンネリングプログラムと消去の能力は、高いエネルギーキャリアからゲートスタックおよび結晶格子に対する損害を減少させて、書込み疲労を減少させ、デバイス寿命を増進させます。低電圧で直接的なトンネルプログラムと消去の能力は、また、低電圧設計およびさらなるデバイス形状性のスケーリングを介して、サイズ縮小を可能にします。本発明のメモリセルは、また、多数ビット記憶を可能にします。これらの特性は、本発明のメモリデバイスの実施の形態が、システム内のDRAMおよびROM双方に取って代わることができて、ユニバーサルメモリの定義内で動作することを可能にします。 (もっと読む)

半導体集積回路装置の製造方法

【課題】 チップの主面内のパターンの解像度を向上させる。

【解決手段】 チップを含む半導体ウエハの半導体基板1の主面上にキャップ膜を形成した後、チップ内のメモリ領域Mにキャップパターン15aを形成するための露光、現像およびエッチング処理と、チップ内においてメモリ領域Mから離れた空き領域Eにキャップパターン15b1を形成するための露光、現像およびエッチング処理とをそれぞれ別々に行う。これにより、メモリ領域Mおよび空き領域Eの各々に合った条件で露光および現像等を行うことができるので、チップの主面内のパターンの解像度を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置及びその制御方法

【課題】書き込み動作、読み出し動作及び消去動作を正常に行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】支持基板1上の埋め込み絶縁層2上の半導体層3に、埋め込み絶縁層2に接して設けられた同一導電型(n-型)のソース領域421〜42n、ドレイン領域422〜42(n+1)及びチャネル領域411〜41nを有するメモリセルトランジスタMT11〜MT1nを備える不揮発性半導体記憶装置であって、チャネル領域411〜41nの厚さTSOIが、1nm以上且つメモリセルトランジスタMT11〜MT1nのゲート長Lに6nmを加えた値以下である。

(もっと読む)

直列接続されたトランジスタ列を組込んだプログラマブルメモリアレイ構造およびこの構造を製造して作動させるための方法

三次元フラッシュメモリアレイは、直列接続されたNAND列に電荷蓄積誘電体が配置された薄膜トランジスタを組込んで、4F2のメモリセルのレイアウトを達成する。各NAND列はそれぞれ、グローバルビット線にNAND列の一方端を結合し、共有されたバイアスノードに他方端を結合するための2つのブロック選択デバイスを含む。ブロック内のNAND列の対は、同じグローバルビット線を共有する。メモリセルは、ブロック選択デバイスと同様に、好ましくはデプリーションモードのSONOSデバイスである。メモリセルは、デプリーションしきい値電圧付近にプログラミングされ得、ブロック選択デバイスは、デプリーションモードのしきい値電圧付近の電圧を有するプログラム状態に維持される。2つ以上の層上のNAND列は、1つの層上のグローバルビット線に接続され得、好ましくは、垂直方向の積層型ビアにより、ともに接続され得る。  (もっと読む)

(もっと読む)

浮遊ゲート装置において結合係数が改善された自己整合シャロートレンチ分離

本発明は、表面(2)を有する基板上に浮遊ゲート型半導体装置を製造する方法、及びそれによって製造した浮遊ゲート型半導体装置を提供する。本方法は、絶縁膜(4)、浮遊ゲート材料の第1の層(6)及び犠牲材料の層(8)を備えるスタックを基板表面に形成し、スタックを通って、基板(2)中に、少なくとも1つの分離領域(18)を形成し、それによって浮遊ゲート材料の第1の層(6)が上表面及び側壁(26)を有し、犠牲材料(8)を除去し、それによって分離領域(18)及び浮遊ゲート材料の第1の層(6)の上表面によって画定される空所(20)を残し、空所(20)を浮遊ゲート材料の第2の層(22)で充填し、それによって浮遊ゲート材料の第1の層(6)及び浮遊ゲート材料の第2の層(22)が共に浮遊ゲート(24)を形成する工程を備える。  (もっと読む)

(もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

1 - 18 / 18

[ Back to top ]