Fターム[5F101BE20]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | その他 (19)

Fターム[5F101BE20]に分類される特許

1 - 19 / 19

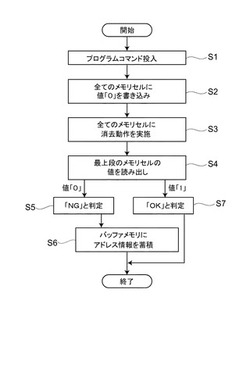

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】不揮発性記憶素子と、容量素子若しくは抵抗素子とを有するシステムICの製造方法を提供する。

【解決手段】半導体基板の主面の素子分離領域5上に下部電極10cが設けられ、かつ下部電極10c上にONO膜11,12,13からなる誘電体膜を介在して上部電極19cが設けられた容量素子Cを有する半導体集積回路装置であって、半導体基板の主面の素子分離領域5と下部電極10cとの間に耐酸化性膜8、及び下部電極10cと上部電極19cとの間に耐酸化性膜12を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型コンタクト用の溝の底および穴型コンタクト用の穴の底に成膜するバリアメタルの膜厚をほぼ等しくする。

【解決手段】本発明の半導体装置は、溝型のソースコンタクト8と、このソースコンタクト8と同じ高さで形成された穴型のドレインコンタクト9とを備えて成る半導体装置であって、ソースコンタクト8用の溝5の形状を、溝5の下部では素子領域3まで到達するように形成された穴5aが並んだような形状とするように構成したものである。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】動作信頼性を向上させるNAND型フラッシュメモリ等の半導体記憶装置、及びその製造方法を提供する。

【解決手段】半導体基板中10の第1活性領域上に第1ゲート絶縁膜14を介在して形成され、電荷を蓄積する第1絶縁膜15と、第1絶縁膜15上に、第1絶縁膜15よりも誘電率の高い材料を用いて形成された第2絶縁膜16と、第2絶縁膜16上に形成された第1金属膜18と、第1金属膜18上にシリサイド膜で形成された制御ゲート電極17と、ソース及びドレインとして機能する不純物拡散層13とを備えたメモリセルトランジスタMTと、半導体基板中10の第2活性領域上に第2ゲート絶縁膜33を介在して形成された第1導電膜35と、第1導電膜35上に形成された第2金属膜19と、第2金属膜19上にシリサイド膜で形成された第2導電膜17とを含む積層ゲートを備えたMOSトランジスタとを具備する。

(もっと読む)

凹型ソケットを有する環状バイアを備えるダイスタッキング

凹型導電性ソケットを備える環状バイアを有するダイを含むダイスタックおよびそのダイスタックを形成する方法は、様々な電子システムで使用するための構造を提供する。一実施形態において、ダイスタックは、別のダイの凹型導電性ソケット中に挿入されたダイの頂部上に導電性ピラーを含む。 (もっと読む)

半導体記憶装置

【課題】アナログ周辺回路に用いられる抵抗素子の材料などが設計変更されても、他の部分への設計変更が波及しない半導体記憶装置を提供する。

【解決手段】第1の絶縁膜12上に形成された第1の導電体13と、第1の導電体13上に形成され第1の開口19を有する第2の絶縁膜14と、第2の絶縁膜14上に形成され第1の開口19を介して第1の導電体13と導通する第2の導電体20と、第2の導電体20の上に形成された第3の絶縁膜21と、第3の絶縁膜21を貫通し第2の導電体20に導通する第1のコンタクト23と、第3の絶縁膜21と第2の絶縁膜14とを貫通して第1の導電体13と導通する第2のコンタクト22と、を有する抵抗素子を有する。配線の存在する層とは異なる層に存在する第2の絶縁膜14の有する第1の開口19の位置を変更すれば、第1のコンタクト23と第2のコンタクト22との間の抵抗値を変更することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子の占有面積を縮小化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、容量素子Cp1〜Cp3を構成する容量素子領域Cを有する。容量素子領域Cは、半導体基板上に積層された複数の容量線CpL1〜CpL4と、それら複数の容量線CpL1〜CpL4の上下間に形成された複数の層間絶縁層とを備える。隣接して積層された容量線の一方(CpL2,CpL4)は、所定電位に接続されている。隣接して積層された容量線の他方(CpL1,CpL3)は、接地電位に接続されている。隣接して積層された容量線CpL1〜CpL4及びそれら容量線CpL1〜CpL4間の層間絶縁層は、容量素子Cp1〜Cp3を構成する。

(もっと読む)

半導体記憶装置及びその駆動方法

【課題】製造工程中にメモリセルのビット線に印加される正負チャージが±1V程度に抑制された半導体記憶装置を実現できるようにする。

【解決手段】半導体記憶装置は、基板11に形成された第1導電型の第1ウェル12、第1導電型の第2ウェル14及び第2導電型の第3ウェル13と、第2ウェル14に形成された行方向に延伸する拡散ビット線20及び列方向に延伸するワード線22と、それぞれが拡散ビット線20及びワード線22と接続され、行列状に配置された複数のメモリセル26と、第1ウェル12に形成され、拡散ビット線20に電圧を印加する選択トランジスタ25と、第3ウェル13に形成された第1導電型拡散層19及び第3ウェル13により構成された順方向ダイオードとを備えている。拡散ビット線20、順方向ダイオード及び選択トランジスタ25のソースが互いに電気的に接続されている。

(もっと読む)

半導体装置の作製方法

【課題】より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

【解決手段】剥離層を用いて基板から剥離された半導体素子層を、他基板に形成され、平坦化された無機絶縁層に覆われた半導体素子層上に積層する。上層の半導体素子層を基板より剥離後、剥離層を除去し半導体素子層下に形成される無機絶縁膜を露出する。平坦化された無機絶縁層及び無機絶縁膜を密着させて接合する。また、半導体素子層の有する半導体層は半導体基板より分離され、作製基板に転置された単結晶半導体層である。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、負の閾値セルが存在するNAND型フラッシュメモリにおいて、負の閾値セルの安定した読み出しおよびベリファイができるようにする。

【解決手段】たとえば、VSGバイアス回路31は、制御回路からのDAC値に応じて可変抵抗器31aを制御することにより(ソースノードは電圧VSS)、正の閾値セルの読み出し時には、選択トランジスタSGTD,SGTSに4V程度の電圧(セレクトゲート電圧VSG)が一挙に印加されるようにする。一方、負の閾値セルの読み出し時には、最終的に、選択トランジスタSGTD,SGTSに5V程度のセレクトゲート電圧(正の閾値セルの読み出し時のセレクトゲート電圧VSGにセルソース線SRCのバイアス分の電圧を加えた電圧)VSGが印加されるようにする。

(もっと読む)

ビットラインレイアウトの構造を改善したフラッシュメモリ装置及びそのレイアウト方法

【課題】ビットラインレイアウトの構造を改善したフラッシュメモリ装置及びそのレイアウト方法を提供する。

【解決手段】ダブルパターニング方式に基づいてビットラインが配されるフラッシュメモリ装置において、データを保存するためのメモリセルを備えるセルストリングにそれぞれ連結される一本以上のメインビットラインと、メインビットラインと平行に配される一本以上のダミービットラインと、メインビットライン及びダミービットラインと異なる層に配され、共通ソース電圧を伝達するための共通ソースラインと、を備え、ダミービットラインは、第1電圧を伝達するための第1ダミービットラインと第2電圧を伝達するための第2ダミービットラインとを備えることを特徴とするフラッシュメモリ装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】浮遊ゲートの段差に起因する種々の問題を解決し、半導体メモリとしての特性劣化を簡便且つ確実に抑止して、高信頼性の半導体装置を実現する。

【解決手段】ダミーセル20aのダミー浮遊ゲート23aは、そのインターフェース部12側における最外端の側面(端部23b)が緩斜面に形成されており、その傾斜角度が、当該ダミー浮遊ゲート23aの他方の側面及び浮遊ゲート23における側面の傾斜角度よりも小さくなるように形成される。

(もっと読む)

半導体記憶装置

【課題】半導体装置、特にフラッシュメモリ等の不揮発性半導体メモリの周辺回路部において抵抗素子と基板との容量を小さくすることが可能な半導体記憶装置を提供する。

【解決手段】フラッシュメモリは、半導体基板1内に形成され、素子領域を区画する素子分離絶縁膜2と、素子分離領域2により分離された素子領域3にゲート酸化膜4、フローティングゲート(FG)として機能する第1のゲート電極5、第1の絶縁膜6上に、セルトランジスタの制御ゲート(CG:ワード線)として機能する第2のゲート電極材7が形成されている。周辺回路部において、素子分離絶縁膜2上に第1の絶縁膜6を介して第2のゲート電極材からなる抵抗素子7aとを備える。抵抗素子7a下の半導体基板1の不純物濃度は、バルクと同等かあるいはバルクの不純物濃度以下である。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷保持性能を短時間で容易に評価することができ、安価に製造することのできる不揮発性半導体記憶装置を提供する。

【解決手段】制御ゲート電極gcと浮遊ゲート電極gfの2つのゲート電極を有してなる書き換え可能な不揮発性メモリトランジスタTが行列状に配置された半導体基板1,1aにおける略四角形状の領域であるメモリマットM,M1,M2,Ma〜Mgと、メモリマットM,M1,M2,Ma〜Mgを加熱する局部加熱手段とを有してなる不揮発性半導体記憶装置100,100a〜100e,101,101a,102a,102bとする。

(もっと読む)

電子機器

【課題】ノイズ除去用素子以外の手段により、基板内のグランドの安定性を図る電子機器を得る。

【解決手段】CCDセンサ22から放出されるノイズは、CCDセンサ22のグランド端子22AからCCD基板16のグランド層16A、板バネ31、32、ヒートシンク24、及び、CCDブラケット20を経てフレーム12のフレームグランド14に至る。ここで、板バネ31、32は、CCDセンサ22のグランド端子22Aに近接して配置されるので、ノイズを効果的に除去できる。

(もっと読む)

磁気抵抗ランダム・アクセス・メモリ(MRAM)を用いた不揮発性メモリ・システム

不揮発性メモリ・システム(230)は、複数の磁気抵抗メモリ・セルを含む磁気抵抗ランダム・アクセス・メモリ(MRAM)(232)と、複数のフローティングゲート・メモリ・セルを含むフローティングゲート不揮発性メモリ(234)と、MRAM(232)及びフローティングゲート不揮発性メモリ(234)に結合された制御器(236)とを含む。制御器(236)は、システム・バス(220)に結合されるよう適合され、且つシステム・バス(220)から開始されたアクセスに応答して、MRAM(232)及びフローティングゲート不揮発性メモリ(234)のうちの選択された1つを制御する。  (もっと読む)

(もっと読む)

不揮発性メモリとその製造方法

【課題】 低消費電力での高速書き込みが可能で、かつ構造の簡単な不揮発性のメモリセルとその製造方法を提供する。

【解決手段】 素子分離領域2で分離された横方向の素子形成領域にソース拡散層4とドレイン拡散層5を交互に形成し、このソース拡散層4の両側にゲートONO膜6L,6Rを介して制御ゲート電極7L,7Rを形成する。制御ゲート電極7L,7Rの側面には、ゲート電極間絶縁膜8L,8Rを介してゲート電極10L,10Rを形成し、制御ゲート電極7L,7R、及びゲート電極10L,10Rは、素子分離領域2上のソースラインSL及びワードラインWLL,WLRで、それぞれ縦方向に接続する。更に、メモリセルが形成されたシリコン基板1の表面に中間絶縁膜11を形成し、横方向の各ドレイン拡散層5はコンタクト12を介してビットラインBLに接続する。

(もっと読む)

半導体記憶装置及び電子機器

【課題】 リードディスターブによるリファレンスセルの特性変動を防止する。

【解決手段】 メモリセル27m及びリファレンスセル27rは、共に、ゲート電極の両側に形成されて、電荷または分極を保持する機能を有するメモリ機能体を備える。メモリセル27mは、ゲート電極の両側のメモリ機能体27mr、27mlにおいて、夫々独立した情報の記憶及び読出しが可能である。一方、リファレンスセル27rは、ゲート電極の片側のメモリ機能体27rlに記憶された情報のみがセンスアンプ22で参照される。

(もっと読む)

1 - 19 / 19

[ Back to top ]