Fターム[5F101BF02]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 特性ヒステリシスしきい値 (921) | 記憶保持 (529)

Fターム[5F101BF02]に分類される特許

521 - 529 / 529

複数層のトンネリング障壁層を備える不揮発性メモリ素子及びその製造方法

【課題】データ保有時間及びデータ記録及び消去速度を向上させた不揮発性半導体メモリ素子及びその製造方法を提供する。

【解決手段】半導体基板21と、半導体基板21に形成されたソース22a領域及びドレイン22b領域と、ソース22a領域及びドレイン22b領域と接触して半導体基板21上に形成されたゲート構造体24と、を備える半導体メモリ素子において、ゲート構造体24は、相異なるバンドギャップエネルギーを持つ2層以上の複数層膜で形成されたトンネリング障壁層25を備える不揮発性メモリ素子。

(もっと読む)

直接トンネル型半導体記憶装置およびその製造方法

【課題】 セルサイズが小さく、平坦性の良い直接トンネル型半導体記憶装置、およびその製造方法を提供する。

【解決手段】 STI型の素子分離領域を有する直接トンネル型半導体記憶装置において、基板上に形成されたフローティングゲート電極の側壁面上に、コントロールゲート電極の一部を構成する導電部を誘電体膜を隔て形成し、さらに前記素子分離領域により画成された素子領域中においてソースおよびドレイン拡散領域を、前記STI構造を形成する素子分離溝の表面に、前記フローティングゲート電極直下の領域から離間するように形成し、かつ前記導電部を、前記素子領域中、前記素子分離溝から離間して形成する。

(もっと読む)

微粒子含有体及び微粒子含有体の製造方法並びに記憶素子、半導体装置及び電子機器

【課題】良好な特性が得られる微粒子含有体と、比較的少ない手間で良好な特性の微粒子含有体を製造できる微粒子含有体の製造方法を提供すること。

【解決手段】シリコン基板100の表面に、膜厚が約50nmのシリコン酸化膜110を熱酸化によって形成する。シリコン酸化膜110中に、約30keVの注入エネルギーで、負イオン注入法によって銀を注入する。銀が注入されたシリコン酸化膜110を、200℃よりも高く、かつ、銀の融点未満の温度で熱処理して、銀微粒子を形成する。酸化雰囲気中で熱処理をして、微粒子の表面部分を酸化して、被覆層としての酸化銀140を形成する。ナノメートルサイズの複数の微粒子130および被覆層140を、少ない工程で形成する。

(もっと読む)

半導体装置の製造方法

【課題】 トラップ膜を有するメモリセルのデータ保持特性の劣化を防止し、信頼性が高い半導体装置を得られるようにする。

【解決手段】 まず、p型の半導体基板11の上に、電荷を蓄積するONO膜12を形成する。続いて、ONO膜12に開口部を12dを形成し、形成した開口部12dから半導体基板11に砒素イオンを注入することにより、半導体基板11の各開口部12dの下側部分にn型拡散層14を形成する。続いて、ONO膜12の開口部12d側の端部を覆うように保護絶縁膜15を形成し、酸素を含む雰囲気で半導体基板11に保護絶縁膜15を介して熱処理を行なって、各n型拡散層14の上部を酸化することにより、各n型拡散層14の上部にビットライン酸化膜16を形成する。続いて、ONO膜12の上に導電体膜を形成することによりワードライン17を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 MONOS型不揮発性半導体記憶装置の高性能化、高信頼性化を推進することのできる技術を提供する。

【解決手段】 MONOS型不揮発性メモリのメモリセル1は、コントロールゲート6を備えたコントロールトランジスタ4と、メモリゲート8を備えたメモリトランジスタ5とで構成され、それらトランジスタは、基板2の表面に形成されたドレイン拡散層23およびソース拡散層24を有している。メモリゲート8と基板2との間の電荷蓄積部である窒化シリコン膜13は、メモリゲート8のゲート長方向の長さが、メモリゲート8のゲート長より短い。

(もっと読む)

不揮発性メモリーデバイスおよびそれの形成方法

一実施形態において半導体デバイス(10)は、半導体基板(20)中に均一に注入された第1の導電型を有する高ドープ層(26)を有し、基板(20)の頂部表面と高ドープ層(26)との間にはチャンネル領域(28)が配置されている。別の実施形態では半導体デバイス(70)は、カウンタドープされたチャンネル(86)およびそのチャンネルの下のパンチスルー防止領域(74)を有する。ゲートスタック(32)を基板(20)上に形成する。第2の導電型を有するソース(52)およびドレイン(54,53)をその基に注入する。得られた不揮発性メモリーセルは、低い自然閾値電圧を与えることで、読取サイクル時の閾値電圧ドリフトを小さくする。さらに、第2の導電型を有し、ドレイン側に斜めで注入されたハロー領域(46)を用いて、熱キャリア注入を支援することができ、それによってより高いプログラミング速度が可能となる。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ装置

【課題】 正負両極のいずれの高電界においてもリーク電流を低減することができ、且つ単独の高誘電体膜では困難な低電界から高電界の広い電界領域でリーク電流を抑制する。

【解決手段】 第1導電型の半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成されたフローティングゲート電極12と、フローティングゲート電極12上に電極間絶縁膜13を介して形成されたコントロールゲート電極14と、各ゲート電極12,14に対応して基板の主面に形成された第2導電型のソース・ドレイン領域15とを備えた不揮発性半導体メモリ装置であって、電極間絶縁膜13は、2種類以上の高誘電体材料13a,13b,13cによる3層以上の積層構造を有する。

(もっと読む)

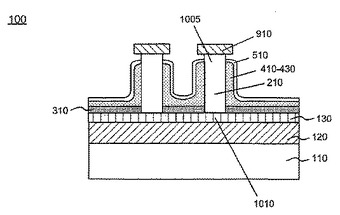

フラッシュメモリデバイス

メモリデバイス(100)は、導電構造(210)、複数の誘電層(410−430)、及び、制御ゲート(510)を含む。誘電層(410−430)は導電構造(210)の周りに形成され、制御ゲート(510)は誘電層(410−430)上に形成される。導電構造(210)の一部はメモリデバイス(100)のドレイン領域(1005)として機能し、また、誘電層(410−430)の少なくとも1つは、メモリデバイス(100)の電荷蓄積構造として機能する。誘電層(410−430)は、酸化物−窒化物−酸化物層を含む。  (もっと読む)

(もっと読む)

非対称のポケットドープ領域を有するメモリトランジスタおよびメモリユニット

本発明は、特に、ソース領域(S)近傍において、ポケットドープ領域(114)を1つ有しているフラッシュメモリトランジスタ(T11)に関する。上記メモリトランジスタ(T11)は、読み出し処理中において、ロードメモリ状態を妨害することなく機能する。 (もっと読む)

521 - 529 / 529

[ Back to top ]