Fターム[5F101BH17]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | 水素処理 (36)

Fターム[5F101BH17]に分類される特許

1 - 20 / 36

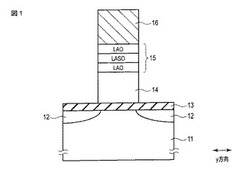

不揮発性半導体記憶装置

【課題】カップリング比の増大と書き込み/消去時のリーク電流の低減とを実現する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、半導体層11と、半導体層11上の第1の絶縁層13と、第1の絶縁層13上の電荷蓄積層14と、電荷蓄積層14上の第2の絶縁層15と、第2の絶縁層15上の制御ゲート電極16とを備える。第2の絶縁層15は、電荷蓄積層14側から制御ゲート電極16側に向かって、第1のランタンアルミネート層LAO、ランタンアルミシリケート層LASO及び第2のランタンアルミネート層LAOを備える。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体素子およびその製造方法

【課題】二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供する。

【解決手段】半導体素子10は、多結晶シリコン膜4と、絶縁膜5,9と、金属量子ドット8とを備える。多結晶シリコン膜4は、絶縁基板1上に配置され、アモルファスシリコン膜を熱プラズマジェットによってアニールして作製される。絶縁膜5は、SiO2からなり、多結晶シリコン膜4に接して多結晶シリコン膜4上に形成される。金属量子ドット8は、Ptからなり、Pt薄膜を熱プラズマジェットによってアニールして絶縁膜5上に形成される。絶縁膜9は、SiO2からなり、金属量子ドット8を覆うように絶縁膜5上に形成される。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1上に配置された不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板1上に順に形成されたメモリゲート絶縁膜MI1およびメモリゲート電極MG1を有する。メモリゲート絶縁膜MI1は、酸化シリコンを主体とする下部バリア膜BB1、窒化シリコンを主体とする電荷保持膜CS1、および、酸窒化シリコンを主体とする上部バリア膜TB1の、3層の積層絶縁膜からなる。特に、上部バリア膜TB1において、酸窒化シリコンのうちの酸化シリコンの割合は0.46より大きく、かつ、0.92以下である。

(もっと読む)

結晶半導体の製造方法およびそれを用いた半導体素子の製造方法

【課題】低温で結晶半導体を形成可能な結晶半導体の製造方法を提供する。

【解決手段】80〜240nmの膜厚を有するa−Ge膜2が基板1上に形成される(工程(b)参照)。そして、約10nmの膜厚を有するSiO2膜3がa−Ge膜2上に形成される(工程(c)参照)。その後、約90nmの膜厚を有するPt薄膜4がスパッタリングまたは蒸着によってSiO2膜3上に形成される(工程(d)参照)。そして、Pt薄膜4は、水素リモートプラズマによって処理される(工程(e)参照)。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】セルソース線、セルウェル線および電源線の各配線抵抗を低く維持しつつ、フォーミングガス・アニール工程における水素をメモリセルに供給することができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板11と、半導体基板上に形成され、データを電気的に格納することができる複数のメモリセルMCを含むメモリセルアレイMCAと、メモリセルに格納されたデータを検出するセンスアンプS/Aと、メモリセルのソース側に電気的に接続されたソースドライバCSDと、メモリセルのソースとセルソースドライバとの間を電気的に接続する第1の配線CSL3と、第1の配線と同じ配線層に形成されかつ第1の配線から絶縁され、センスアンプに電気的に接続された第2の配線VSSL3とを備え、第1および第2の配線は、所定間隔ごとに設けられた複数の貫通孔Hを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】下層の絶縁膜が窒化するのを抑制するとともに上層の絶縁膜からの酸素の拡散を抑制して電荷捕獲密度の低下を可及的に防止することを可能にする。

【解決手段】第1絶縁膜2と、第1絶縁膜上に形成され、窒素が添加されたアモルファスシリコン層4aと、アモルファスシリコン層上に形成された第1窒化シリコン層4bと、第1窒化シリコン層上に形成された第2絶縁膜10と、を備えていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】活性領域表面に凹凸を生じることなく活性領域上端の角部を丸めることができる半導体装置の製造方法を提供する。

【解決手段】活性領域を画定する素子分離絶縁膜を形成する工程と、活性領域上に、0.1nm以上、0.7nm未満の膜厚の自然酸化膜を形成する工程と、水素を含む雰囲気中で、850℃よりも高く950℃未満の温度で熱処理を行い、活性領域の角部を丸めるとともに、自然酸化膜を還元除去する工程と、自然酸化膜を除去した活性領域上に、ゲート絶縁膜を形成する工程とを有する。

(もっと読む)

半導体デバイスの製造方法及び基板処理装置

【課題】金属製のゲート電極(メタル電極)のダメージを熱酸化により修復する際の高誘電率ゲート絶縁膜の結晶化を抑制する。

【解決手段】エッチングにより側壁が露出した高誘電率ゲート絶縁膜とメタル電極とを有する基板を処理室内に搬入する工程と、処理室内で、基板を高誘電率ゲート絶縁膜が結晶化しない温度に加熱した状態で、基板に対してプラズマで励起した水素含有ガスと酸素含有ガスとを供給して酸化処理を施す工程と、処理後の基板を処理室内から搬出する工程と、を有する。

(もっと読む)

メモリー素子およびその製造方法

【課題】窒化シリコンからなる電荷蓄積部を備えたメモリー素子で、より長時間安定に電子を保持できるようにする。

【解決手段】基板101の上に形成された層間絶縁層102と、層間絶縁層102の上に形成されたゲート電極103と、ゲート電極103を覆うように形成された下部絶縁層104と、下部絶縁層104の上に形成された窒化シリコンからなる電荷蓄積部105と、電荷蓄積部105の上にこれを覆うように形成された上部絶縁層106と、上部絶縁層106の上に形成されたチャネル層107と、チャネル層107のチャネルが形成される領域を挟むように配置されたソース108およびドレイン109とを備え、電荷蓄積部105を構成している窒化シリコンに、窒化シリコンを構成している原子とは未結合状態で導入された水素原子を含むようにした。

(もっと読む)

絶縁膜、およびこれを用いた半導体装置

【課題】リーク電流を減少させることのできる絶縁膜を提供することを可能にする。

【解決手段】金属と、水素と、窒素とを含む非晶質の酸化物誘電体膜を有し、前記酸化物誘電体膜内の前記窒素の含有量[N]および前記水素の含有量[H]は、

{[N]−[H]}/2≦1.0×1021cm−3

を満たす。

(もっと読む)

不揮発性半導体記憶素子及びその製造方法並びに表示装置

【課題】複雑な工程を経ることなく不揮発性半導体記憶素子を製造する。

【解決手段】不揮発性半導体記憶素子10は、絶縁基板11と、絶縁基板11上に設けられ、ソース領域13s、チャネル領域13c、及びドレイン領域13dが形成された半導体層13と、半導体層13を覆うように設けられたゲート絶縁膜14と、ゲート絶縁膜14内に、半導体層13のチャネル領域13cに対応するように埋設されたメモリ用金属粒子層15と、ゲート絶縁膜14上に、半導体層13のチャネル領域13cに対応するように設けられたゲート電極16と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

【解決手段】剥離層を用いて基板から剥離された半導体素子層を、他基板に形成され、平坦化された無機絶縁層に覆われた半導体素子層上に積層する。上層の半導体素子層を基板より剥離後、剥離層を除去し半導体素子層下に形成される無機絶縁膜を露出する。平坦化された無機絶縁層及び無機絶縁膜を密着させて接合する。また、半導体素子層の有する半導体層は半導体基板より分離され、作製基板に転置された単結晶半導体層である。

(もっと読む)

結晶質アルミニウム酸化物層のエネルギーバンドギャップを高める方法及びエネルギーバンドギャップの高い結晶質アルミニウム酸化物層を備える電荷トラップメモリ素子の製造方法

【課題】結晶質アルミニウム酸化物層のエネルギーバンドギャップを高める方法及びエネルギーバンドギャップの高い結晶質アルミニウム酸化物層を備える電荷トラップメモリ素子の製造方法を提供する。

【解決手段】下部膜上に非晶質アルミニウム酸化物層を形成する第1ステップと、非晶質アルミニウム酸化物層内に水素(H)または水酸基(OH)を導入する第2ステップと、水素または水酸基が導入された非晶質アルミニウム酸化物層を結晶化させる第3ステップと、を含むことを特徴とするアルミニウム酸化物層のエネルギーバンドギャップを高める方法である。これにより、結晶化されたアルミニウム酸化物層のエネルギーバンドギャップは、7.0eVより大きい。

(もっと読む)

1 - 20 / 36

[ Back to top ]