Fターム[5F102GA05]の内容

接合型電界効果トランジスタ (42,929) | 集積化 (1,005) | FETとFET (424) | MOS・FET+MES・FET (49)

Fターム[5F102GA05]に分類される特許

21 - 40 / 49

半導体装置、半導体基板、及び半導体基板の処理方法

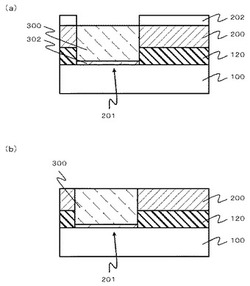

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

半導体装置および電子機器

【課題】ノーマリーオフ動作を実現するとともに製造コストの増大を防ぐことが可能な半導体装置および電子機器を提供する。

【解決手段】半導体装置101は、第1の電界効果トランジスタF1の制御電極と第2電源ノードN2との間に接続され、第1の電界効果トランジスタF1の制御電極における電圧が所定値以上になると第1の電界効果トランジスタF1の制御電極から第2電源ノードN2への方向に導通するスイッチ素子ZDを備え、第1の電界効果トランジスタF1は、エピタキシャル成長用基板と、エピタキシャル成長用基板の主表面上に形成された半導体層とを含み、第1の電界効果トランジスタF1の第1導通電極、第2導通電極および制御電極は半導体層上に形成され、半導体層と電気的に接続され、第1の電界効果トランジスタF1の制御電極および半導体層によってショットキー接合が形成されている。

(もっと読む)

モノリシック垂直集積複合III−V族及びIV族半導体デバイス

【課題】3ー5族半導体デバイスを4族半導体デバイスと一緒に、単一のダイの上にモノリシック集積することができる半導体装置を提供する。

【解決手段】第1、第2の表面を有する両面仕上げ処理された半導体基板と、前記第1の表面上に形成され、一つの4族半導体デバイスを含む4族半導体層と、前記第2の表面上に形成され且つ前記少なくとも一つの4族半導体デバイスに電気的に結合された3−5族半導体デバイスを含む3−5族半導体本体130とを備える。さらに電気的結合のための基板ビア112及び/又はウェハ貫通ビア114を備える。4族半導体層はエピタキシャルシリコン層とすることができ、エピタキシャル層上に形成されたTFET及びショットキーダイオード(FETKY)とすることができる。また、3−5族半導体デバイスは高電子移動度トランジスタ(HEMT)170とすることができる。

(もっと読む)

横型HEMTおよび横型HEMTの製造方法

【課題】高いアバランシュブレークダイン強度を有する横型HEMTと、その製造方法を提供する。

【解決手段】基板10と、基板上に配置された、第1導電型のチヤネルとなる第1層11、少なくとも部分的に上記第1層11の上に配置された電子供給層となる第2層12を有する。さらに、上記横型HEMTは、上記第1導電型に対して相補的な第2導電型の半導体物質を有し、少なくとも部分的に上記第1層11の中に配置された第3層13を有する。このためPNダイオードが上記第1層および第3層の間で形成され、PNダイオードは横型HEMTより低いブレークダウン電圧を有することにより、HEMTを高い電界から保護することができ、HEMTの劣化を防止できる。

(もっと読む)

半導体装置

【課題】接合FETを備えた半導体装置の特性を向上させる。

【解決手段】主たるトランジスタとして接合FET10を備え、制御用トランジスタとしてMISFET20を備えた半導体装置であって、接合FET10は第1ゲート電極G1、第1ソース電極S1、および、第1ドレイン電極D1を有し、MISFET20は第2ゲート電極G2、第2ソース電極S2、および、第2ドレイン電極D2を有する。また、MISFET20はnチャネル型であり、エンハンスメント型の電気特性を有する。また、MISFET20の第2ゲート電極G2と第2ドレイン電極D2とは短絡接続され、接合FET10の第1ゲート電極G1とMISFET20の第2ソース電極S2とは短絡接続されている。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

窒化ガリウム半導体装置およびその製造方法

【課題】回路全体の小型化を実現し、高温環境下で使用することができる窒化ガリウム半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1の表面には、絶縁層2、アンドープの第1GaN層3、AlGaN層4がこの順で積層されている。第1GaN層3とAlGaN層4の界面には、2次元電子ガスで形成された表面障壁層5が形成されている。AlGaN層4の表面層には、第1GaN層3に達し、かつ貫通しない程度の凹部(第1凹部)が形成されている。このような半導体基板1に、第1高耐圧トランジスタ110および制御回路120が一体的に形成されている。第1高耐圧トランジスタ110は、第1凹部およびAlGaN層4の表面に形成されている。また、制御回路120は、第1凹部の一部に形成されたnチャネルMOSFETと、AlGaN層4の表面に形成されたデプレッション型nチャネルMOSFETとで構成されている。

(もっと読む)

ハイブリッド基板回路

【課題】3−5集積回路とシリコン集積回路とは別々の集積回路上に設けられてきた。3−5集積回路とシリコン集積回路等の相違する基板を必要とする複数の回路を1つの集積回路において組み合わせることを可能にするハイブリッド基板回路を提供すること。

【解決手段】ハイブリッド基板回路は、第1半導体材料の第1領域と、埋め込み酸化層および埋め込み酸化層の上方の第2半導体材料を含んでいる第2領域と、第1半導体材料内に形成された第1回路と、第2半導体材料内に形成された第2回路と、第1回路と第2回路との間のシャロー・トレンチ・アイソレーション領域103と、を含んでいる。第1半導体材料はシリコンを含み、第2半導体材料はシリコンを含んでいない。第1回路はCMOS回路101であり、第2回路は高電子移動度トランジスタ回路102である。

(もっと読む)

パワー電界効果トランジスタ

寄生NPNなしでバルクシリコンからの電流フローを許容する、非常に短いチャネルを有するハイブリッドパワー電界効果トランジスタ(FET)装置。装置は、JFETコンポーネント、JFETコンポーネントに近接して配置された第1の蓄積型MOSFET、およびトレンチ端の底部のJFETコンポーネントに近接して配置された第2の蓄積型MOSFETまたはソースに接続する絶縁ゲートを有するMOSFETを含む。 (もっと読む)

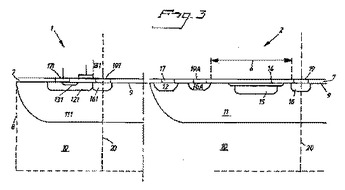

第1絶縁ゲート電界効果トランジスタが第2電界効果トランジスタと直列に接続された半導体デバイス

第1絶縁ゲート電界効果トランジスタ(1)が第2電界効果トランジスタFET(2)と直列に接続された半導体デバイスであって、前記第1絶縁ゲート電界効果トランジスタの厚くドープされたドレイン接点領域(191)へ電気的に接続されている厚くドープされたソース領域(19A)を前記第2電界効果トランジスタ(2)が有し、更に第2電界効果トランジスタ(2)のピンチ電圧Vpよりも前記第1絶縁ゲート電界効果トランジスタ(1)のブレークスルー電圧の方が高い前記半導体デバイス。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極下端の側面に接する領域に半導体表面が露出することを防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板(20)の上に、電子走行層(21)と電子供給層(23)とが配置されている。電子供給層の上に、ソース電極(30F)及びドレイン電極(31F)が、相互に間隔を隔てて配置されている。ソース電極とドレイン電極との間の電子供給層の上に、ゲート電極(40F)が配置されている。電子供給層の上に、ソース電極とゲート電極との間の領域、及びドレイン電極とゲート電極との間の領域を覆う保護膜(35)が形成されている。ゲート横開口(38)が保護膜に形成されている。ゲート横開口は、ソース電極とゲート電極との間の領域、及びドレイン電極とゲート電極との間の領域の少なくとも一方に、ゲート電極、ソース電極、及びドレイン電極のいずれからも間隔を隔てて配置されている。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

高耐圧MOSトランジスタの回路シミュレーション方法

【課題】双方向MOSとしてのモデルを実現可能とし、高耐圧MOSのシミュレーション精度を向上する。

【解決手段】高耐圧MOSFETのシミュレーションを行うためのマクロモデルとして、NMOSFETのドレイン側とソース側に第1、第2のJFET(JN1、JN2)をそれぞれ付加し、第1のJFET(J1)のゲートに第1のダイオード(D1)の一端を接続し、第1のダイオード(D1)の他端を、前記NMOSFETのソースに接続し、第2のJFET(J2)のゲートに第2ダイオード(D2)の一端を接続し、第2のダイオード(D2)の他端を前記NMOSFETのドレインに接続してなるマクロモデルを用いてシミュレーションを行う。

(もっと読む)

窒化物系化合物半導体装置

【課題】リーク電流の増大、及び電流コラプス現象によるオン抵抗の増大を抑制できる窒化物系化合物半導体装置を提供する。

【解決手段】窒化物系化合物半導体からなるキャリア走行層3を有する半導体層10と、半導体層10の主面100上に配置され、キャリア走行層3を流れる主電流の電流経路の端部である第1の主電極21及び第2の主電極22と、第1の主電極21及び第2の主電極22を囲むように主面100上に配置され、主面100直下及びその近傍の半導体層10内の電荷を制御する外周電極30とを備える。

(もっと読む)

電界効果トランジスタ

【課題】ブレイクダウン電圧が高く、閾値電圧が安定で、かつゲート電極についての遷移電流が小さい電界効果トランジスタを提供すること。

【解決手段】この発明の電界効果トランジスタは、半導体層上でこの半導体層の表面に沿って互いに離間した位置に、それぞれ金属電極を有するソース、第1ゲート、第2ゲート、ドレインをこの順に備える。第1ゲートはMIS型であり、第2ゲートはショットキ型である。

(もっと読む)

半導体装置およびその製造方法

【課題】コプラス時オン抵抗を低減化し、かつゲート漏れ電流を低減化した半導体装置を提供する。

【解決手段】窒化物系化合物半導体層(3,4)上に窒化物系化合物半導体層(3,4)とショットキー接触するゲート電極7と、ゲート電極7上に形成された第1の絶縁膜18と、ゲート電極7から離間した窒化物系化合物半導体層(3,4)上に窒化物系化合物半導体層(3,4)と低抵抗接触するソース電極5と、ゲート電極7と第1の絶縁膜18を介して形成され、ソース電極5と電気的に接続し、平面的に見て、ゲート電極7の上を跨ぐように延伸しているソースFP電極9と、ソースFP電極9上に形成された第2の絶縁膜10とを有する半導体装置であって、ソースFP電極9の厚みはソース電極5の厚みよりも厚く形成されている。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置であって、半導体装置は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN2とを有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電位ノードNL1に結合される第3ノードN3を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第3ノードN3から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体素子及び分布増幅器

【課題】分布増幅器の動作を安定化する。

【解決手段】デュアルゲート電極と、2つの主電極とを有する半導体素子において、デュアルゲート電極の第2ゲート電極21から配線層24を延出し、配線層24を絶縁膜25を介して、ソース電極23に接続し、配線層24と絶縁膜25とソース電極23で構成されるMIMキャパシタ26を半導体素子1内部に配置した。そして、このような半導体素子1を分布増幅器に増幅回路素子として搭載した。これにより、分布増幅器は高出力で広帯域特性を備え、安定に動作する。更に、高集積化、低コスト化を図ることができる。

(もっと読む)

MIS構造を内蔵するHEMT

【課題】 ノーマリオフで動作するMIS構造を有するHEMTを提供すること。

【解決手段】 HEMT10は、ドレイン電極に電気的に接続するドレイン領域32と、ソース電極に電気的に接続するソース領域34と、ドレイン領域32とソース領域34の間に形成されている第1半導体領域22と、第1半導体領域22の表面の一部にゲート絶縁膜42を介して対向しているゲート電極42を有するMIS構造40と、第1半導体領域22の表面の残部に接しているとともに第1半導体領域22のバンドギャップよりも広いバンドギャップを有する第2半導体領域24を有するヘテロ構造を備えている。ドレイン領域32とソース領域34は、MIS構造40とヘテロ構造を直列に配置した構造で接続されている。

(もっと読む)

21 - 40 / 49

[ Back to top ]