Fターム[5F102GN02]の内容

接合型電界効果トランジスタ (42,929) | 表面半導体層(ゲートメタル電極底面より高い位置にある層) (914) | 単一半導体層 (704) | 4族 (11)

Fターム[5F102GN02]に分類される特許

1 - 11 / 11

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

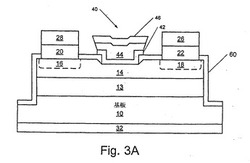

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

選択エピタキシャル成長を用いた横型接合型電界効果トランジスタの製造方法

接合型電界効果トランジスタ(JFET)などの半導体素子を製造する方法が記載される。方法は、自己整合であり、素子のゲート又はソース/ドレイン領域を形成するために、再成長マスク物質を用いた、選択的エピタキシャル成長に関する。方法は、イオン注入の必要性を除去する。素子は、SiCなどのワイドギャップ半導体物質から形成される。再成長マスク物質は、TaCである。素子は、放射線及び/または高温にさらされることを含む過酷な環境において使用される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】デバイス特性の歩留まりを向上して、実用化を可能とする半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置(FET)は、ダイヤモンド単結晶からなる半導体膜(活性層)を備え、半導体膜(活性層)の表面13aは、{001}面から、[110]方向から半導体膜(活性層)の表面13a内において−15度以上15度以内の方向に、2度以上10度以下傾斜している。半導体膜(活性層)は、半導体膜(活性層)のオフ方向と垂直な面内にチャネルを有している。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】特性の安定性が高い電界効果トランジスタ及びその製造方法を提供する。

【解決手段】基板2上にバッファ層3、アンドープGaN層4、AlGaN層5及びSiC層9をこの順に形成する。SiC層9のキャリア濃度は1×1017cm−3以上とし、抵抗率は10mΩcm(ミリオーム・センチメートル)以下とする。次に、SiC層9に対してSF6ガスにより反応性イオンエッチングを施し、SiC層9をパターニングする。そして、AlGaN層5上に保護膜10を形成した後、SiC層9上にソース電極6及びドレイン電極7を形成し、AlGaN層5上にゲート電極8を形成する。

(もっと読む)

SiCに基づく半導体ヘテロ接合デバイス

SiC上にヘテロ構造のためのSi(1-x)MxC材料を、CVD、PVD及びMOCVDにより成長させ得る。Alのような金属でドープされたSiCは、バンドギャップ、それ故にヘテロ構造を改質する。SiC及び金属ソースを用いるSiC Si(1-x)MxCのヘテロ接合の成長は、改良されたHFMTs(高周波移動度トランジスタ)、HBTs(ヘテロ接合バイポーラトランジスタ)及びHEMTs(電子移動度トランジスタ)の製造を可能とする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、動作領域にSi/SiCのヘテロ接合を用い、SiCに依ってnチャネル・トランジスタ及びpチャネル・トランジスタそれぞれに好適な歪みを印加できるようにして超高速の半導体装置を実現しようとする。

【解決手段】 半導体装置に含まれるnチャネル絶縁ゲート型FETに於いては、Si層1上に形成されたSiC層2と、SiC層2上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極4と、Si層1上に形成されたSiC層2のうちソース領域5及びドレイン領域6を覆う部分の上に形成されてSiに比較して格子定数が小さく且つSiCに近い格子定数をもつ物質で構成された層、即ち、3C−SiC層8とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】素子間を分離する絶縁層を容易に形成することができ、また配線の段切れを防止することができ、さらには配線部における寄生容量も低減できる、半導体装置およびその製造方法を提供する。

【解決手段】SiC基板(またはSiC薄膜)に素子間を分離する溝17が形成され、その溝17内が酸化膜(SiO2)18などの絶縁膜で埋め込まれた構造とする。絶縁膜は堆積によって形成すればよいので、1um以上の厚みが容易に得られ、簡便な方法でありながら、良好に素子分離することが可能となる。溝17内を埋め込んだ絶縁膜上に配線することで、断線を防止し、寄生容量を低減することが可能である。

(もっと読む)

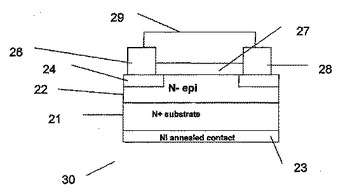

炭化ケイ素上に耐久性接触を有するデバイスおよびその製造方法

ショットキーバリア炭化ケイ素デバイスは、レニウムショットキー金属接触を有している。レニウム接触(27)は250Åよりも厚く、2000Åから4000Åまでの間であり得る。ターミネーション構造は、ショットキー接触の周囲の環状領域をイオンミリングすることによって与えられる。  (もっと読む)

(もっと読む)

1 - 11 / 11

[ Back to top ]