Fターム[5F102GV01]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 空間配線の利用 (76)

Fターム[5F102GV01]に分類される特許

1 - 20 / 76

高周波増幅器

集積型半導体装置

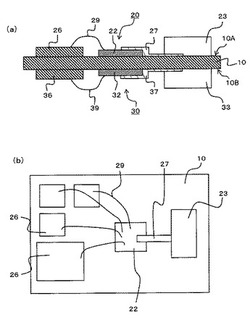

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体素子の構造、半導体抵抗素子の製造方法およびFETスイッチ回路

【課題】薄膜抵抗又は基板抵抗によって数kΩから数十kΩの抵抗値を持つゲート抵抗のサイズが基板長さ、基板幅に比べて大きい。

【解決手段】能動層10を有する半導体基板11と、半導体基板の能動層10にオーミック接触するソース電極13及びドレイン電極14と、能動層10の上方に設けられたゲート電極15と、半導体基板11に設けられた非活性領域16と、非活性領域16上にゲート電極15の一部が引出されて接触する導体17と、非活性領域16上で直流電圧が印加されるパッド電極18と、パッド電極18及び導体17にオーミック接触し、非活性領域16に設けられたゲート抵抗領域19とを備え、ゲート抵抗領域19は半導体基板11へボロンイオンを注入することによって形成され、ボロンイオンの注入量によりゲート抵抗領域19上のシート抵抗値を高めたことを備えたことを特徴とする半導体素子の構造が提供される。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2と各ドレイン電極11の長手方向の長さL1とが同じ長さである。また、ソース電極12の長手方向の端12A,12Bの長手方向の位置は、ドレイン電極11の長手方向の端11A,11Bの長手方向の位置と一致している。ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

半導体装置

【課題】エアブリッジの強度を向上させる。

【解決手段】半導体層上に設けられ、互いに並列に配置された複数のソースフィンガー10と、半導体層上に設けられ、複数のソースフィンガー10と交互に配置された複数のドレインフィンガー12と、半導体層上に設けられ、ソースフィンガー10とドレインフィンガー12との間にそれぞれ配置された複数のゲートフィンガー14と、複数のゲートフィンガー14同士、複数のソースフィンガー10同士、および複数のドレインフィンガー12同士のいずれかを共通に接続するバスラインと、複数のソースフィンガー10、複数のドレインフィンガー12、および複数のゲートフィンガー14のいずれかに設けられ、バスライン上を跨ぐ複数の第1エアブリッジ24と、複数の第1エアブリッジ24同士の間を接続し、半導体層との間に空隙を有する第2エアブリッジ26と、を備える半導体装置。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

半導体装置

【課題】素子温度の上昇を抑制する半導体装置を提供する。

【解決手段】動作周波数fで動作可能な半導体装置であって、熱拡散率Dの基板と、基板上に形成され、ワイドギャップ半導体素子で横型素子の第1のトランジスタで構成される第1の素子ユニット12と、基板上に第1の素子ユニット12に隣接して形成され、第1のトランジスタと異なるタイミングで動作するワイドギャップ半導体素子で横型素子の第2のトランジスタで構成される第2の素子ユニット14とを備え、第1の素子ユニット12の重心と、第2の素子ユニット14の重心との距離が熱拡散長(D/πf)1/2の2倍以下であることを特徴とする半導体装置。

(もっと読む)

電力増幅装置及び連結電力増幅装置

【課題】ソース電極からビアホールまでの距離をさらに短くし、インダクタンスの影響をできる限り低下させる増幅装置を提供する。

【解決手段】電力増幅装置は、接地のためのビアホールと接続する接地部と、接地部を接続するソース電極接地導体と、ソース電極接地導体に連結したソース電極と、ソース電極接地導体に接触しない内側ソース電極と、ドレイン電極と、ゲート電極と、内側ソース電極と接地部とを直接接続する接地ブリッジと、を備える。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

半導体装置及び電源装置

【課題】半導体装置において、抵抗が増大して変換効率が低下してしまうのを防止する。

【解決手段】半導体装置を、基板2上に形成されたGaN系半導体積層構造3を有する第1トランジスタQ1と、GaN系半導体積層構造を有する第2トランジスタQ2とを備え、第1トランジスタが、複数の第1フィンガ8AXを有する第1ゲート電極8Aと、複数の第1ドレイン電極9Aと、複数の第1ソース電極10Aとを備え、第2トランジスタが、複数の第2フィンガ8BXを有する第2ゲート電極8Bと、複数の第2ドレイン電極9Bと、複数の第2ソース電極10Bとを備え、複数の第1ドレイン電極の上方又は下方に接続されたドレインパッド15と、複数の第2ソース電極の上方又は下方に接続されたソースパッド25と、複数の第1ソース電極及び複数の第2ドレイン電極に接続された共通パッド35とを備えるものとする。

(もっと読む)

熱スペーサを有する半導体デバイス

【課題】放熱スペースが短縮された、複数のユニットセルを有する高出力高周波半導体デバイスを提供する

【解決手段】ユニットセルは各々、制御電極24と、第1及び第2の被制御電極20,22とを有する。熱スペーサ(すなわち、電気的に不活性な領域)40が、これらのユニットセルのうち少なくとも1つを第1の活性部分及び第2の活性部分50に分割し、第2の活性部分は、この熱スペーサにより第1の部分から離隔される。ユニットセルの制御電極ならびに第1及び第2の被制御電極は、第1の熱スペーサを横切っている。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。トランジスタ及び配線を覆う形状に加工されたシート、テープ、又は基板を、トランジスタ及び配線を覆って半導体基板の上面上に貼り付ける。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。上面が開口した枠体を、トランジスタの周囲を取り囲んで、半導体基板の上面上に形成する。枠体上にテープを貼り付けることにより、枠体及びテープによってトランジスタ及び配線を覆う。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体を有する半導体装置において、熱による出力低下を低減する。

【解決手段】半導体装置は、基板101上に設けられ、III-V族窒化物半導体からなるバッファ層102と、バッファ層102上に設けられ、III-V族窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられ、III-V族窒化物半導体からなる第2の半導体層104と、基板101の裏面上に設けられ、接地に接続された裏面電極111と、第2の半導体層104上に互いに離間して設けられたソース電極132及びドレイン電極134と、第2の半導体層104上に設けられたゲート電極136とと、第2の半導体層104、第1の半導体層103、及びバッファ層102を貫通し、少なくとも基板101に達し、ソース電極132と裏面電極111とを電気的に接続させるプラグ109とを備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 電力等の信号の合成効率が高く、チップ占有面積を低減可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】 本発明の半導体装置10は、電極パッド11と、複数の信号伝送電極12a、12bおよび12cと、複数の伝送線路13、14および15とを有し、前記電極パッド11と前記各信号伝送電極12a、12bおよび12cとは、前記各伝送線路13、14および15により電気的に接続され、前記複数の伝送線路13、14および15の少なくとも一本は、その線路長が他の伝送線路14以上であり、前記線路長が他の伝送線路以上である伝送線路13および15は、その一部または全部が空中配線され、前記空中配線された伝送線路13aおよび15aが、マイクロストリップラインであることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

1 - 20 / 76

[ Back to top ]