Fターム[5F102HC04]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | デルタドープ、プレーナドープ (52)

Fターム[5F102HC04]に分類される特許

1 - 20 / 52

半導体装置

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

半導体発光素子

【課題】GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成された窒化物系III−V族化合物半導体からなる活性層15とを備え、n型積層構造(11〜14)がSiを5x1017cm-3以上2x1019cm-3以下の濃度で含有し、厚さが0.3nm以上200nm以下のドープ層10と、ドープ層10よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

化合物半導体装置

【課題】プレーナドープの高性能性を保持したまま特性変動を抑制できる化合物半導体装置を提供する。

【解決手段】化合物半導体からなるHEMT構造の化合物半導体装置において、チャネル層へ電子を供給する電子供給層14,16,18が、n型不純物のプレーナドープ層で形成されており、同一の電子供給層におけるプレーナドープ層15,17が2分割以上に分割されている。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】オン抵抗やリーク電流を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板上に、少なくとも、GaAs層、AlGaAs層からなるバッファ層、InGaAs層からなるチャネル層、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層、ノンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層、Se又はTeをドーパントとしたn型不純物を含有するInxGa(1-x)As層(但し0<x<1)からなるコンタクト層を積層したHEMT構造を有するIII−V族化合物半導体エピタキシャルウェハにおいて、その表面清浄度検査におけるHaze値が500ppm以下であるものである。

(もっと読む)

化合物半導体エピタキシャルウェハの製造方法と、トランジスタ用エピタキシャルウェハ

【課題】基板面内のコンタクト抵抗を低く抑えることを可能とした化合物半導体エピタキシャルウェハの製造方法と、トランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板1上に有機金属原料化学気相成長法で化合物半導体層を形成する気相エピタキシャル成長装置10によってn型不純物がドーピングされたn型コンタクト層を成長させる際に、原料ガスが供給される上流側に設けられた第1ヒータ16のヒータ温度を500℃以上とし、第1ヒータ16より下流側に設けられた他のヒータ17,18のヒータ温度を第1ヒータ16のヒータ温度よりも低く、かつ、350℃以上500℃以下に調整する。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】コンタクト層に不純物として供給するTe、Seのメモリーの影響を小さくしつつ、コンタクト抵抗を低減し、かつ、特性変動や信頼性低下を抑制しつつ、電子供給層の不純物濃度を高め、オン抵抗を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板11上に、GaAs層、AlGaAs層からなるバッファ層12a,12b、n型不純物を含有するAlGaAs層13,17又はInGaP層若しくはSiプレナードープ層からなる電子供給層、InxGa(1-x)As層からなるチャネル層15、アンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層18、n型不純物を含有するInxGa(1-x)As層からなるコンタクト層20a、20bを積層したHEMT構造を有し、チャネル層のxを0.3≦x≦0.35とし、コンタクト層のxを0.55≦x≦0.60としたものである。

(もっと読む)

電界効果トランジスタ

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】第1障壁層102に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第1不純物導入領域110と、第2障壁層104に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第2不純物導入領域111とを備える。また、第1不純物導入領域110および第2不純物導入領域111は、チャネル層103の電子に不純物散乱を生じさせない範囲でチャネル層103より離間して形成されている。

(もっと読む)

化合物半導体エピタキシャルウエハ及び高周波半導体装置

【課題】HEMTのチャンネル抵抗を小さくできる構造を有する化合物半導体エピタキシャルウエハ及び高周波半導体装置を提供する。

【解決手段】半絶縁性半導体基板10と、結晶成長性を良好にするためのバッファ層11と、一様にドープされた領域内にデルタドープされた領域を有する第1の電子供給層12と、電子のポテンシャル障壁を形成する第1のスペーサ層13と、2次元電子を発生させるチャネル層14と、電子のポテンシャル障壁を形成する第2のスペーサ層15と、一様にドープされた領域内にデルタドープされた領域を有する第2の電子供給層16と、オーミックコンタクトをとるためのキャップ層17と、を順次積層して形成してなることを特徴とする。

(もっと読む)

トランジスタ素子

【課題】GaAs基板上にHEMT、HBTを順次積層してなるトランジスタ素子において、HEMTの移動度の低下を抑制することが可能なトランジスタ素子を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ(HEMT)3が形成され、HEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子において、HEMT3がアンドープInGaAsPからなるバリア層10を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

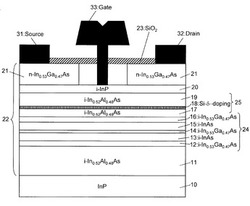

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

半導体基板及び半導体発光素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性が、半導体素子の寸法相当において向上した半導体基板を提供し、更には、この半導体基板を基礎として、特性の高性能化された半導体発光素子、半導体素子を提供する。

【解決手段】基板11と、この基板11上に積層された窒化物系III−V族化合物半導体単結晶層12と、基板11と窒化物系III−V族化合物半導体単結晶層12との間に設けられた、不純物元素を5x1017cm-3以上2x1019cm-3以下含有する層10とを備える。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】精度良く加工された窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101の上に形成された第1の窒化物半導体層107と、第1の窒化物半導体層107の上に形成された欠陥導入層108と、欠陥導入層108の上に接して形成され、欠陥導入層108を露出する開口部を有する第2の窒化物半導体層109とを備えている。欠陥導入層108は、第1の窒化物半導体層107及び第2の窒化物半導体層109と比べて結晶欠陥密度が大きい。

(もっと読む)

電界効果トランジスタ

【課題】p型不純物がドーピングされたバッファ層からの空乏化による影響を低減することで、特性が改善された電界効果トランジスタを提供する。

【解決手段】ダブルヘテロのHEMT構造を有する電界効果トランジスタ10であって、半絶縁性GaAs基板11と、半絶縁性GaAs基板11上に形成され、p型不純物がドーピングされたp型バッファ層101と、p型バッファ層101の上方に形成され、n型不純物がドーピングされた下部キャリア供給層103と、下部キャリア供給層103の上方に形成されたアンドープのチャネル層105と、チャネル層105の上方に形成され、n型不純物がドーピングされた上部キャリア供給層107と、p型バッファ層101と下部キャリア供給層103との間に形成され、n型不純物がドーピングされたn型バッファ層102Bとを備える。

(もっと読む)

化合物半導体装置

【課題】 化合物半導体装置に関し、オン耐圧を高め、また、I−V特性を改善するとともに、保護層を介したリーク電流の発生を抑制する。

【解決手段】 GaNのキャリア走行層と、前記キャリア走行層上に形成されたAlxGa1−xN(0<x≦1)のキャリア供給層と、前記キャリア供給層上に形成され、開口を有する走行キャリアと同導電の第一導電型のGaNのGaN系保護層と、前記開口内に形成されたゲート電極とを設ける。

(もっと読む)

電界効果トランジスタ、および、その製造方法

【課題】従来よりもゲート寸法が縮小され、高周波性能の高い電界効果トランジスタを、均一なゲート寸法でかつ低コストで提供すること。

【解決手段】ゲート電極を形成するための開口部を設ける工程において、投影露光装置を用いて、レジストを露光して前記開口部を作成する際に、露光されるレジストにおいて、該露光により形成される半導体基板上での開口部の幅が、レチクルおよび露光装置の縮小比によって規定されるウエハー上での光束寸法よりも小さな幅として形成されるように、ソース電極およびドレイン電極の厚さを、それぞれ所定の値に設定する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電極の接触抵抗の低減を図るようにした高周波特性の良い電界効果トランジスタ及びその製造方法を提供すること。

【解決手段】III−V族化合物半導体薄膜をエピタキシャル結晶成長させてなる多層膜半導体構造を有しており、多層膜半導体構造は、基板1と、基板1上に形成されたバッファ層2と、バッファ層2上に形成された電子走行層3と、電子走行層3上に形成されたスペーサ層4と、スペーサ層4上に形成された電子供給層5と、電子供給層5上に形成されたバリア層6と、バリア層6上に形成された高電子濃度キャップ層7とを備え、さらに、高電子濃度キャップ層7上に形成されたソース電極101及びドレイン電極103と、バリア層6の表面に形成されたゲート電極102とを備えている。

(もっと読む)

1 - 20 / 52

[ Back to top ]