Fターム[5F102HC16]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エッチング (1,013) | 異方性エッチング、方向性エッチング (113)

Fターム[5F102HC16]に分類される特許

61 - 80 / 113

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】耐圧性が高い電界効果トランジスタおよびその製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成された、リセス部を有する半導体動作層と、前記リセス部を含む前記半導体動作層上に形成された絶縁膜と、前記リセス部における前記絶縁膜上に形成されたゲート電極と、前記半導体動作層上に前記リセス部を挟んで形成され、前記半導体動作層に電気的に接続されたソース電極およびドレイン電極と、を備え、前記リセス部が前記半導体動作層に対して傾斜して立ち上がっている側壁部を有する。

(もっと読む)

化合物半導体装置の製造方法

【課題】本発明は、RFデバイスの特性のばらつきを抑え、高耐圧化、高速化を実現することが可能な化合物半導体装置の製造方法を提供する。

【解決手段】化合物半導体層11の素子領域上に、所定の幅の第1のマスクと、これを所定の間隙で挟むように第2、第3のマスクを形成して異方性エッチングを行い、化合物半導体層中に、凸部を有する所定の深さの第1のリセス14aを形成し、マスクを除去し、露出した化合物半導体層11表面を清浄化し、凸部の上面を露出させた第1のパシベーション膜(18)を形成し、これをマスクとしてエッチングを行い、化合物半導体層11中に所定の深さの第2のリセス14bを形成し、第2のパシベーション膜(18)を形成し、異方性エッチングにより、第2のリセス14bの底面の一部を露出させ壁面にセルフアラインで側壁18aを形成し、露出した第2のリセス底面上にゲート電極17を形成する。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】RFデュアルバンドデバイスとして用いられ、微細化と高性能化をともに実現することが可能な電界効果型トランジスタを提供する。

【解決手段】基板w上に形成され、ソース領域12、ドレイン領域13およびこれらの間に形成されるフィン状領域14を有する化合物半導体層11と、フィン状領域14の第1の側面に形成され、第1の信号が入力される第1のゲート電極16と、フィン状領域14の第2の側面に形成され、第2の信号が入力される第2のゲート電極17を備える。

(もっと読む)

ヘテロ接合電界効果トランジスタの製造方法

【課題】窒化ガリウム系化合物半導体層を備え、ノーマリオフ化したヘテロ接合電界効果トランジスタを簡略に製造する方法を提供することを課題とする。

【解決手段】基板上に半導体層を備え、前記半導体層が基板側から、窒化ガリウム系化合物半導体からなるチャネル層と、障壁層とをこの順で備え、前記半導体層上にソース電極及びドレイン電極と、前記ソース電極と前記ドレイン電極間に位置するゲート電極とを備えたヘテロ接合電界効果トランジスタの製造方法であって、前記半導体層が、フッ素系ガスプラズマによる処理に付されて、ドライエッチングされ、かつフッ素導入され、前記ドライエッチングにより、処理前の半導体層の表面から障壁層の下面までの厚さの10%以上の厚さで半導体層が除去されることを特徴とするヘテロ接合電界効果トランジスタの製造方法により上記課題を解決する。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ動作を実現することができるとともに、所望のゲート閾値電圧を実現することができる、窒化物半導体素子(HEMT)を提供すること。

【解決手段】このHEMTは、真性GaN層3およびn型AlGaN層4が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2は、ストライプ状の線状部10と、島状の合流部11とを備えている。複数本の線状部10は、隣接する線状部10との間に形成されたストライプ状のトレンチ6によって、互いに分離されている。線状部10においてトレンチ6内に露出した積層境界7には、ゲート絶縁膜12を介してゲート電極13が対向している。また、n型AlGaN層4には、ソース側合流部11Sおよびドレイン側合流部11Dにおいて、ソース電極14およびドレイン電極15がそれぞれ接触形成されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】リセスの水平方向寸法の変動を抑え、良好な耐圧安定性を得ることが可能な化合物半導体装置の製造方法を提供する。

【解決手段】化合物半導体基板11上に、第1の開口パターンを有するホトレジスト層17、および第1の開口パターンより広い第2の開口パターンを有し化合物半導体基板11に接する密着層18を形成し、ホトレジスト層17をマスクとし、密着層18の端部を水平方向の終点としてウェットエッチングを行い、リセス13を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】接地インダクタンスを低減化した半導体装置およびその製造方法。

【解決手段】半絶縁性基板11の第1表面に配置され,複数のフィンガーを有するゲート電極、ソース電極およびドレイン電極と、第1表面と反対側の第2表面に配置された接地導体26と、ゲート電極、ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極14、ソース端子電極18およびドレイン端子電極12と、ゲート電極、ソース電極およびドレイン電極の下部の半絶縁性基板11上に形成された動作層と、動作層近傍の小口径VIAホール30と接地導体26近傍の大口径VIAホール20とからなる多段VIAホールと、多段VIAホールの内壁面および第2表面に形成され、ソース端子電極18に対して第2表面側から接続された接地電極23とを備える半導体装置およびその製造方法。

(もっと読む)

リセスゲート型HFETの製造方法

【課題】安定してノーマリオフ特性を有するリセスゲート型HFETを製造することができるリセスゲート型HFETの製造方法を提供する。

【解決手段】基板上にGaN層とAlGaN層とのヘテロ接合部を有し、AlGaN層上にゲート電極が形成されているリセスゲート型HFETを製造する方法であって、基板上にGaN層を形成する第1工程と、GaN層上に第1のAlGaN層を1nm以上3nm以下の厚さに形成する第2工程と、第1のAlGaN層の表面のうちゲート電極形成領域以外の領域の少なくとも一部の表面上に第2のAlGaN層を再成長により形成する第3工程と、第1のAlGaN層の表面のゲート電極形成領域にゲート電極を形成する第4工程と、を含む、リセスゲート型HFETの製造方法である。

(もっと読む)

電界効果型トランジスタ

【課題】ゲート電圧を効率的に印加し、キャパシタンス成分を小さくすることにより、高効率化、高速化を図ることが可能な電界効果型トランジスタを提供する。

【解決手段】基板1上に形成され、ソース領域4、ドレイン領域5およびこれらの間に形成されるフィン状領域6を有する第1の化合物半導体層と、フィン状領域6の表面に、このフィン状領域6をまたぐように形成されたゲート電極7を備える。

(もっと読む)

半導体装置の製造方法

【課題】短ゲート長のゲート電極を有する半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体基板10上にゲート電極14を形成する領域を規定するダミーゲート12を形成する工程と、半導体基板10表面に対して垂直方向の指向性スパッタであるコリメートスパッタ、ロングスロースパッタおよびイオンビームスパッタのいずれかにより半導体基板10上に表面膜16を形成する工程と、ダミーゲート12の側壁に形成された表面膜16を除去する工程と、ダミーゲート12を除去する工程と、半導体基板10上のダミーゲート12を除去した領域にゲート電極14を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

III族窒化物素子のための活性領域成形およびその製造方法

その底部孔口よりも幅が広い最上部孔口を有するゲートウェルを備えるパッシベーション体を含むIII族窒化物ヘテロ接合パワー半導体素子、およびその製造方法。  (もっと読む)

(もっと読む)

横型接合型電界効果トランジスタ

【課題】オフ動作時におけるリーク電流の発生を抑制できる横型接合型電界効果トランジスタを提供する。

【解決手段】p-エピタキシャル層3上に、n型エピタキシャル層4とゲート領域5とが順に形成されている。ゲート電極12aはゲート領域5に電気的に接続され、ソース電極12bおよびドレイン電極12cは、ゲート電極12aを挟むように互いに間隔を置いて配されている。制御電極12dは、オフ動作時においてp-エピタキシャル層3とn型エピタキシャル層4とが逆バイアス状態となるような電圧をp-エピタキシャル層3に印加するためのものである。

(もっと読む)

半導体装置

【課題】ゲートオフ時におけるソース・ドレイン電極間のリーク電流を低く抑制しつつノーマリーオフ型の特性を得ると共に、2次元キャリアガスの濃度とその移動度を高めることのできる半導体装置を提供する。

【解決手段】GaNを含むキャリア走行層と、前記キャリア走行層上に形成され、AlXGa1−XN(0.05≦X≦0.25)を含む第1の層とAlYGa1−YN(0.20≦Y≦0.28、X < Y)を含む第2の層とを積層した障壁層と、前記障壁層上に離間して設けられたソース電極及びドレイン電極と、前記ソース電極と前記ドレイン電極との間で前記障壁層上面から前記キャリア走行層に隣接する前記第1の層に達する溝の底部の上に設けられたゲート電極とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】リセス構造を有する半導体装置における絶縁膜の後退量を制御し、リセスエッジ形状のばらつきを抑え、安定した特性、信頼性を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明の一態様によれば、基板1上に第1の絶縁膜3を形成し、第1の絶縁3膜の所定位置に、この第1の絶縁膜3を貫通する開口部4を形成し、第1の絶縁膜3および開口部4上に第2の絶縁膜5を形成し、異方性エッチングにより、第2の絶縁膜5を選択的に除去して、開口部4壁面に第2の絶縁膜5からなる側壁6を形成し、第1の絶縁膜3および側壁6をマスクとして、等方性エッチングによりリセス7を形成し、側壁6を選択的に除去する。

(もっと読む)

電界効果トランジスタおよびその製造方法

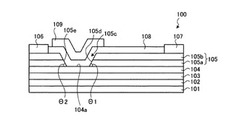

【課題】低いオン抵抗を実現可能な構造を有する、窒化物半導体を用いたエンハンスメント(ノーマリーオフ)型電界効果トランジスタ、とその製造方法の提供。

【解決手段】AlGaN電子供給層104上に、それと同じか、より大きなAl組成のAlGaNからなり、n型不純物が2×1019cm-3以上ドーピングされ、厚さが2〜10nm範囲のコンタクト層105を設け、ソース電極106とドレイン電極107の間の一部でコンタクト層105をエッチング除去して形成する第1のリセス110と、第1のリセス内の一部で電子供給層104を薄くして形成する第2のリセス112とを有し、第2のリセス内をゲート絶縁膜113とT型ゲート電極108で隙間なく埋め込み、T型ゲート電極108の傘の下の絶縁膜109による段差を利用して自己整合的にT型ゲート電極108に隣接してコンタクト層105上にオーミック補助電極114を形成する。

(もっと読む)

半導体素子の製造方法

【課題】電極形成工程を複雑化することなく、BeO膜を除去し優れた接合性を有するp側電極を形成することが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法によれば、AuBe層5を有するp側電極18、18a、18bの表面にオーミック特性付与時の熱により生成されるBeOをエッチングにより除去するため、電極形成工程を複雑化することなく、優れた接合性を有するp側電極18、18a、18bを形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】MIS構造GaN系半導体FETにおいて、リーク電流を抑制すること。

【解決手段】本発明は、基板(10)上に設けられたGaN電子走行層(12)と、電子走行層(12)上に設けられ2次元電子ガス(13)を電子走行層(12)に生成するAlGaN電子供給層(14)と、電子供給層(14)上に設けられた絶縁膜(22)と、絶縁膜(22)上に設けられたゲート電極(34)と、を具備し、ゲート電極(349の中央部下の絶縁膜(22)の膜厚は、ゲート電極(34)の端部(35)下の絶縁膜(24)の膜厚よりも薄い半導体装置である。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】位置合わせの精度に依存しないでゲート電極とトレンチとの間の距離をゼロにすることができ、さらにステッパーの開口能力に依存しないでトレンチの開口幅を狭くすることの可能な電界効果トランジスタの製造方法を提供する。

【解決手段】拡散層17上に絶縁膜18Aと、開口径L1の開口部H1を有するレジスト層R1とを形成したのち(S1,S2)レジスト層R1をマスクとして絶縁膜18Aに開口部を形成する(S3)。レジスト層R1を除去したのち絶縁膜18Aをマスクとして拡散層17の露出部分にゲート領域20Aを形成する(S4)。開口径L2の開口部H2を有するレジスト層R2を形成したのち(S5)リフトオフにより開口部H2の部位にゲート電極21を形成する(S6)。ゲート電極21および絶縁膜18Aをマスクとしてゲート電極21の両脇に一対のトレンチ19を形成する(S7)。

(もっと読む)

窒化物系半導体装置

【課題】閾値電圧を容易に制御することができると共に低いオン抵抗を有する窒化物系半導体装置を歩留まりよく提供する。

【解決手段】ノンドープのAlXGa1-XN(0≦X<1)からなる第1窒化物系半導体層1と、第1窒化物系半導体層よりも格子定数の小さいノンドープまたはn型のAlYGa1-YN(0<Y≦1、X<Y)からなる第2窒化物系半導体層2と、第1窒化物系半導体層と格子定数の等しいノンドープまたはn型の第3窒化物系半導体層3と、InWAlZGa1−W−ZN(0<W≦1、0<Z<1)からなる第4窒化物系半導体層4と、ゲート電極形成領域において前記第3窒化物系半導体層に到達している底面を有するリセス構造30中に形成されたゲート電極5と、ゲート電極を挟んだ第2窒化物系半導体層、第3窒化物系半導体層および第4窒化物系半導体層のいずれかの位置に形成されるソース電極6、ドレイン電極7と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】活性層本体上に均一な膜厚での第1及び第2主電極領域を付加的活性層部分として、突出させて形成するとともに、リーク電流や寄生容量の増加等の問題が防止され、かつ素子分離プロセスを容易に行う。

【解決手段】活性層本体部19a上に形成したマスク層21に第1及び第2開口部23a及び23bとダミー開口部25とを開口する。そして、これら開口部におけるローカルローディング効果を利用して、第1及び第2開口部から露出した第1及び第2主電極領域形成予定領域27a及び27b上のみに、第1及び第2主電極領域31a及び31bを付加的活性層部分として形成する。

(もっと読む)

61 - 80 / 113

[ Back to top ]