Fターム[5F102HC16]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エッチング (1,013) | 異方性エッチング、方向性エッチング (113)

Fターム[5F102HC16]に分類される特許

101 - 113 / 113

半導体装置及びその製造方法

【課題】 短絡不良の発生を抑え、信頼性に優れた半導体装置の構造を提供する。

【解決手段】 トレンチ15に充填する絶縁用酸化膜30を、n+ソース領域12よりも上まで形成し、この絶縁膜30の開口部においてのみ、金属またはシリサイド膜をn+ソース領域12とオーミック接触させソース電極221を形成する。また、ユニットの長手方向におけるソース配線22の端部とソース領域12の端部の距離dをソース配線22の厚さTswの2倍以上とする。

【効果】 ソース/ゲート間の短絡を防止し、歩留り向上によりコストを低減し、冷却系及びシステムサイズを小型化した。

(もっと読む)

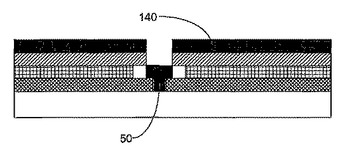

窒化物ベースのトランジスタ及びその製造方法

窒化物ベースのトランジスタ用コンタクト及びそのようなコンタクトの製造方法は、再成長工程によって凹部を提供する。コンタクトは、凹部内に形成される。再成長工程は、III族窒化物半導体材料を含む第1キャップ層を形成する工程を含んでいる。マスクは、第1キャップ層上に形成及びパターン形成される。マスクのパターンは、コンタクト用凹部のパターンに対応する。III族窒化物半導体材料を含む第2キャップ層は、パターン形成されたマスクを使用して、第1キャップ層上に選択的に形成(例えば、成長する)される。追加層は、第2キャップ層上に形成することができる。マスクは除去され、第1キャップ層に対向する凹部(郡)を提供することができ、コンタクト(群)は、凹部(群)内に形成することができる。あるいは、マスクは、上にコンタクトを形成することができ、除去する必要のない導電性材料を含むことができる。  (もっと読む)

(もっと読む)

電界効果トランジスタの製造方法

【課題】 互いに異なるしきい値電圧をもつトランジスタを別途のマスクパターンなしで製造する。

【解決手段】 本発明は、基板上のソース−ドレイン領域にオーミック金属層を形成する段階と、この段階の結果物の全体上部に絶縁膜及び多層の感光膜を形成した後オーミック層以外の一側領域に最下層の感光膜が露出されるようにお互い異なる形態の感光膜パターンを形成すると同時にオーミック金属層以外の他側領域に絶縁膜が露出されるようにお互い異なる形態の感光膜パターンを形成する段階と、感光膜パターンをエッチングマスクとして用いて、露出された絶縁膜及び最下層の感光膜パターンを同時にエッチングして基板及び絶縁膜を露出させる段階と、露出された基板にリセス工程を行った後、露出された絶縁膜をエッチングして基板を露出させる段階と、基板上にお互い異なるエッチング深さを有するゲートリセス領域を形成した後所定のゲート金属を蒸着し感光膜パターンを除去する段階とを含む。

(もっと読む)

窒化物半導体装置の製造方法

【課題】 プレーナー構造で、かつ高抵抗の素子分離が可能な窒化物半導体装置の製造方法を提供する。

【解決手段】 基板上に積層したIII−V族窒化物半導体層からなる窒化物半導体装置の製造方法であって、素子分離領域表面に、鉄、炭素、亜鉛あるいはマグネシウムの少なくとも1つを含む被覆膜を形成した後、加熱処理することによって鉄、炭素、亜鉛あるいはマグネシウムの1つを不純物として窒化物半導体層中に拡散させ、高い絶縁性を有する素子分離領域を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 結晶欠陥が存在する半導体層を備える半導体装置において、低耐圧化の抑制あるいはリーク電流の発生の抑制を実現する。

【解決手段】 電源の一方の極性に接続するドレイン電極22及び半導体基板32と、非被覆領域55を残して半導体基板32の表面を被覆している電流規制層42と、その電流規制層42の表面を被覆している半導体層(ドリフト層56、チャネル層54、ソース層52)と、ソース層52の表面に形成されており、電源の他方の極性に接続するソース電極62を備えている。

(もっと読む)

HEMT装置及び製造方法

【課題】

【解決手段】基板と垂直な縦壁を備えた柱部を有するHEMT型装置。柱部はGaN等の絶縁性半導体材料からなる。柱部の側面上には、柱部の絶縁性材料のそれより大きいバンドギャップを有するAlGaN等の半導体材料からなるバリア層が配置される。電子流は2つの材料の界面の狭いチャネルに制限される。適当なソース、ドレイン及びゲートコンタクトがHEMTの動作のため含まれる。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】 プレーナー構造で、かつ高抵抗の素子分離が可能な窒化物半導体装置及びその製造方法を提供する。

【解決手段】 基板上にIII−V族窒化物半導体層からなる第1の窒化物半導体層と第2の窒化物半導体層とが積層した窒化物半導体装置であって、素子分離領域を、低温で成長させた微結晶構造のIII−V族窒化物半導体層からなる第3の窒化物半導体層で充填する構造とする。素子分離領域に凹部を形成した後、第3の半導体層を選択再成長させることで形成することができる。

(もっと読む)

選択的エッチングした自己整列二重リセス高電子移動度トランジスターの製造方法

選択的エッチングされた自己整合二重リセス高電子移動度トランジスターの製造方法を提供する。この方法は、III−V基板(12);第1の相対的広バンドギャップ層(14,18);チャネル層(20);第2の相対的広バンドギャップショットキー層(22,25);エッチング停止層(26);エッチング停止層上のIII−V第3広バンドギャップ層(28);および第3広バンドギャップ層上のオームコンタクト層(30)を有する、半導体構造体を作製することを含む。  (もっと読む)

(もっと読む)

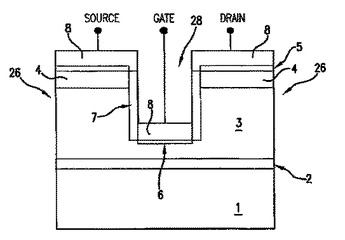

自己整列型炭化ケイ素半導体デバイスおよびそのデバイスの作成方法

電流安定性の改善された自己整列型炭化ケイ素パワーMESFETおよびそのデバイスの作成方法を記載する。このデバイスは、ゲート凹部により分離されたレイズドソースおよびドレイン領域を含み、低ゲートバイアスにおいてでさえ表面トラップ効果が低減されるため、電流安定性が改善される。このデバイスは自己整列型プロセスを用いて作成され得る。このプロセスでは、金属エッチマスクを用いて、nドープのSiCチャネル層上のn+ドープのSiC層を備えた基板がエッチングされてレイズドソースおよびドレイン領域が規定される。この金属エッチマスクがアニールされ、ソースおよびドレイン・オームコンタクトが形成される。単層または多層の誘電性フィルムが成長または堆積され異方性エッチングされる。蒸着または別の異方性堆積技術を用いて、ショットキーコンタクト層および最終金属層が堆積され、オプションとして、誘電性層の等方エッチングされる。  (もっと読む)

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

化合物半導体層の表面処理方法及び半導体装置の製造方法

【課題】窒素を含む化合物半導体層の表面に生じた、エッチングによるダメージを除去あるいは軽減し、ゲート電極に良好なショットキ特性を有する半導体装置を形成する。

【解決手段】ドライエッチングにより、第1化合物半導体層22のゲート電極形成予定領域36の表面を露出するとともに、コンタクト層32を形成する。次いで、この第1化合物半導体層22の露出した表面に対するアニール処理を行う。前述のドライエッチングの際に第1化合物半導体層22の表面に生じたダメージを、窒素プラズマを用いた表面処理を行うことにより、良好な電気特性をもつ第1化合物半導体層22の表面を形成する。この窒素プラズマを用いた表面処理を行った第1化合物半導体層22の表面上にゲート電極38を形成し、良好なショットキ特性を有するゲート電極を具えたリセス型HEMT10を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 能動層に設ける窪みの側壁部分とゲート電極との間に隙間のない埋め込みゲート電極構造を有する半導体装置およびその製造方法を提供すること。

【解決手段】 窪み20をもつ能動層12が形成された半導体基板11と、この半導体基板11の能動層12の上方に設けられたソース電極14およびドレイン電極15と、能動層12の窪み20の部分に埋め込まれたゲート電極21と、ソース電極14およびドレイン電極15間の能動層12上に堆積された絶縁膜17とを具備した半導体装置において、窪み20の幅W1は、絶縁膜17に設けられた開口17aの幅W2よりも小さく形成され、ゲート電極21を構成する金属膜が能動層12に設けた窪み20の部分および絶縁膜17の開口17aの部分に埋め込まれている。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

101 - 113 / 113

[ Back to top ]