Fターム[5F102HC16]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エッチング (1,013) | 異方性エッチング、方向性エッチング (113)

Fターム[5F102HC16]に分類される特許

41 - 60 / 113

窒化物電子デバイスを作製する方法

【課題】ゲートリーク電流を低減できる、窒化物電子デバイスを作製する方法を提供する。

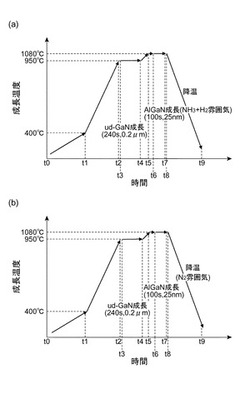

【解決手段】時刻t0で基板生産物を成長炉に配置した後に、摂氏950度まで基板温度を上昇する。基板温度が十分に安定した時刻t3でトリメチルガリウム及びアンモニアを成長炉に供給して、i−GaN膜を成長する。時刻t5で基板温度が摂氏1080度に到達する。基板温度が十分に安定した時刻t6でトリメチルガリウム、トリメチルアルミニウム及びアンモニアを成長炉に供給して、i−AlGaN膜を成長する。時刻t7でトリメチルガリウム及びトリメチルアルミニウムの供給を停止して成膜を停止した後に、速やかに、成長炉へアンモニア及び水素の供給を停止すると共に窒素の供給を開始して、成長炉のチャンバ中においてアンモニア及び水素の雰囲気を窒素の雰囲気に変更する。窒素の雰囲気が形成された後に、時刻t8で基板温度の降下を開始する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】ノーマリオフ特性が安定的に得られる窒化物半導体装置を提供すること。

【解決手段】基板1と、基板1上に形成され、且つ、ヘテロ接合界面22aを有する窒化物半導体層2と、窒化物半導体層2に形成されたリセス3と、を備える窒化物半導体装置であって、

窒化物半導体層2は、基板1上に形成されたAlx1Inx2Ga1−x1−x2N(0≦x1<1、0≦x2≦1、0≦(x1+x2)≦1)からなるキャリア走行層22と、キャリア走行層22上に形成されたAlyGa1−yN(0<y≦1、x1<y)からなる第1の層231、第1の層231上に形成されたGaNからなる第2の層232、及び、第2の層上に形成されたAlzGa1−zN(0<z≦1、x1<z)からなる第3の層233を有するキャリア供給層23と、を備え、

凹部3は、第3の層233を貫通し、凹部底面31において第2の層232の主面が露出するように形成される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

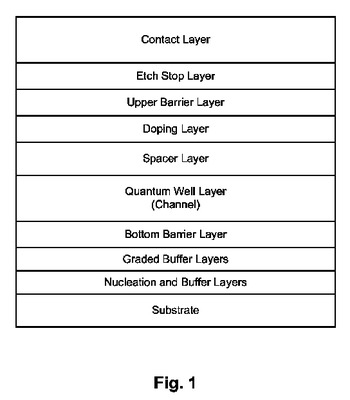

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

打込みされた側壁を有する半導体デバイスを製造する方法およびそれによって製造されたデバイス

半導体デバイスおよびそのデバイスを製造する方法が提供される。デバイスは、接合型電界効果トランジスタ(JFET)、または接合型バリアショットキー(JBS)ダイオードまたはPiNダイオードのようなダイオードであり得る。デバイスは、打込みマスクを用いる選択的イオン注入を使用して製造される。デバイスは、打込みマスクからの通常の入射イオンの散乱によって形成された打込み側壁を有する。長いチャネル長の縦型接合型電界効果トランジスタが記載される。デバイスは、シリコンカーバイド(SiC)のようなワイドバンドギャップ半導体材料から製造されることができ、高温および高出力の用途において使用することができる。 (もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

ゲート電極の形成方法、AlGaN/GaN−HEMTの製造方法及びAlGaN/GaN−HEMT

【課題】リソグラフィ限界以下のゲート長を有するゲート電極の形成方法、及び高周波特性のよいAlGaN/GaN-HEMTの製造方法及びAlGaN/GaN-HEMTを提供する。

【解決手段】基板1表面に第1SiN表面保護層2を成膜する工程と、第1SiN表面保護層表面のレジスト3にリソグラフィ限界のレジスト開口部3aを形成し第1SiN表面保護層をエッチング開口する工程と、第1SiN表面保護層の開口部2a及び第1SiN表面保護層の表面に第2SiN表面保護層4を成膜する工程と、第2SiN表面保護層の表面のレジスト5にリソグラフィ限界のレジスト開口部5aを形成し異方性RIEにて第2SiN表面保護層をエッチングして第2SiN表面保護層の開口部4aと第2SiN表面保護層のサイドウォール4bとを形成する工程と、サイドウォールの内側の基板表面とサイドウォールと第2SiN表面保護層の開口部とを被覆するゲート電極6を形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネルにおけるキャリア移動度が高く、ノーマリオフを実現する半導体装置を提供する。

【解決手段】 n型GaNキャップ層18の開口部28との界面(開口部境界面)は、複数のほぼ鉛直な面S1と、各面S1の間を補完するように形成された傾斜した面S3により構成されている。傾斜面はドライエッチングにより形成し、異方性エッチングによりダメージ層を除去する。縦型FET1では、GaN基板10上に、六方晶のGaN、AlGaNを、{ 0 0 0 1}面を成長面として、エピタキシャル成長させており、n型GaNキャップ層18における鉛直な面S1は、{ 1-1 0 0}面(m面)となる。m面は、C面とは異なり無極性面であるので、m面を成長面として、GaN電子走行層22、AlGaN電子供給層26を再成長させると、ピエゾ電荷等の分極電荷がAlGaN/GaNヘテロ界面に生じない。よって、縦型FET1においては、よりノーマリオフに近づけることが可能となる。

(もっと読む)

窒化物半導体素子、及び窒化物半導体素子を作製する方法

【課題】電流リークパスを低減可能であると共に、ドリフト層におけるオン抵抗を低減可能な窒化物半導体素子を提供する。

【解決手段】窒化物半導体素子11では、半導体積層13の開口部31上に、チャネル層15及びキャリア供給層17が成長される。半導体積層13は、n型ドリフト層23、p型電流ブロック層25及びn型コンタクト層17を含み、これらの半導体層23、25、27は支持基体29の主面29a上に順に設けられる。半導体積層13では(0002)面方向のX線回折半値幅は100秒以下であり、(10−12)面方向のX線回折半値幅は250秒以下である。ゲート電極19は、キャリア供給層17上に設けられる。ゲート電極19は、電流ブロック層25の側面25a上に設けられたチャネル層15における二次元電子ガス35の濃度を変調するように設けられる。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された高抵抗層又は下地層と、前記高抵抗層又は下地層上に形成された、炭素を含有するキャリア濃度制御層と、前記キャリア濃度制御層上に形成されたキャリア走行層と、前記キャリア走行層上に形成された、前記キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層と、前記キャリア供給層から所定の深さに到るまで形成されたリセス部と、前記キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記キャリア供給層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1上に形成されたGaN層2と、GaN層2上に形成されたn型AlGaN層3と、n型AlGaN層3上に形成されたソース電極11s及びドレイン電極11dと、n型AlGaN層3上においてソース電極11s及びドレイン電極11dとの間に位置し、Nを含み、開口部22が形成されたAlN層5と、開口部22内からAlN層5の上方まで延在するゲート電極11gと、が設けられている。更に、開口部22内においてゲート電極11gとAlN層5とを絶縁するSiN膜7が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールドプレートを設けることによって、半導体装置のゲート電極及びドレイン電極間における電解集中を、効率良く緩和する。

【解決手段】下地11と、この下地の下地面11aに、互いに離間しかつ対向して形成された第1及び第2主電極29a及び29bを具えている。また、下地面に、第1及び第2主電極間に挟み込まれて形成されたゲート電極27を具えている。さらに、ゲート電極と第1主電極との間に露出した下地面には、第1下地面保護膜31aが形成されている。また、ゲート電極と第2主電極との間に露出した下地面には、第2下地面保護膜31bが形成されている。そして、ゲート電極の上側表面27aから、このゲート電極の第2主電極と対向する側の側面27b、第2下地面保護膜に渡って、一体的に被覆するフィールドプレート43が形成されている。さらに、フィールドプレートと第2下地面保護膜との境界面47は、下地面側に凸状に湾曲している傾斜面である。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化と信頼性の向上を図ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】化合物半導体基板に形成されたメサ22と、メサ22の壁面に形成された曲率表面を有する側壁16と、メサ22上に形成されるゲート電極と、ゲート電極と一体化され、側壁16の表面に形成されるゲートメタル18と、を備える。

(もっと読む)

電界効果トランジスタ、その製造方法、及び半導体装置

【課題】電圧ストレス前後でのしきい値電圧変動が少ない高信頼性の電界効果トランジスタ、その製造方法、及び半導体装置を提供すること

【解決手段】本発明にかかるJ−FET51は、半絶縁性GaAs基板1上に形成された第1導電型のチャネル層(Siドープn型AlGaAs電子供給層3、7、アンドープAlGaAsスペーサ層4、6、アンドープInGaAsチャネル層5)と、第1導電型のチャネル層上に形成された少なくとも1層以上の半導体層からなる上層半導体層と、上層半導体層に設けられたリセス内、又は上層半導体層の上に形成された第2導電型の半導体層(Cドープp+−GaAs層18)と、第2導電型の半導体層上に接触して設けられたゲート電極19と、上層半導体層の上に接触して設けられた窒化膜16と、窒化膜16上に形成され、窒化膜16よりも膜厚の厚い酸化膜17とを含むゲート絶縁膜と、を備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】ビアホールの形成に関連する歩留まりの低下を抑制し、また、スループットを向上することができる半導体装置の製造方法を提供する。

【解決手段】絶縁性基板1上にGaN層2及びn型AlGaN層3を形成し、その後、ゲート電極4g、ソース電極4s及びドレイン電極4dを形成する。次に、ソース電極4s、GaN層2及びn型AlGaN層3に、少なくとも絶縁性基板1の表面まで到達する開口部6を形成する。次いで、開口部6内にNi層8を形成する。その後、Ni層8をエッチングストッパとするドライエッチングを高速で行うことにより、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを、冷却等によりその側壁に化合物膜19を堆積させながら形成する。そして、ビアホール1s内から絶縁性基板1の裏面にわたってビア配線16を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングで加工したp型の窒化物半導体の表面に低コンタクト抵抗のオーミック電極を形成する。

【解決手段】 半導体装置の製造方法は、窒化物半導体のp型領域をドライエッチングによって露出させる工程と、ドライエッチングで露出させたp型領域の表面にマグネシウムを含む被覆層を形成する被覆層形成工程と、被覆層が形成されている窒化物半導体を加熱処理するアニール工程と、被覆層を形成したp型領域の表面に、オーミック電極を形成する電極形成工程を備える。

(もっと読む)

41 - 60 / 113

[ Back to top ]