Fターム[5F102HC18]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 側壁の形成(被着部を凸部側面に残す) (19)

Fターム[5F102HC18]に分類される特許

1 - 19 / 19

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

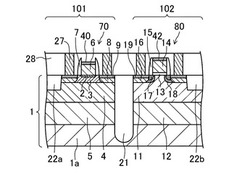

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

半導体装置

【課題】オン抵抗の増加を抑制すると共にリーク電流を低減させることができる半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、ノンドープInGaAs層8と、ノンドープInGaAs層8上に形成された、第1リセス部を備えるSiドープGaAs層1と、ノンドープInGaAs層8とSiドープGaAs層1との間に形成され、第1リセス部内に設けられた第2リセス部を備える、ノンドープオーダ系InGaP層4とその上に形成されるノンドープGaAs層3からなる2層構造半導体層と、第2リセス部内において、ノンドープInGaAs層8上に設けられたCドープGaAs層13と、CドープGaAs層13と、ノンドープGaAs層3及びノンドープオーダ系InGaP層4の界面との間に設けられると共に、ノンドープオーダ系InGaP層4とCドープGaAs層13との間の一部には設けられていない側壁絶縁膜17とを備える。

(もっと読む)

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

ゲート電極の形成方法、AlGaN/GaN−HEMTの製造方法及びAlGaN/GaN−HEMT

【課題】リソグラフィ限界以下のゲート長を有するゲート電極の形成方法、及び高周波特性のよいAlGaN/GaN-HEMTの製造方法及びAlGaN/GaN-HEMTを提供する。

【解決手段】基板1表面に第1SiN表面保護層2を成膜する工程と、第1SiN表面保護層表面のレジスト3にリソグラフィ限界のレジスト開口部3aを形成し第1SiN表面保護層をエッチング開口する工程と、第1SiN表面保護層の開口部2a及び第1SiN表面保護層の表面に第2SiN表面保護層4を成膜する工程と、第2SiN表面保護層の表面のレジスト5にリソグラフィ限界のレジスト開口部5aを形成し異方性RIEにて第2SiN表面保護層をエッチングして第2SiN表面保護層の開口部4aと第2SiN表面保護層のサイドウォール4bとを形成する工程と、サイドウォールの内側の基板表面とサイドウォールと第2SiN表面保護層の開口部とを被覆するゲート電極6を形成する工程とを備える。

(もっと読む)

電界効果トランジスタの製造方法

【課題】ゲート長が短い電界効果トランジスタを低コストで製造できる電界効果トランジスタの製造方法を提供すること。

【解決手段】基板上に、窒化物系化合物半導体からなるチャネル層および該チャネル層上に積層した上部層を含む半導体層を形成する工程と、半導体層の一部領域を少なくとも上部層からチャネル層に到る深さまでエッチングして、該チャネル層の表面の一部を底面部とし、エッチングによって露出した半導体層の側面を側壁部とする段差部を形成する工程と、段差部を含む半導体層の表面を覆うようにマスク層を形成し、該マスク層をエッチバックして該段差部のマスク層を残留させたマスク部を形成する工程と、イオン注入法によって、底面部のマスク部を除く領域にコンタクト領域を形成する工程と、マスク部を除去した後に、少なくとも段差部の底面部と側壁部とを覆うようにゲート絶縁膜およびゲート電極を順次形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】低オン抵抗と高耐圧とを同時に実現させることができる半導体装置を提供すること。

【解決手段】GaNからなる半導体基板12と、この半導体基板12の表面に形成されたn型拡散層11と、このn型拡散層11の表面の一部に形成されたn+型拡散層17と、n型拡散層11上に互いに離間して形成されたドレイン電極13及びソース電極14と、n+型拡散層17上に形成され、ドレイン電極13とソース電極14との間に形成されたゲート電極15と、ゲート電極15とドレイン電極13との間の半導体基板12に、深さ方向に延長形成され、内部が高抵抗体20で充填されたトレンチ19と、を具備する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗低減、ゲート長短縮によるドレインコンダクタンス低下を防止できる半導体装置。

【解決手段】

基板10上に順次配置された窒化物系化合物半導体層からなるバッファ層12,アルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)からなるショットキー層14と、ショットキー層14上に配置されたソース電極16およびドレイン電極18と、ショットキー層14に形成され,チャネルを細線状に分割する複数の溝26と、溝26およびチャネルを横断するゲート電極20とを備え、溝26の側壁部に対してソース電極16との間で、オーミックコンタクトが形成されるため、ソース電極16とショットキー層14との間のコンタクト抵抗が低減でき、ゲート電極20がショットキー層14を囲むように形成され、2DEG層28内のキャリアの閉じ込め効果が高くなるため、ドレインコンダクタンスの低下を防止することができる。

(もっと読む)

電界効果型トランジスタを有する半導体装置

【課題】良好な絶縁性を確保しつつ極めて高い誘電率を有するゲート絶縁膜の機能と、空乏層が形成されることのない金属性のゲート電極の機能とを備え、ゲート電圧のチャネル領域への静電的支配力を可及的に大きくすることのできる半導体装置を提供することを可能にする。

【解決手段】第1導電型の第1半導体層12に離間して設けられた第2導電型の第1ソース領域12aおよび第1ドレイン領域12bと、第1ソース領域と第1ドレイン領域との間の第1半導体層に設けられる第1チャネル領域12cと、第1チャネル領域上に設けられたハーフメタル強磁性金属の第1ゲート電極60と、第1ソース領域に接続するように設けられたハーフメタル強磁性金属の第1ソース電極50aと、を備え、第1ゲート電極の磁化64cの向きが、第1ソース電極の磁化64aの向きと略反平行である。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化と信頼性の向上を図ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】化合物半導体基板に形成されたメサ22と、メサ22の壁面に形成された曲率表面を有する側壁16と、メサ22上に形成されるゲート電極と、ゲート電極と一体化され、側壁16の表面に形成されるゲートメタル18と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧を落とすことなくチャネル抵抗を低減したノーマリオフ型接合FETを提供する。

【解決手段】炭化珪素からなる基板1を用いて形成した接合FETにおいて、チャネル領域(第2エピタキシャル層3)の不純物濃度をドリフト層となる第1エピタキシャル層2の不純物濃度よりも高くする。チャネル領域は、チャネル幅が一定の領域7Aと、その下部でドレイン(基板1)側に行くほどチャネル幅が広くなっていく領域7Bとから形成し、第1エピタキシャル層2とチャネル領域との境界は、ドレイン(基板1)側に行くほどチャネル幅が広くなっていく領域7Bに位置するようにする。

(もっと読む)

III族窒化物素子のための活性領域成形およびその製造方法

その底部孔口よりも幅が広い最上部孔口を有するゲートウェルを備えるパッシベーション体を含むIII族窒化物ヘテロ接合パワー半導体素子、およびその製造方法。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】リセス構造を有する半導体装置における絶縁膜の後退量を制御し、リセスエッジ形状のばらつきを抑え、安定した特性、信頼性を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明の一態様によれば、基板1上に第1の絶縁膜3を形成し、第1の絶縁3膜の所定位置に、この第1の絶縁膜3を貫通する開口部4を形成し、第1の絶縁膜3および開口部4上に第2の絶縁膜5を形成し、異方性エッチングにより、第2の絶縁膜5を選択的に除去して、開口部4壁面に第2の絶縁膜5からなる側壁6を形成し、第1の絶縁膜3および側壁6をマスクとして、等方性エッチングによりリセス7を形成し、側壁6を選択的に除去する。

(もっと読む)

高電子移動度トランジスタ半導体デバイスおよびその製造方法

【課題】サブ・ミリメータ波動作に適した半導体デバイスの生産を可能とする半導体デバイスの形成方法を提供すること。

【解決手段】半導体基板(100)上にフォトレジスト層(102)が堆積され、ウインド(106)がフォトレジスト層(102)内に電子ビーム・リソグラフィによって形成され、共形層(108)がフォトレジスト(102)上、およびウインド(106)内に堆積され、実質的に全ての共形層(108)がフォトレジスト層(102)およびウインドの底部から選択的に除去されて、ウインド(106)内に誘電体側壁(110)を形成する。

(もっと読む)

埋め込みカーボン・ドーパントを用いた半導体デバイス

【課題】 電荷移動度の低下とデバイス性能の低下とをもたらすミスフィット転位の形成を減少させる。

【解決手段】 半導体構造体、及び、半導体デバイス、より具体的にはN型FETデバイスを製造する方法である。本デバイスは、構造体におけるミスフィット転位の発生及び伝播を減少させる層間の界面の材料を介して応力誘発層の上に設けられる応力受容層を含む。応力受容層はシリコン(Si)であり、応力誘発層はシリコン・ゲルマニウム(SiGe)であり、材料は、デバイスを形成する間に両層をドープすることによって与えられるカーボンである。カーボンは、SiGe層全体にわたってドープすることもできる。

(もっと読む)

静電誘導型トランジスタおよびその製造方法

【課題】小コンタクト面積のn+型の低抵抗層への効率よい接触と、ソース、ゲートのコンタクト部のコンタクト抵抗の減少と、リセス部側面の引上配線の断線の補修とが可能な静電誘導型トランジスタの提供。

【解決手段】エピタキシャル成長層にリセス構造を形成し、ゲート電極を形成する工程とエピタキシャル成長層の絶縁膜の開口部にソース電極を形成する工程と半導体基板の反対側にドレイン電極を形成する工程とを含む静電誘導型トランジスタの製造方法において、前記ゲート領域に低抵抗化された多結晶シリコン層を減圧化学気相堆積法で形成する工程とゲート電極形成工程と減圧化学気相堆積法で堆積酸化膜を形成する工程とを介在させた後に、ゲート引出し金属電極を設ける工程を設け、前記ソースの領域に、低抵抗化された多結晶シリコン層を減圧化学気相堆積法で成膜する工程とソース電極形成工程とを介在させた後にソース引出し金属電極を設ける工程を設けた。

(もっと読む)

電界効果トランジスタ及びこの電界効果トランジスタを備えた半導体装置並びに半導体装置の製造方法

【課題】チップサイズの増大を招くことなく、ゲート−ドレイン間寄生容量を低減させる電界効果トランジスタ、及びこの電界効果トランジスタを備えた半導体装置、並びに半導体装置の製造方法を提供する。

【解決手段】半絶縁性基板上にエピタキシャル成長によって形成したチャネル層と、このチャネル層上にエピタキシャル成長によって形成したスペーサー層と、このスペーサー層上にエピタキシャル成長によって形成したドーピング層と、このドーピング層上にエピタキシャル成長によって形成した障壁層とからなる半導体層を有し、かつ、この半導体層の障壁層上に形成したソース電極と、ドレイン電極と、ゲート電極とを有し、ゲート電極の下側の障壁層に不純物をドーピングした埋込みゲート領域を有する電界効果トランジスタにおいて、ゲート電極とドレイン電極との間における障壁層に凹形状のスリットを設ける。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】HEMTを形成した後、半導体基板上に側壁11a,11bを形成する。次に、HEMTを覆って犠牲層15を形成する。次に、犠牲層15内にコンタクトホール16a,16bを形成することにより、ソース電極6a,6bの各上面を露出する。次に、全面的に形成した金属膜をパターニングすることにより、金属配線9を形成する。次に、金属配線9内にスリット12を形成することにより、犠牲層15の上面を部分的に露出する。次に、犠牲層15を溶解した後、溶解された犠牲層15を、スリット12を介して外部に排出する。犠牲層15が除去された結果、空気層10が形成される。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有し、歩留が改善する半導体装置の製造方法を提供すること。

【解決手段】電子供給層13およびキャップ層14を設けた半導体基板10上に第1絶縁膜15を堆積する第1工程と、半導体基板10上にレジスト膜16を形成する第2工程と、レジスト膜16に開口16aを形成する第3工程と、開口16aを通して第1絶縁膜15をエッチングし開口15aを形成する第4工程と、レジスト膜16を剥離する第5工程と、第1絶縁膜15の開口15aを通して、電子供給層13と選択的にキャップ層14をエッチングし開口14aを形成する第6工程と、キャップ層14の開口14aを塞がない膜厚の第2絶縁膜17を堆積する第7工程と、第2絶縁膜17にエッチバック処理を行い電子供給層13を露出させる第8工程と、第2絶縁膜17をマスクにして電子供給層13を所定の深さまでエッチングする第9工程と、電子供給層13上にゲートメタル20を形成する第10工程とからなる。

(もっと読む)

1 - 19 / 19

[ Back to top ]