Fターム[5F102HC29]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 露光 (14)

Fターム[5F102HC29]に分類される特許

1 - 14 / 14

半導体装置の製造方法

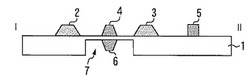

【課題】設計の自由度を損なわずに、高いオン特性とオフ特性を持つ半導体装置を容易に製造する。

【解決手段】可視光に対して透明な半導体基板1の表面にソース電極2及びドレイン電極3を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間に表側ゲート電極4を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間以外の領域に合わせマーク5を形成する。半導体基板1を透過して見える合わせマーク5に基づいて半導体基板1を位置合わせして、半導体基板1の裏面において表側ゲート電極4と対向する位置に裏側ゲート電極6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 ゲート電極からソース及びドレインまでの領域を覆う絶縁膜が、寄生容量増大の要因になっている。

【解決手段】 半導体層を有する基板の上にゲート電極が形成されている。半導体層の上に、ゲート電極から相互に反対側に離れて、ソース電極及びドレイン電極が形成されている。ソース電極とドレイン電極との間の半導体層の上に、ソース電極及びドレイン電極から離れて配置されたゲート横絶縁膜が形成されている。ゲート横絶縁膜には、ゲート電極の下端が充填されたゲート用開口が設けられている。

(もっと読む)

半導体装置の製造方法および半導体基板

【課題】所望のレジストパターンが形成可能な、インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域を有する半導体装置の製造方法を提供する。

【解決手段】インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域と、第1の層および第1の層とは異なる半導体層からなるメサ領域と、を備える半導体基板を用いた半導体装置の製造方法であって、フィールド領域表面に、半導体基板表面から半導体基板上に形成する電子ビーム露光用レジストへのインジウムおよびアルミニウムを含む成分の拡散を抑制する被覆層を形成する工程と、フィールド領域表面に被覆層が形成された半導体基板上に電子ビーム露光用レジストを塗布し、メサ領域の一部に電子ビームを露光し、現像することでメサ領域に開口部を有するレジストパターンを形成する工程と、メサ領域に開口部を有するレジストパターンを用いて半導体基板を修飾する工程とを有する製造方法。

(もっと読む)

ワイドギャップ半導体基板およびワイドギャップ半導体装置の製造方法

【課題】ワイドギャップ半導体基板の位置検出を、可視光を用いて高精度に行う。

【解決手段】一実施形態によれば、ナローギャップ半導体基板(例えばSi基板2)の主面の所定の位置に彫り込み型のアライメントマーク4が形成されたナローギャップ半導体基板のその主面上にワイドギャップ半導体層(例えばGaN層19)をエピタキシャル成長したことにより、基板位置決め用のアライメントマークが予め埋め込まれているワイドギャップ半導体基板を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】2つのオーミック電極、及び、それらの間に配置されたゲート電極を備えた、ゲート電極形成用電子線の揺らぎに起因するゲート電極形成不良が生じない形で製造できる半導体装置を提供する。

【解決手段】半導体装置1の、ゲート電極20により近い方のオーミック電極(ソース電極14s)として、ゲート電極20と対向する側の少なくとも一方の隅(電子線の描画開始位置側の隅)がカットされた矩形形状のものを採用しておく。

(もっと読む)

半導体装置及びその製造方法

【課題】耐湿性(信頼性)及び高周波特性を両立することができる半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性のSiC基板1上に化合物半導体領域2が形成されている。化合物半導体領域2上に、ゲート電極6、ソース電極4及びドレイン電極5が形成されている。シリコン窒化膜10上に、ソース電極4及びドレイン電極5から離れた位置においてゲート電極6を覆う低誘電率膜11が形成されている。低誘電率膜11の上面及び側面を覆うシリコン窒化膜12がシリコン窒化膜10上に形成されている。シリコン窒化膜12上に低誘電率膜13が形成されている。低誘電率膜13の比誘電率は低誘電率膜11のそれよりも高い。また、低誘電率膜13の耐湿性は低誘電率膜11のそれより高い。

(もっと読む)

化合物半導体装置の製造方法

【課題】RFデバイスの耐圧、Po特性などの特性劣化や素子間のばらつきを抑え、良好な高周波特性を実現することが可能な化合物半導体装置の製造方法を提供する。

【解決手段】化合物半導体基板(sub.)またはこの化合物半導体基板(sub.)上に形成された動作層11上に、膜厚tが、

t=n×λ/2(λ:ホトレジスト膜内露光波長、n:整数)

となるホトレジスト膜18を形成し、このホトレジスト膜18の所定領域を、ホトレジスト内露光波長λで露光し、現像して、マスク18’を形成し、このマスク18’を用いて、化合物半導体基板sub.または動作層11をエッチングして、リセス14を形成し、このマスク18’を用いて、リフトオフ法によりリセス14上にゲート電極17を形成する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaN系あるいはGaAs系FET用エピでは、バッファ層耐圧を向上させるために最近ではバッファ層に高抵抗のエピを用いる傾向にある。しかし、微細ゲートのパターニングのための電子ビーム露光によるリソグラフィーの際、チャージアップ現象が生じるという問題がある。

【解決手段】金属配線によって電子が放電する経路を形成する。すなわち、FETを作製するウエハ上の各チップの周辺部のスクライブラインあるいはエッチカットする部分に相当する部分に金属配線を配し、電子線にとってウエハ上で陽極あるいは接地導体となる部分とその金属配線が金属で接続されており、さらにチップ内においてFETのソース電極がチップ周辺の金属配線と金属で接続されるようにした。

(もっと読む)

電界緩和プレートを有する高電子移動度トランジスタ半導体デバイスおよびその製造方法

【課題】 高電界による劣化メカニズムを最小化でき、信頼性のあるマイクロ波およびミリ波周波数動作に適したHEMTデバイスを製造することのできる半導体デバイス製造プロセスを提供する。

【解決手段】 半導体デバイスは、チャネル層及びショットキーコンタクトを形成するため、バリア層上においてドレイン領域とソース領域との間に配設されるTゲートを含む。第1の不活性電界緩和プレートは、Tゲートの一部の上に配設され、第2の活性フィールドプレートは、バリア層上においてTゲートの近傍に配設される。

(もっと読む)

高電子移動度トランジスタのT−ゲート形成方法及びそのゲート構造

【課題】高電子移動度トランジスタのT−ゲート形成方法及びそのゲート構造を提供する。

【解決手段】半導体基板上に互いに異なる電子ビーム感度を有する第1レジスト、第2レジスト及び第3レジストを塗布する第1段階と、電子ビームを用いた第1露光工程を行った後、前記第3レジストを選択的に現像する第2段階と、前記第3レジストが選択現像された幅よりも相対的に広い領域の前記第2レジストを選択現像してゲート頭402領域を画定する第3段階と、前記第3レジスト及び第2レジストがそれぞれ選択現像された半導体基板上に電子ビームを用いた第2露光工程を行った後、前記第1レジストを前記第2段階及び第3段階の現像よりも相対的に低温で選択現像する第4段階と、前記選択現像されたレジストに沿って金属物質を蒸着した後、前記レジストを除去して前記ゲート頭及びゲート脚404を有するT−ゲートを形成する第5段階とを含む。

(もっと読む)

半導体装置の製造方法

【課題】金属残渣とレジスト残渣を生じることを防ぐことができる半導体装置の製造方法を提供する。

【解決手段】レジストパターン19の開口部18に金属を堆積させて電極21を形成する金属堆積工程S28を有する半導体装置の製造方法において、金属堆積工程S28と、リフトオフで電極を構成する金属以外の金属を除去するリフトオフ工程S30の間に、レジストパターン19の開口部18の側壁部19sを除去する側壁部除去工程S29を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、透明基板に遮光性を持たせてウェハ検出を容易にするとともに、微細なリソグラフを可能にする。

【解決手段】 透明基板1或いは透明半導体層2の表面及び裏面の少なくとも一方に、少なくとも一辺の長さが1μm以下の微細加工領域4を除いた領域に可視光を遮光する遮光膜3を設けて、プロセス装置におけるセンサによるウェハ検知が可能になるとともに、露光時に透明基板1の裏面から露光光6の反射が軽減され、開口の広がりを最小限にとどめる。

(もっと読む)

電界効果トランジスタの製造方法

【課題】 互いに異なるしきい値電圧をもつトランジスタを別途のマスクパターンなしで製造する。

【解決手段】 本発明は、基板上のソース−ドレイン領域にオーミック金属層を形成する段階と、この段階の結果物の全体上部に絶縁膜及び多層の感光膜を形成した後オーミック層以外の一側領域に最下層の感光膜が露出されるようにお互い異なる形態の感光膜パターンを形成すると同時にオーミック金属層以外の他側領域に絶縁膜が露出されるようにお互い異なる形態の感光膜パターンを形成する段階と、感光膜パターンをエッチングマスクとして用いて、露出された絶縁膜及び最下層の感光膜パターンを同時にエッチングして基板及び絶縁膜を露出させる段階と、露出された基板にリセス工程を行った後、露出された絶縁膜をエッチングして基板を露出させる段階と、基板上にお互い異なるエッチング深さを有するゲートリセス領域を形成した後所定のゲート金属を蒸着し感光膜パターンを除去する段階とを含む。

(もっと読む)

1 - 14 / 14

[ Back to top ]