Fターム[5F103DD05]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出物質 (905) | 3−5族化合物 (251) | GaAlAs (13)

Fターム[5F103DD05]に分類される特許

1 - 13 / 13

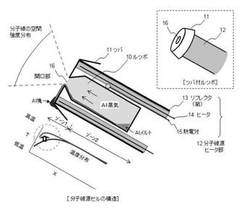

分子線源セル

【課題】分子線源セルを破損させることなく、かつ均一な空間強度分布を維持できるAl用分子線源セルを提供する。

【解決手段】蒸発させる原料を収容するルツボ10と、ルツボ10の側面を囲んで該ルツボ10を加熱する分子線源ヒータ部12と、を備え、ルツボ10は、上端において環状の開口部16が設けられた有底円筒状の容器と、該容器の開口部16の全周に渡って外向きに配置され、分子線源ヒータ部12の外側まで張り出したツバ11と、を有することを特徴とする分子線源セル1。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】 従来の化合物半導体へテロ接合の製造方法では、微小な信号電流を扱う半導体装置において十分な雑音特性を得ることが困難である。

【解決手段】 基板の上に、III−V族化合物半導体である第1の半導体を、第1の基板温度で成長させる。第1の半導体の成長を停止させ、第1の半導体の表面に、V族元素の原料を供給しながら、基板の温度を、第1の基板温度とは異なる第2の基板温度に変化させる。第1の半導体の上に、第1の半導体とは異なるIII−V族化合物半導体である第2の半導体を、第2の基板温度で成長させる。基板の温度を第1の基板温度から第2の基板温度に変化させる工程が、基板の温度を測定する工程と、V族元素の供給量が、測定された前記基板の温度における供給量の目標下限値と目標上限値との間に納まるように、供給量を制御する工程とを含む。

(もっと読む)

半導体量子ドット及び同形成方法

【課題】

巨大アイランドの形成による結晶品質の低下という問題を引き起こすことなく、ナノ構造の品質・形状を高品質に保つことを可能とする半導体量子ドット及び同形成方法を提供すること。

【解決手段】

本願に係る半導体量子ドット形成方法は、自己組織化機構により半導体量子ドットを形成する方法において、量子ドットDの結晶成長レート及び/もしくは埋め込み層L4の結晶成長速度として1ML/s(モノレイヤー・パー・セカンド)以上によって層形成させる。

(もっと読む)

半導体装置及びその製造方法

【課題】

成長中断による、Alを含むIII-V族化合物半導体層への酸素の取り込みを抑制した半導体装置を提供すること。

【解決手段】

Alを構成元素として含む第1のIII-V族化合物半導体によって半導体基板上に形成された第1の半導体層と、厚さが2原子層以上8原子層以下のAlを構成元素として含まない第2のIII-V族化合物半導体で形成され、且つ前記第1の半導体層の上面又は前記第1の半導体層の内部に配置された表面保護層とを有する半導体積層構造と、第3のIII-V族化合物半導体で形成され、且つ前記半導体積層構造の上面に形成された第2の半導体層を具備すること。

(もっと読む)

オプトエレクトロニック半導体素子およびその製造方法

本発明は、分子線エピタキシーによって半導体ヘテロ構造を製造するための方法に関するものであり、以下のステップを有する。それらは、基板を第1の真空チャンバに導入するステップと、基板を第1の温度に加熱するステップと、第1のエピタキシャル層を生成するステップであって、当該層は、III族およびV族典型元素の2元、3元または4元化合物を含む第1の材料を含み、少なくとも1つの分子線から堆積されるステップと、前記基板を第2の温度に冷却するステップであって、III族およびV族典型元素の分子線を遮るステップと、基板を第3の温度に加熱するステップと、第2のエピタキシャル層を生成するステップであって、当該層は、III族およびV族典型元素の2元、3元または4元化合物を含む第2の材料を含み、少なくとも1つの分子線から堆積されるステップとである。さらに、本発明は、ここで述べた方法によって得ることができる半導体素子に関する。  (もっと読む)

(もっと読む)

成膜装置

【課題】半導体基板などを加熱雰囲気中で成膜させる際には、昇温させるだけでも半導体基板には相当の反り(湾曲)が発生する。反りが原因で、基板上に成膜させた膜質の均質性が劣化したり、基板にクラックが発生しやすくなるなどの問題が起こる。

【解決手段】基板の主表面の上側と下側との両方から基板を加熱することにより、主表面の上側と下側との温度勾配(温度差)を小さくし、基板の反りを抑制する。

(もっと読む)

III−V族半導体層を作製する方法、量子井戸構造を作製する方法、及び、窒素源装置

【課題】窒素フラックスの調整が可能な、III−V族半導体層を作製する方法と、量子井戸構造を作製する方法と、窒素源装置とを提供すること。

【解決手段】アパーチャ26a等のうち開口されたアパーチャを介して窒素フラックスを供給し他の原料フラックスを供給して、第1のIII−V族半導体層を基板上に堆積する第1の工程と、開口されるアパーチャの数を変更する第2の工程と、第2の工程後に開口されているアパーチャを介して窒素フラックスを供給し他の原料フラックスを供給して、第2のIII−V族半導体層を第1のIII−V族半導体層上に堆積する第3の工程とを備え、第1のIII−V族半導体層の窒素組成は第2のIII−V族半導体層の窒素組成と異なる。

(もっと読む)

分子線源,分子線結晶成長装置,分子線結晶成長方法

【課題】ポートの数を増やすことなく,還元性ガスを分子線結晶成長装置の成長室内に導入することを可能にする分子線源を提供する。

【解決手段】本発明の分子線源は,結晶成長のための分子線を放出する分子線放出部と,前記分子線放出部に結合され,前記分子線を加熱して分解するクラッキングゾーンとを備え,前記分子線放出部と前記クラッキングゾーンの間に還元性ガスを導入するための還元性ガス導入部を有することを特徴とする。

(もっと読む)

原料物質とターゲットとの間の透視線を除去する坩堝

ターゲット基材上に堆積される物質を加熱するための坩堝は、原料物質を含むように構成されている胴部、胴部の第1の端部に形成された基部、および胴部の第2の端部に形成された放出オリフィスを含む。坩堝は、加熱された原料物質が放出オリフィスを通って通過する前に、中間オリフィスを通過し、そして少なくとも1回坩堝胴部の内側表面に衝突するように、少なくとも配置されかつ構成されている1つの中間オリフィスをさらに含む。  (もっと読む)

(もっと読む)

水素ラジカル発生装置およびそれを備えた分子線エピタキシャル成長装置

【課題】 基板のクリーニング効果、および、結晶成長の高品質化を実現する。

【解決手段】 本発明の分子線エピタキシャル成長装置は、水素ラジカル発生装置10および分子線セル23が、それぞれ独立して設けられている。そして、水素ラジカル発生装置10から水素ラジカルが、分子線セル23から成膜材料の分子線または原子線が、それぞれ別々に、基板処理室20に供給されるようになっている。さらに、水素ラジカルは光励起により発生させる。これにより、水素ラジカルを放出ガスの発生なしに効率的に発生させることができ、基板21のクリーニング効果、および、成膜材料中の不純物を除去する効果を顕著に高めることができる。

(もっと読む)

半導体発光素子、その製造方法およびその半導体発光素子を用いた半導体レーザジャイロ

【課題】 1.1μmよりも短波長な発光波長を有する半導体発光素子を提供する。

【解決手段】 半導体レーザは、活性層6を備える。活性層6は、6個の量子ドット層61と、5個の間隙層62とを含む。6個の量子ドット層61および5個の間隙層62は、交互に積層される。5個の間隙層62の各々は、ノンドープのGaAsからなる。そして、5個の間隙層62の各々は、30〜50nmの膜厚を有する。6個の量子ドット層61の各々は、量子ドット611とキャップ層612とからなる。量子ドット611は、InAsからなり、キャップ層612は、AlyGa1−yAs(y=0.05〜0.5)からなる。量子ドット611は、1.8〜2.4モノレイヤーのInAsをMBEにより結晶成長することにより形成される。

(もっと読む)

半導体層の形成方法

【課題】 表面状態及び電気特性に優れた半導体層を形成することができる半導体層の形成方法を提供する。

【解決手段】 組成比xが0.0942,0.14,0.18,0.30である場合、Alx Ga1-x Asの成長温度を590℃乃至645℃とし、Asの供給圧力を0.5×10-6torr乃至4.0×10-6torrにすることにより、表面状態及び電気特性の双方に優れた膜を形成することができる(領域61)。一方、組成比xが0.5以上である場合、Alx Ga1-x Asの成長温度を645℃乃至720℃とし、Asの供給圧力を3.5×10-6torr乃至6.0×10-6torrにすることにより、表面状態及び電気特性の双方に優れた膜を形成することができる(領域62)。組成比xによって最適な成長温度が相違するのは、AlとGaとの表面拡散距離の相違によるものと推定される。

(もっと読む)

気相成長方法

FeドープInP等の半導体基板上にInAlAs等の化合物半導体からなるエピタキシャル層を再現性よく成長させることのできる気相成長方法を提供する。

半導体基板上にエピタキシャル層を成長させる気相成長方法において、予め室温における半導体基板の抵抗率を測定し、該半導体基板の抵抗率に関わらず実際の基板の表面温度が所望の温度となるように、前記室温における抵抗率に応じて基板の設定温度を制御し、エピタキシャル層を成長させるようにした。

(もっと読む)

1 - 13 / 13

[ Back to top ]