Fターム[5F110AA02]の内容

Fターム[5F110AA02]に分類される特許

401 - 412 / 412

液晶表示装置

【課題】 良好な画像品質を有すると共に、高歩留まりで製造できる液晶表示装置を提供する。

【解決手段】 基板10上に形成されたスイッチトランジスタ(Tr)9a、Tr9aに接続された保持容量13a、Tr9a及び保持容量13a上に形成された絶縁層35、絶縁層35上に形成され、Trの一方の出力端子に接続された画素電極19を有する構成が平面的にマトリクス状に形成された素子基板20aと、素子基板20a上に所定の間隙を有して設けられた共通電極基板22と、素子基板20aと共通電極基板22aとの間に充填された液晶層4と、共通電極基板22a側から読出光を照射したときに、Tr9aに読出光が到達しないように絶縁層中に設けられた遮光層25aと、を備えた液晶表示装置において、保持容量13の一方の電極17aはTr9aの一方の出力端子16aと共通接続され、保持容量13の他方の電極18aは遮光層25aと電気的に接続されている。

(もっと読む)

表示装置および表示装置の製造方法

【課題】駆動側基板上の信号線と対向側基板上の透明電極との間に形成される寄生容量が大きいと、信号線によって伝送される映像信号に波形のなまりや遅延が生じたり、あるいは基板外部から映像信号を供給する駆動ICの負荷が増大したりする。

【解決手段】ガラス基板41(駆動側基板)上の第2のガラス基板(対向側基板)42と対向する領域内に信号線33(33R,33G,33B,33P)を配線する配線構造を採る場合において、ガラス基板41上の酸化膜43に凹部45を形成し、この凹部45内に信号線33を配線することにより、透明電極44と信号線33との間の距離を拡大して透明電極44と信号線33との間に形成される寄生容量を低減する。

(もっと読む)

埋め込み酸化物層の圧縮材料に導入される伸張性のストレインシリコンを備えた半導体デバイス

シリコンゲルマニウム層の形成を必要としないで、高速性のシリコンオンインシュレータ(SOI)とストレインドシリコン技術を備えた半導体デバイスが提供される。圧縮材料(22)層はSOI半導体基板(20)に形成され、上部のシリコン層(21)の歪みをもたらす。圧縮材料層には、酸窒化シリコン、リン、窒化シリコン、及びホウ素/リンドープの石英ガラスが含まれる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 リーク電流を増加させることなく半導体増幅装置の効率を向上させる。

【解決手段】 SOI基板20のドライバ段LDMOSFET形成領域20Aおよび出力段LDMOSFET形成領域20BのそれぞれにLDMOSFETが形成されている。LDMOSFETのソースは、p-型半導体層23および絶縁層22を貫通するn型打抜き層25を介して基板21および裏面電極72に電気的に接続されている。n型打抜き層25とp-型半導体層23およびp型ウエル28とは、PN接合が形成されることによって電気的に分離されている。p型ウエル28に形成されたp+型半導体領域41は、プラグ53cを介してベース電極54cが電気的に接続されている。LDMOSFETのベース電位とソース電位とは独立に制御され、LDMOSFETのオン時にはベース電位をソース電位よりも高くし、オフ時にはベース電位をソース電位と等しくする。

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

低ソース・ドレイン容量用高周波トランジスタ・レイアウト

ゲート電極と櫛形ドレイン及びソース電極を有し、櫛形ドレイン電極の複数の指が櫛形ソース電極の複数の指と互い違いに配置されており、ソース及びドレイン電極が多層(110,120,130,149)を有するRF電界効果型トランジスタ。互い違いの量が各層で異なることにより、多層によりもたらされる低電流密度の効果のすべては失うことなく、最適化、特に、低寄生容量が可能となる。指を短くすることにより、ゲート電極から離間した層において互い違いが低減される。互い違いの低減は、最小容量のために急激な互い違いの低減、最小横方向電流密度のためにより緩やかな互い違いの低減により、最適化される。これが、より高温度又はより高入力バイアス電流においても動作を可能にし、一方、依然として、エレクトロマイグレーションの条件を満たす。  (もっと読む)

(もっと読む)

ソース及びドレインの追加絶縁層を備えた共平面型薄膜トランジスタ

共平面型薄膜トランジスタ、TFT(22)及びその製造方法において、追加の絶縁層がソースコンタクト(30)及びドレインコンタクト(32)上に設けられ、当該追加の絶縁層の第1領域(34)がソースコンタクト(30)と実質的に同一領域を占有し、当該追加の絶縁層の第2領域(36)がドレインコンタクト(32)と実質的に同一領域を占有するように形が定められる。これにより、ゲート(62)−ソース容量、及びゲート(62)−ドレイン容量が低減される。一部の構成では、このことが追加のマスク又は形を定める工程なくして実現され得る。  (もっと読む)

(もっと読む)

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ。

前記電界効果トランジスタは、ゲート絶縁膜(3)によりチャネル(7)から分離されたゲート電極(5)により制御されるチャネル(7)により接続されるソース(10)及びドレイン(11)を含む。前記チャネル(7)はダイアモンド状のカーボン層により形成される。前記トランジスタの製造方法は、続いて、ダイアモンド状のカーボン層を基板上(2)に堆積させ、ゲート絶縁層(3)を堆積させ、そして、少なくとも1つの導電層(4)を堆積させることを含む。前記導電層(4)は前記ゲート電極(5)からエッチングされる。次に、側面の絶縁膜(6)を形成するために、前記ゲート電極(5)の側面に絶縁材料が堆積される。次に、前記ゲート絶縁層(3)がエッチングされ、そして、前記ダイアモンド状のカーボン層がチャネル(7)の輪郭を描くようにエッチングされる。次に、前記ソース(10)を形成するための半導体材料、及び前記ドレイン(11)を形成するための半導体材料がチャネル(7)の両側に堆積される。  (もっと読む)

(もっと読む)

電界効果型トランジスタおよびその製造方法

基体平面から上方に突起した半導体層と、この半導体層を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体層の側面の間に介在するゲート絶縁膜と、前記半導体層上面に設けられ前記ゲート電極下に位置するキャップ絶縁層と、前記半導体層の前記ゲート電極に覆われない領域に形成されたソース/ドレイン領域とを有し、前記キャップ絶縁層は、前記基体平面に平行方向であって一対のソース/ドレイン領域を結ぶチャネル長方向に垂直な方向へ、前記ゲート絶縁膜の表面から張り出した張り出し部を有することを特徴とする電界効果型トランジスタ。 (もっと読む)

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

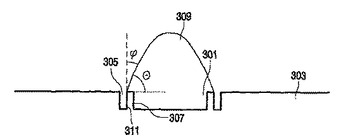

半導体構成用の構造およびその製造方法

本発明は、半導体構成用の構造に関する。半導体を含む溶液の堆積を補助するレジスト構造は、直接、あるいは介在層を介して基板に結合される。このレジスト構造は、半導体を含む溶液(309)を堆積するくぼみ(301)と、くぼみ(309)の縁部の少なくとも一部に整列し、突出部(307)によってくぼみ(309)から分離した溝(305)とを備える。好ましくは、溝(305)は、くぼみ(309)を取り囲む。この溝により、半導体を含む溶液を固定する作用が得られ、それによって濡れ性が改善し、それにしたがって、より大きな体積の半導体を所与の区域に付着させることができる。  (もっと読む)

(もっと読む)

401 - 412 / 412

[ Back to top ]