Fターム[5F110AA07]の内容

Fターム[5F110AA07]に分類される特許

661 - 669 / 669

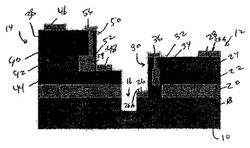

相補的窒化膜トランジスタの垂直およびコモンドレイン

【課題】少ない材料で、電流搬送能力に優れた半導体デバイスを提供する。

【解決手段】 異なる平面に、オーミック接点を含む半導体デバイス、およびそのデバイスを製造するための方法であって、連続したステップで、異なる導電タイプの半導体層の半導体スタックをエッチングし、第1半導体層内に、第1の幅の第1開口部を形成し、別の半導体層を露出させ、次に別の層内に、より狭い幅の第2開口部を形成し、オーミック接点を収容するための別の層の一部を、露出した状態で残すことを含む。

(もっと読む)

歪みFINFETチャネルの製造方法

例示的実施形態はFinFETチャネル構造の形成法に関する。当該方法において、絶縁層(130)上に化合物半導体層(140)を提供し、化合物半導体層(140)上にトレンチ(142)を提供し、かつ、化合物半導体層(140)上およびトレンチ(142)内に歪み半導体層(144)を提供する。該方法において、さらに、化合物半導体層(140)上から歪み半導体層(144)を除去し、その結果、トレンチ(142)内に歪み半導体層(144)を残し、化合物半導体層(140)を除去して、歪み半導体層(144)を残し、かつ、フィン形のチャネル領域(152)を形成する。  (もっと読む)

(もっと読む)

半導体電源スイッチ、および、半導体電源スイッチの製造に適した方法

半導体電源スイッチ(1)が、ソース端子(2)と、ドレイン端子(3)と、それらの間に設けられた半導体構造と、ゲート(5)とを備えている。このゲート(5)は、ソース端子(2)とドレイン端子(3)との間の半導体構造を介して電流の流れを制御するために、用いられる。該半導体構造は、複数のナノワイヤ(4)を備えている。これらのナノワイヤ(4)は、並列に接続されており、各ナノワイヤがソース端子とドレイン端子との間の電気接続を形成するように、配置されている。  (もっと読む)

(もっと読む)

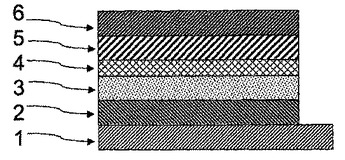

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

1つ以上のトランジスタチャンネルを形成可能な電界効果マイクロエレクトロニクスデバイス

本発明は、電界効果マイクロエレクトロニクスデバイスと、さらにその製造方法に関わる。このデバイスは、基板(700)と、さらに1つ以上のトランジスタチャンネル(transistor channel)を形成することができる少なくとも1つの改善された構造(702)を含む。この構造は、基板上にスタックされた複数のバーによって形成され、電界効果トランジスタの集積化においてスペースを節約することを可能にし、さらにその性能を改善することを可能にする。  (もっと読む)

(もっと読む)

全体的な設計目標を達成すべく、半導体デバイス中のキャリア移動度の可変な半導体デバイス

半導体デバイス(100)は、基板(110)、およびこの基板(110)上に形成される絶縁層(120)とを含む。第1デバイス(710)は第1フィン(130)を含む絶縁層(120)上に形成される。この第1フィン(130)は、絶縁層(120)上に形成され、第1アスペクト比を有する。第2デバイス(720)は、第2フィン(130)を含む絶縁層(120)上に形成される。この第2フィン(130)は、絶縁層(120)上に形成され、第1アスペクト比と異なる第2アスペクト比を有する。  (もっと読む)

(もっと読む)

縦型有機電界効果トランジスタ

共通のソース電極を共有するアクティブセルとキャパシタとを備える縦型有機電界効果トランジスタ。アクティブセルは、ドレイン電極と共通のソース電極との間に挟まれた半導体層を備える。キャパシタは、ゲート電極と共通のソース電極との間に挟まれた誘電体層を備える。共通のソース電極は、ゲート電極に印加される電位を制御することによってソース電極とドレイン電極との間を流れる電流を制御することを可能にする。

(もっと読む)

(もっと読む)

ダブルゲート電界効果トランジスタ装置を製造する方法、及びそのようなダブルゲート電界効果トランジスタ装置

本発明は、ダブルゲート電界効果トランジスタ装置を製造する方法、及び本方法により形成されるような装置を開示する。セミコンダクタ・オン・インシュレータ基板から開始し、第1のゲート、ソース、ドレイン、及びエクステンションを形成し、第2のゲートを形成する。次に、基板が第2の担体に接合され、半導体層の第2のサイドを露出させる。次に、アニーリングステップが、無拡散アニーリングとして実行される。当該無拡散アニーリングステップには、半導体層が、おおむね一様な厚さを有するだけでなく、おおむね平坦な表面を有する、という利点がある。これによって、前記アニーリングステップについて、実現可能な中で最良のアニーリング作用が確保される。ドーパントの非常に高度な活性化によって、エクステンションの非常にシャープな急峻性が達成される。  (もっと読む)

(もっと読む)

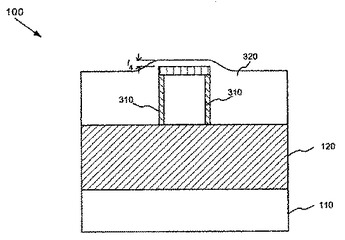

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

661 - 669 / 669

[ Back to top ]