Fターム[5F110EE28]の内容

Fターム[5F110EE28]に分類される特許

101 - 120 / 568

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

半導体装置

【課題】遮光層の端部で回折した光が半導体層に照射されTFT特性の変動を引き起こしているため、この光の照射を防止する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】第3の遮光層108の端部で回折した光117を完全に遮光するため、半導体層103をゲート電極104と第2の遮光部106とで覆うことによって、回折した光の照射を防止し、TFT特性の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

発光装置

【課題】鮮明な多階調カラー表示の可能な発光装置及びそれを具備する電気器具を提供する。

【解決手段】画素104に設けられたEL素子109の発光、非発光を時間で制御する時分割駆動方式により階調表示を行い、電流制御用TFT108の特性バラツキによる影響を防ぐ。また、基板上に形成されるTFT自体も各回路又は素子が必要とする性能に併せて最適な構造のTFTを配置することで、信頼性の高いアクティブマトリクス型発光装置を実現することができる。このようなアクティブマトリクス型発光装置を表示ディスプレイとして具備することで、画像品質が良く、信頼性の高い高性能な電気器具を生産することが可能となる。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

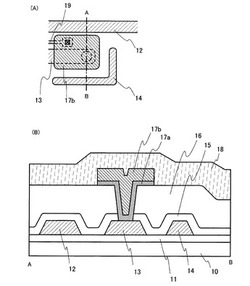

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体表示装置及びその駆動方法

【課題】消費電力の低減を実現することができる、タッチパネルを有する半導体表示装置の提案を課題とする。

【解決手段】画素部、及び、画素部への画像信号の入力を制御する駆動回路が設けられたパネルと、画素部においてパネルと重なる位置に設けられたタッチパネルとを有する。画素部は、入力される画像信号の電圧に従って表示を行う表示素子と、電圧の保持を制御するトランジスタとを有する。トランジスタは、そのチャネル形成領域に酸化物半導体を含んでいる。そして、駆動回路の駆動周波数、すなわち一定期間内における画像信号の書き込み回数を、タッチパネルから入力される操作信号に従って変更する。

(もっと読む)

スイッチング素子、高周波信号スイッチ及び高周波信号増幅モジュール

【課題】高周波信号経路を切り替えるために半導体基板上に形成された、小型でかつ低歪特性を実現するスイッチング素子を提供する。

【解決手段】スイッチング素子の一例であるFET100は半導体基板109上に形成された櫛型の2つのソース・ドレイン電極101と、2つのソース・ドレイン電極101の間を這うように配置された少なくとも2本のゲート電極102と、隣り合うゲート電極102の間に挟まれ、かつ、隣り合うゲート電極102に沿って配置された導電層103とを備え、ゲート電極102の2つのソース・ドレイン電極101の指状部と平行な部分である直線部108の直下に位置する層が、ゲート電極102の隣り合う一対の直線部108をつなぐ部分である屈曲部107の直下に位置する層から、電気的に分離されている。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】液晶表示装置において、製造工程中に残留する導電膜によって画素電極及びデータ配線が互いに短絡されることを防止して画素欠陥を減少させる。

【解決手段】液晶表示装置は、絶縁基板と、絶縁基板の上に位置するゲート線と、ゲート線を覆っているゲート絶縁膜30と、ゲート絶縁膜上に位置し、ドレーン電極とデータ線とを含むデータ配線と、データ配線を覆っている保護膜70と、保護膜の上に位置してデータ配線と電気的に連結されている画素電極80とを含み、ゲート絶縁膜は第1開口部を有し、保護膜は第2開口部と接触口72とを含み、第2開口部は前記第1開口部を露出させ、第1開口部と前記第2開口部は画素の縁領域に位置し、接触口72は前記ドレーン電極の一部分を露出させる。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

半導体装置

【課題】特性が良好であって、かつ大電力用途向けの半導体装置を提供することを課題とする。

【解決手段】半導体装置、具体的には縦型トランジスタのゲート電極層の一部を、ソース電極層、ドレイン電極層およびチャネル領域となる半導体層の一部と重畳する構造にすることである。つまり、ソース電極層と、ソース電極層に接した酸化物半導体層と、酸化物半導体層に接したドレイン電極層と、一部がソース電極層、ドレイン電極層および酸化物半導体層と重畳したゲート電極層と、ゲート電極層の全ての面に接するゲート絶縁層と、を有する半導体装置を提供することである。

(もっと読む)

電気光学装置用基板、電気光学装置、及び電子機器

【課題】十分な容量値を有する蓄積容量を備えることで表示ムラの発生を確実に抑制し得るとともに、消費エネルギーの少ない電気光学装置用基板を提供する。

【解決手段】本発明の電気光学装置用基板30は、第1、第2TFT72,73が、第1導電膜からなるゲート電極74,75と、第1絶縁膜からなるゲート絶縁膜83と、半導体層76と、第2導電膜からなるソース電極77及びドレイン電極79と、を備え、第1蓄積容量71が、前記第2導電膜からなる第1蓄積容量電極80と、少なくとも第1蓄積容量電極80を覆うように形成された第2絶縁膜からなる保護膜85と、保護膜85を間に挟んで少なくとも一部が第1蓄積容量電極80と重なるように形成された画素電極35と、から構成されている。

(もっと読む)

電気光学装置用基板、電気光学装置、及び電子機器

【課題】十分な容量値を有する蓄積容量を備えることで表示ムラの発生を確実に抑制し得るとともに、消費エネルギーの少ない電気光学装置用基板を提供する。

【解決手段】本発明の電気光学装置用基板30は、第1、第2TFT72,73が、第1導電膜からなるゲート電極74,75と、第1絶縁膜からなるゲート絶縁膜83と、半導体層76と、第2導電膜からなるソース電極77、ドレイン電極79と、を備え、蓄積容量71が、前記第2導電膜からなるドレイン電極79と、第2絶縁膜からなる第1保護膜85Aと、第1保護膜85Aを間に挟んでドレイン電極79と重なる第3導電膜からなる蓄積容量上部電極80とから構成され、第1、第2TFT72,73を覆う第2保護膜85B、平坦化膜92が形成され、平坦化膜92上に画素電極35が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明の半導体装置は、良好なカットオフ特性と高速動作とを両立して改善できる。

【解決手段】 本発明の半導体装置は、基板と、基板上に形成され、バンドギャップが生成されたグラフェンを有するチャネル領域と、チャネル領域の両側に形成され、チャネル領域のグラフェンに比して小さいバンドギャップが生成されたグラフェンを有するソース/ドレイン領域と、ソース/ドレイン領域のチャネルに接する部分の上に、夫々形成された第1および第2のゲート電極と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】光劣化が最小限に抑えられ、電気特性が安定したトランジスタを提供することを課題とする。

【解決手段】”safe”トラップが存在するため、光応答の二種類のモードを示す酸化物半導体層を用いることによって、光劣化が最小限に抑えられ、電気特性が安定したトランジスタを実現する。なお、光応答の二種類のモードを示す酸化物半導体層は、10pA以上10nA以下の光電流値を有している。光応答の二種類のモードの存在は、キャリアが”safe”トラップに捉えられるまでの平均時間τ1が十分大きい場合、光電流の時間変化の結果において、急速に立ち下がる部分とゆっくり下がる部分がある。

(もっと読む)

半導体装置の作製方法及び電気光学装置

【課題】TFTに適したSOI基板およびその作製方法を提供する。またSOI基板を用

いて信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】SIMOX、ELTRAN、Smart−Cutに代表される技術を用いて

SOI基板を作製するにあたって、主表面(結晶面)が{110}面である単結晶半導体

基板を用いる。その様なSOI基板は下地となる埋め込み絶縁層と単結晶シリコン層との

密着性が高く、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

101 - 120 / 568

[ Back to top ]