Fターム[5F110EE28]の内容

Fターム[5F110EE28]に分類される特許

61 - 80 / 568

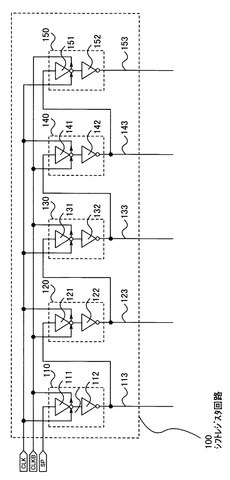

半導体装置

【課題】簡素でかつ占有面積の小さな駆動回路を提供すること。

【解決手段】本発明のシフトレジスタ回路は、複数のレジスタ回路を有している。各レジスタ回路は、クロックドインバータ回路およびインバータ回路を有している。クロックドインバータ回路の出力信号がインバータ回路の入力信号となるよう両者が直列に接続されている。さらに、レジスタ回路は、インバータ回路の出力信号が伝達される信号線を有している。該信号線には接続されている素子が多く寄生容量が大きいため高負荷である。本発明のシフトレジスタ回路は、信号線の寄生容量が大きいために高負荷であることを用いている。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

発光装置およびモジュール

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を作製し、提供することを課題の一とする。

【解決手段】薄膜トランジスタの酸化物半導体層を覆う絶縁層にボロン元素またはアルミ

ニウム元素を含ませる。ボロン元素またはアルミニウム元素を含む絶縁層は、ボロン元素

またはアルミニウム元素を含むシリコンターゲットまたは酸化シリコンターゲットを用い

るスパッタ法により形成する。また、ボロン元素に代えてアンチモン元素(Sb)やリン

元素(P)を含む絶縁層で薄膜トランジスタの酸化物半導体層を覆う構成とする。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

表示装置

【課題】光電変換素子を含む表示装置において、生産性および利便性に優れた表示装置を提供する。

【解決手段】複数の画素がマトリクス状に配列された表示部と、表示部に画像情報を伝送する駆動部と表示部に設けられ、且つレーザ光を検出する受光部と、受光部で検出するレーザ光の位置を解析し、位置に基づいて画像情報を操作し、操作に基づいた画像情報とは異なる画像情報を駆動部に伝送する情報処理部を有し、表示部の複数の画素はそれぞれ薄膜トランジスタを有し、受光部は複数の光電変換素子、走査回路、リセット回路および読み出し回路を有し、薄膜トランジスタおよび複数の光電変換素子は、同一の基板に設けられている表示装置である。

(もっと読む)

表示装置

【課題】本発明は、アクティブマトリクス型表示装置の製造コストを低減するこ

とを課題とし、安価な表示装置を提供することを課題とする。また、本発明の表

示装置を表示部に用いた安価な電子装置を提供することを目的とする。

【解決手段】 アクティブマトリクス型表示装置の製造コストを低減するために

画素部に用いるTFTを全て一導電型TFT(ここではpチャネル型TFTもし

くはnチャネル型TFTのいずれか一方を指す)とし、さらに駆動回路もすべて

画素部と同じ導電型のTFTで形成することを特徴とする。これにより製造工程

を大幅に削減し製造コストを低減することが可能となる。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、高パワーの高周波信号に対する耐圧を維持しながら小型化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、絶縁膜の上の半導体層に設けられたFETを含むスイッチ回路を有する半導体装置であって、前記FETのソース領域とドレイン領域との間に、前記ソース領域から前記ドレイン領域に向かう方向に並んで設けられた第1のゲート電極および第2のゲート電極と、前記第1のゲート電極と前記第2のゲート電極との間の中間領域に電気的に接続された制御端子と、を備える。前記FETは、前記第1のゲート電極および前記第2のゲート電極に供給されるゲート電圧によりON/OFF制御され、前記FETがON状態にある時、前記制御端子をアース電位とし、前記FETがOFF状態にある時、前記制御端子を正電位または負電位とする。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

半導体装置及び表示装置

【課題】複数の有機EL素子への供給電流ばらつきを低減する。

【解決手段】有機EL素子50と電源ラインVLとの間に、電源ラインVLから供給する電流量を制御する素子駆動用TFT20を備え、TFT20のチャネル長方向を、画素の長手方向、又はTFT20を制御するスイッチング用TFT10にデータ信号を供給するデータラインDLの延在方向、又はTFT20の能動層16を多結晶化するためのレーザアニールの走査方向に平行な方向に配置する。さらに電源ラインVLとTFT20の間にTFT20と逆特性の補償用TFT30を備えていても良い。

(もっと読む)

半導体装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する半導体装置を作製す

るための技術を提供する。

【解決手段】分離層を有する固定基板上に樹脂基板を形成する工程と、前記樹脂基板上に

少なくともTFT素子を形成する工程と、前記分離層にレーザー光を照射することにより

、前記分離層の層内または界面において前記固定基板から前記樹脂基板を剥離する工程と

を行い、前記樹脂基板を用いた柔軟性を有する表示装置を作製する。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置

【課題】複数の有機EL素子への供給電流ばらつきを低減する。

【解決手段】有機EL素子50と電源ラインVLとの間に、電源ラインVLから供給する電流量を制御する素子駆動用TFT20を備え、TFT20のチャネル長方向を、画素の長手方向、又はTFT20を制御するスイッチング用TFT10にデータ信号を供給するデータラインDLの延在方向、又はTFT20の能動層16を多結晶化するためのレーザアニールの走査方向に平行な方向に配置する。さらに電源ラインVLとTFT20の間にTFT20と逆特性の補償用TFT30を備えていても良い。

(もっと読む)

表示装置の駆動方法

【課題】酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表示装置の駆動方法を提供する

【解決手段】複数のフレーム期間により画像表示を行う表示装置の駆動方法において、各フレーム期間における複数の走査線のうち、いずれか一の走査線を選択する期間で駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるよう駆動する。そして複数のフレーム期間にわたって、各行を選択していくことで全ての駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるようにしてトランジスタの特性劣化を回復するものである。

(もっと読む)

半導体装置、発光装置、モジュール、及び電子機器

【課題】電気光学装置において、新規の構成を有する画素回路を用いることにより、従来の構成の画素よりも高い開口率を実現することを目的とする。

【解決手段】i行目を除くゲート信号線の電位は、i行目のゲート信号線106が選択されている以外の期間においては定電位となっていることを利用し、i−1行目のゲート信号線111をi行目のゲート信号線106によって制御されるEL素子103への電流供給線として兼用することで配線数を減らし、高開口率を実現する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

61 - 80 / 568

[ Back to top ]